AXI4-Stream Interface

Using SoC Blockset™, you can model a simplified, streaming protocol in your model. Use HDL Coder™ to generate AXI4-Stream interfaces in the IP core.

Simplified Streaming Protocol

When you want to generate an AXI4-Stream interface in your IP core, in your DUT interface, implement the following signals:

Data

Valid

When you map scalar DUT ports to an AXI4-Stream interface, you can optionally model the following signals and map them to the AXI4-Stream interface:

Ready

Other protocol signals, such as:

TSTRBTKEEPTLASTTIDTDESTTUSER

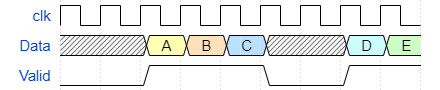

Data and Valid Signals

When the Data signal is valid, the Valid signal is asserted.

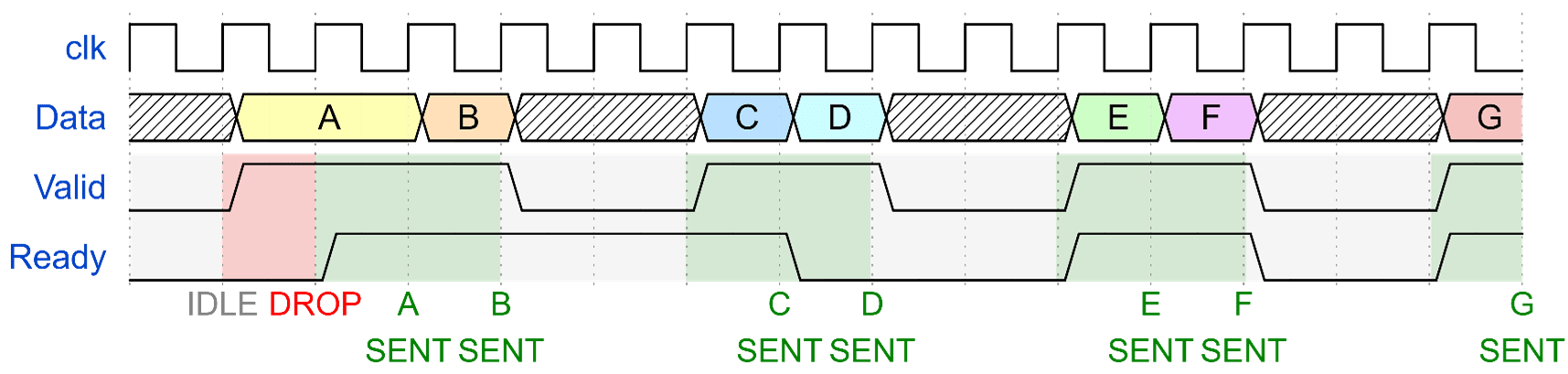

Ready Signal (Optional)

The AXI4-Stream interfaces in your DUT can optionally include a Ready signal. In a Slave interface, the Ready signal enables you to apply back pressure. In a Master interface, the Ready signal enables you to respond to back pressure.

If you model the Ready signal in your AXI4-Stream interfaces, your Master interface ignores the Data and Valid signals one clock cycle after the Ready signal is deasserted. You can start sending Data and Valid signals once the Ready signal is asserted. You can send one more Data and Valid signal after the Ready signal is deasserted.

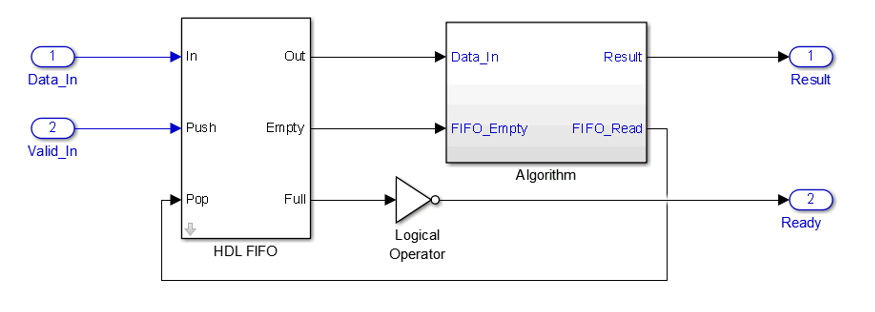

If you do not model the Ready signal, HDL Coder generates the signal and the associated back pressure logic.

For example, if you have a FIFO in your DUT to store a frame of data, to apply back pressure to the upstream component, you can model the Ready signal based on the FIFO Full signal.

TLAST Signal (Optional)

The AXI4-Stream interface on your DUT can optionally model a TLAST signal, which indicates the end of a frame of data. You can use this signal when modeling data packets of different sizes. If you do not model this signal, HDL Coder generates it for you. The autogenerated TLAST signal is asserted when the number of valid samples counts up to the default frame length value.

When the IP core has an AXI4-light Slave interface, the default frame length value is stored in a programmable register in the IP core. You can change the default frame length during run time. When using the autogenerated TLAST signal, if you change the default frame length register in the middle of a frame, the TLAST counter state resets to zero and the TLAST signal is asserted early.

Note

When the Memory simulation parameter is set to

Behavioral mode, the value of the TLAST

signal is ignored.

See Also

Software to AXI4-Stream | AXI4-Stream to Software | SoC Bus Creator