Memory

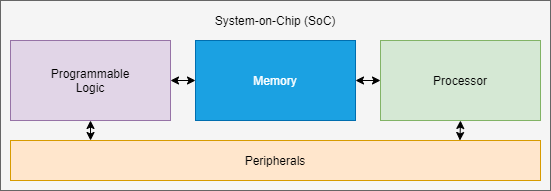

Design and develop the shared memory and data register

components of an SoC application

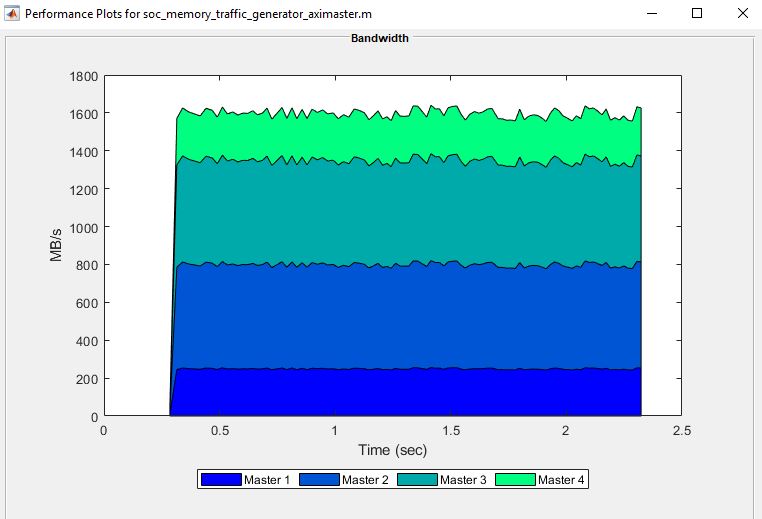

SoC Blockset™ enables simulation and evaluation of shared memory transactions in Simulink®. Visualize post-simulation performance and bandwidth metrics before deploying to SoC device by using the Logic Analyzer app.

Blocks

Apps

| Logic Analyzer | Visualize, measure, and analyze transitions and states over time |

Tools

| Performance Report | Display performance and core usage metrics after model simulation or execution on SoC device (Since R2021b) |

Model Settings

Topics

Design

- Memory and Register Data Transfers

Introduction to memory and register transfers. - External Memory Channel Protocols

Supported memory channel protocols and control signals. - AXI4-Stream Interface

How to design your model for AXI4-Stream vector or scalar interface generation. - Simplified AXI4 Master Interface

Description of AXI4 Master protocol, and how you can design your model for IP core generation with AXI4-Master interfaces. - AXI4-Stream Video Interface

How to design your model for IP core generation with AXI4-stream video interfaces.

Simulation

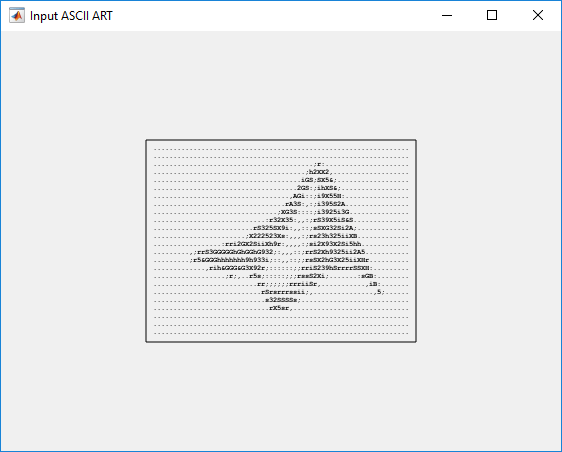

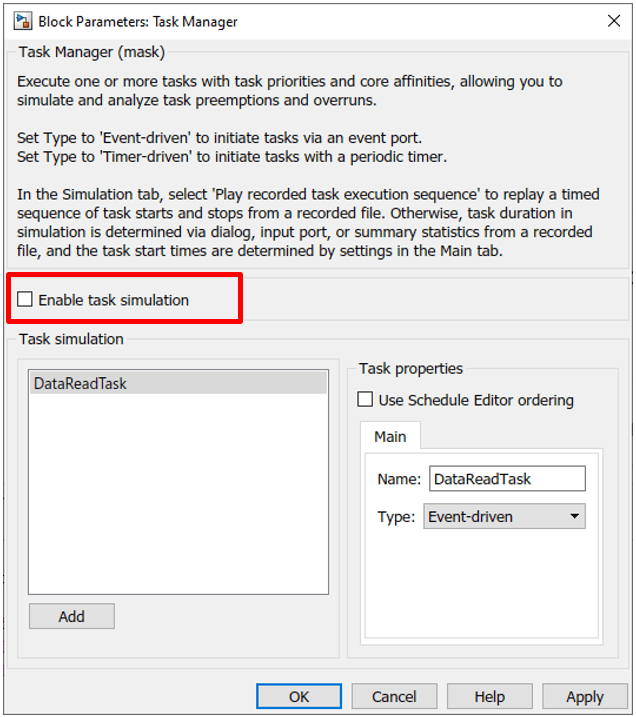

- Simulation Diagnostics

SoC Blockset enables simulation and evaluation of memory transactions in Simulink without the need to deploy a model to an SoC device. - Simulation Performance Tips

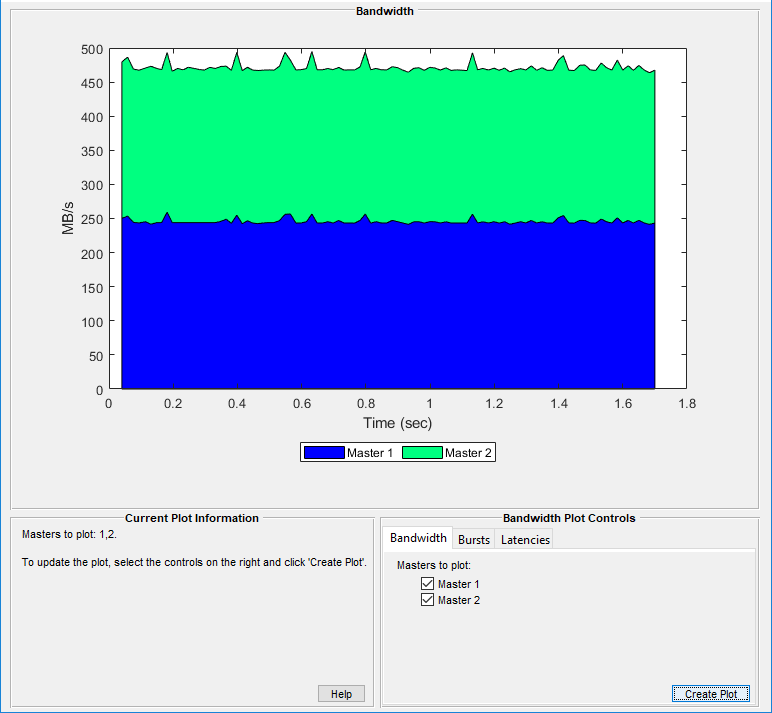

Suggestions for enhancing simulation performance of SoC models. - Simulation Performance Plots

SoC Blockset enables post-simulation analysis of memory diagnostic data.

Measurement

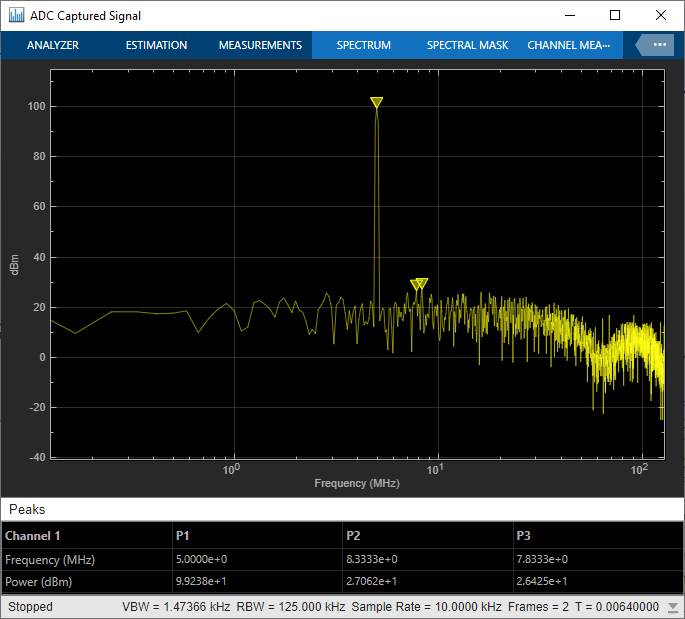

- Memory Performance Information from FPGA Execution

Obtain memory interconnect traffic information from a design running on FPGA.