Interrupt Channel

Send interrupt to processor from hardware

Libraries:

SoC Blockset /

Memory

Description

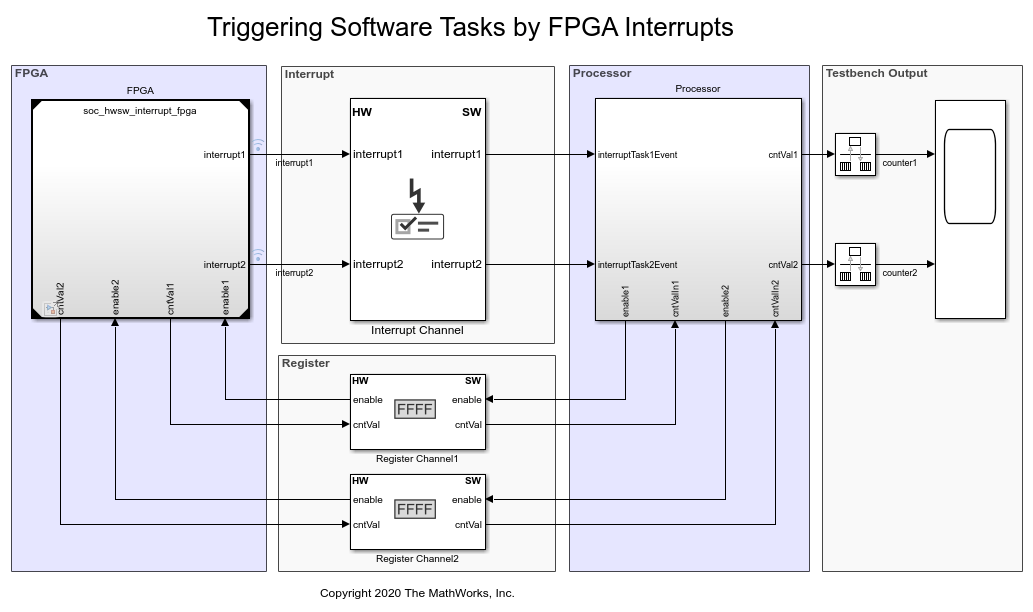

The Interrupt Channel block receives interrupt requests from FPGA logic or the Memory Channel block, arbitrates the requests, and triggers an event-driven software task to the Task Manager block. You can connect up to 16 devices to the interrupt controller, with one interrupt per device. The block consists of these three parts:

Interrupt Controller – This part accepts interrupt requests (IRQs) and arbitrates them according to a user-specified priority. When concurrent requests to the interrupt controller exist, requests with a higher priority are processed before those with a lower priority.

Kernel Interrupt Service Routine (ISR) – This part receives an interrupt request from the Interrupt Controller, serves the interrupt, and sends an acknowledge signal back to the Interrupt Controller, so that it can process the next IRQ.

IPCore Driver (one per interrupt) – This part receives a request from the Kernel ISR and triggers an event-driven task in the processor.

Even though the interrupt channel can have more than one interrupt output toward the processor, it sends no more than one active interrupt event to the processor at any given time.

This image shows a conceptual view of an Interrupt Channel block, that accepts interrupt requests from an FPGA algorithm. After arbitration, the kernel serves the request and triggers an event to a processor algorithm.

Examples

Ports

Input

Output

Parameters

Extended Capabilities

Version History

Introduced in R2020b