Full Duplex Data Streaming between Software and Hardware on Versal Platform

This example shows how to design a system for full duplex data streaming between hardware and software and implement it on a Xilinx® Versal® AI Core Series VCK190 Evaluation Kit using SoC Blockset™ software. In this example, you generate the HDL code for the algorithm as an IP core, integrate it in a reference design to build a system, and deploy the system to hardware.

This example supports the Xilinx Versal AI Core Series VCK190 Evaluation Kit.

Design Hardware Algorithm

Use the Support for Fixed Reference Design workflow to design an algorithm and integrate it into a predefined reference design that defines the architecture. You can use this workflow for rapid prototyping when you have a reference design that meets your system requirements and is available for deployment.

In this example, soc_swhwsw_stream_top model receives a stream of ramp signal samples from the processor. The model then sends that stream with the error and status signals to the processor to verify and display the received ramp signal.

To design the hardware algorithm, you must choose the reference design that meets your requirements by using the SoC Model Creator tool. Open the tool by entering this command at the MATLAB® command prompt.

socModelCreator

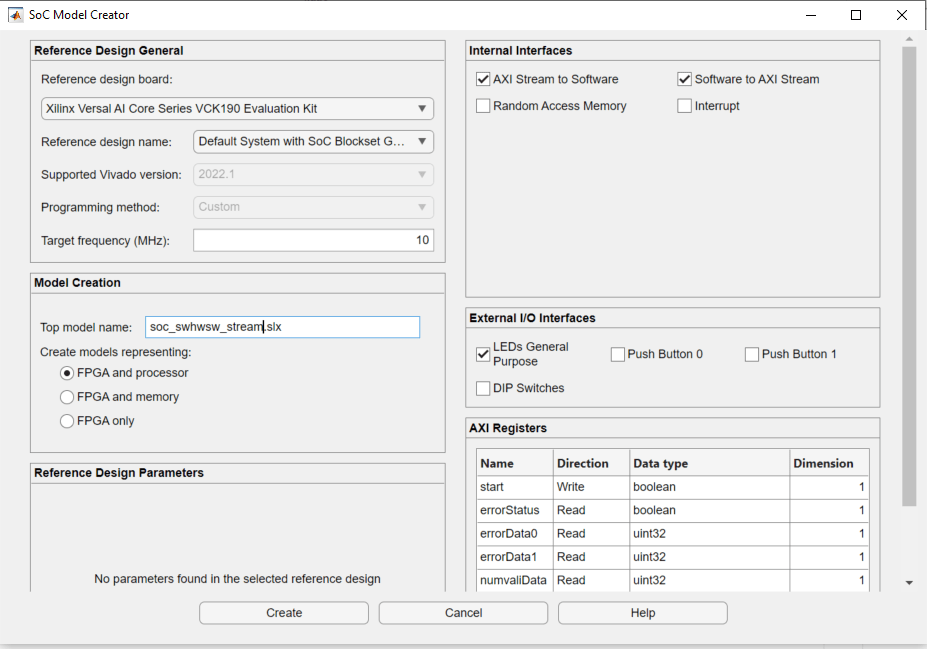

To create the model, follow these steps in the SoC Model Creator tool.

Set Reference design board to

Xilinx Versal AI Core Series VCK190 Evaluation Kit.Set Reference design name to

Default System with SoC Blockset Generic Design.Set Top model name to

soc_swhwsw_stream.Specify the model type as FPGA and processor.

Select the

AXI Stream to SoftwareandSoftware to AXI Streaminterfaces in the Internal Interfaces pane.Select

LEDs General Purposein the External I/O Interfaces pane.Add the required registers in the AXI Registers pane.

Click Create.

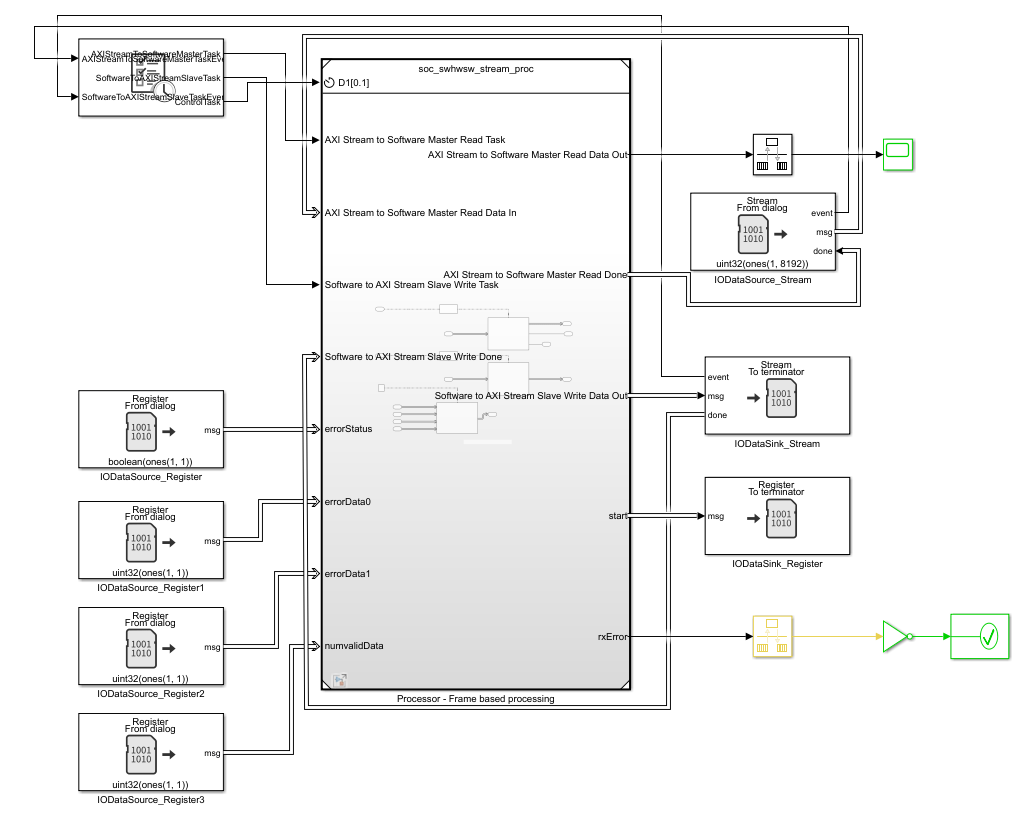

The tool generates the soc_swhwsw_stream top model, the soc_swhwsw_stream_fpga FPGA model, and the soc_swhwsw_stream_proc processor model. The subsystem in the FPGA model is preconfigured with ports to match your chosen reference design. The processor model is preconfigured with the Stream Write and Stream Read blocks according to the internal interfaces you define in the SoC Model Creator. Add your hardware algorithm inside the HDL_IP subsystem and add stimuli and scopes in the top model for simulating your algorithm.

The soc_swhwsw_stream_fpga model is the hardware generation model. This model adds the algorithm that reads a stream of samples from the processor and sends them back to the processor as a stream of samples along with error and status signals to the processor as registers.

The soc_swhwsw_stream_proc model is the processor model that sends the ramp data from the counter to the Stream Write block. The Stream Write block sends the ramp signal data to the FPGA. The Stream Read block receives the looped back ramp signal samples from the FPGA and sends them to the verify Rx data subsystem to display the received ramp signal and returns an error if it receives an incorrect signal.

open_system('soc_swhwsw_stream_top')

close_system('soc_swhwsw_stream_top')

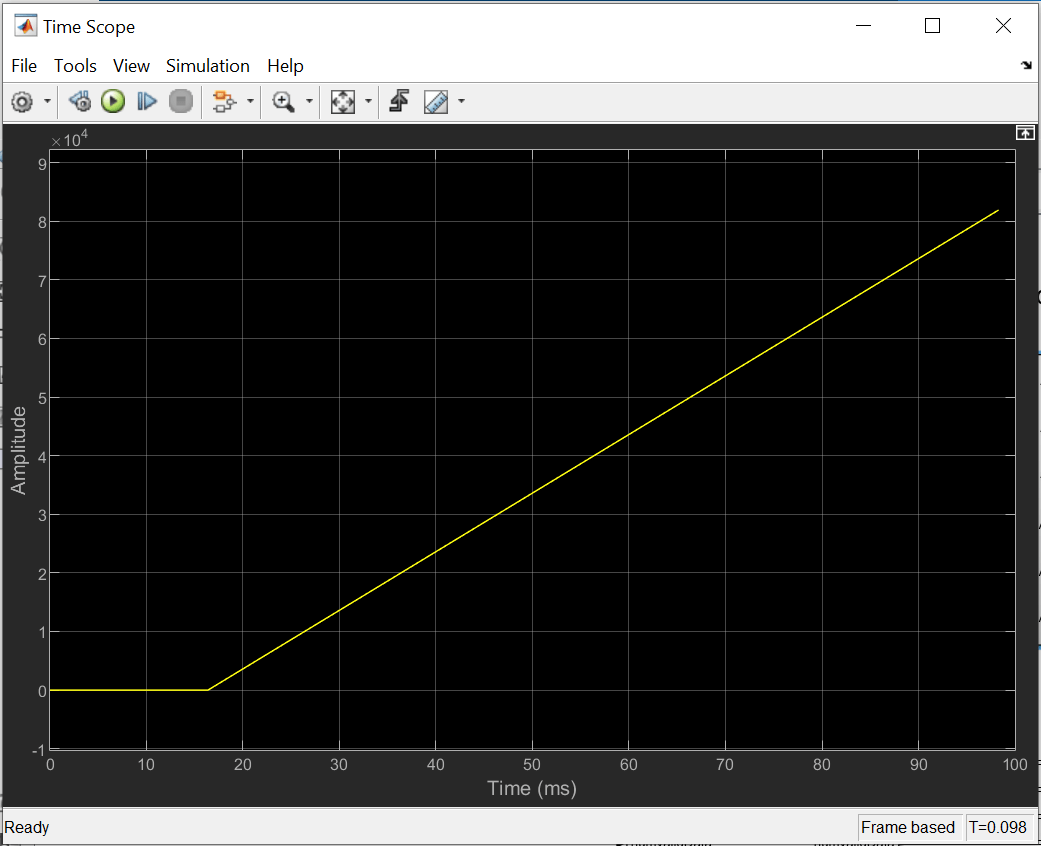

Simulate

Simulate the model and observe the ramp signal in the scope. If receive error occurs, the simulation stops and the software displays the assertion message Receive ramp verification check failed.

Implement and Run Model on Hardware

Specify the DUT subsystem of the FPGA model as an atomic subsystem. Right-click the HDL_IP subsystem, and then click the Block Parameters button. In the Block Parameters window, select Treat as atomic unit.

Set up the Vivado® tool version by entering this command at the MATLAB command prompt. To run this command, you must have the required Xilinx Vivado version installed.

hdlsetuptoolpath('ToolName','Xilinx Vivado', ... 'ToolPath','C:\Xilinx\Vivado\2022.1\bin\vivado.bat');

To implement the model on a supported SoC board, use the SoC Builder tool. Before you use this tool, set the Hardware Board to Xilinx Versal AI Core Series VCK190 Evaluation Kit on the System on Chip tab of the Simulink toolstrip.

To open SoC Builder, click Configure, Build, & Deploy. After the SoC Builder tool opens, follow these steps.

Select Build using fixed reference design on the Setup screen. Click Next.

Select Build in external mode on the Select Build Action screen. Click Next.

Specify the project folder on the Select Project Folder screen. Click Next.

View the memory map by clicking View/Edit on the Review Hardware Mapping screen. Click Next.

Check the compatibility of the model for implementation by clicking Validate on the Validate Model screen. Click Next.

Build the model by clicking Build on the Build Model screen. The tool generates the software model and saves it in the current project folder. An external shell opens when FPGA synthesis begins. The Build step integrates the newly generated IP core into the Versal IP core reference design and generates the corresponding embedded system with a bitstream.

After bitstream generation finishes in the external shell, Click Next.

Test the connectivity of the host computer with the SoC board by clicking Test Connection on the Connect Hardware screen. Click Next to go to the Load Bitstream screen.

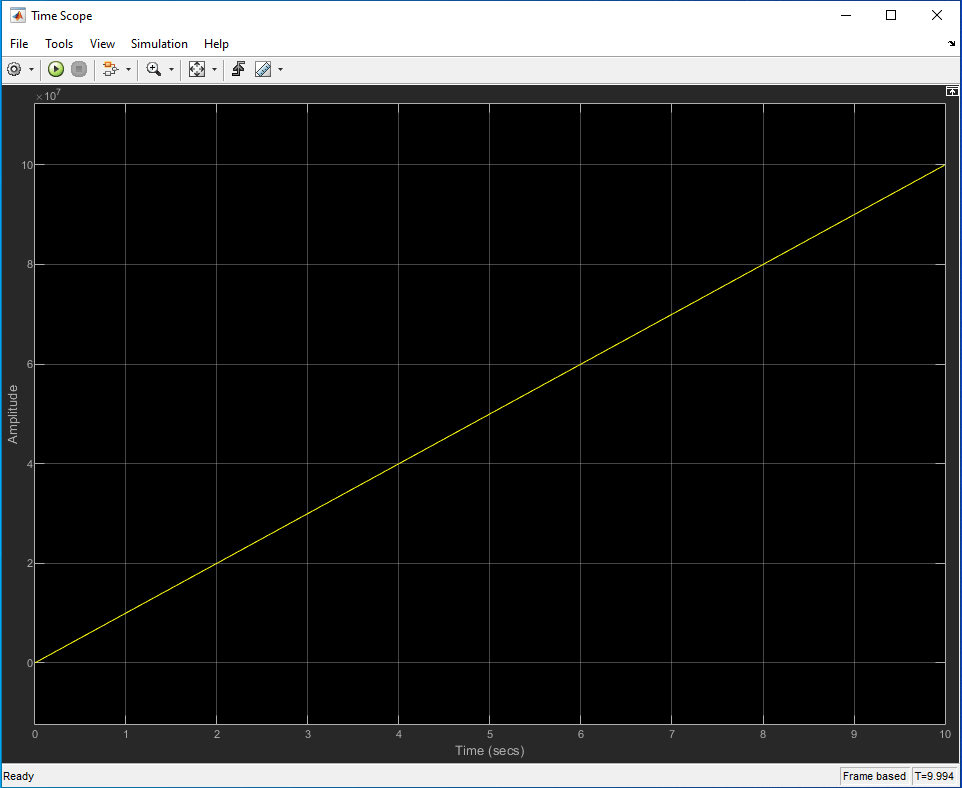

Click Load to program the hardware. Once programming finishes, open the generated software model in external mode.

Run the software model in external mode. When the software model runs on hardware, you can observe the ramp signal in the scope. If receive error occurs, the simulation stops and the software displays the assertion message Receive ramp verification check failed.

Conclusion

Using the fixed reference design workflow, you implement an algorithm that receives a stream of samples from a processor. The processor sends this stream with the error and status signals to the processor for verification. You verify that the system runs on the hardware according to your specifications. You can use this example as a reference and prototype for your algorithms on the Xilinx Versal AI Core Series VCK190 Evaluation Kit.

See Also

SoC Model Creator | SoC Builder