Support for Fixed Reference Design

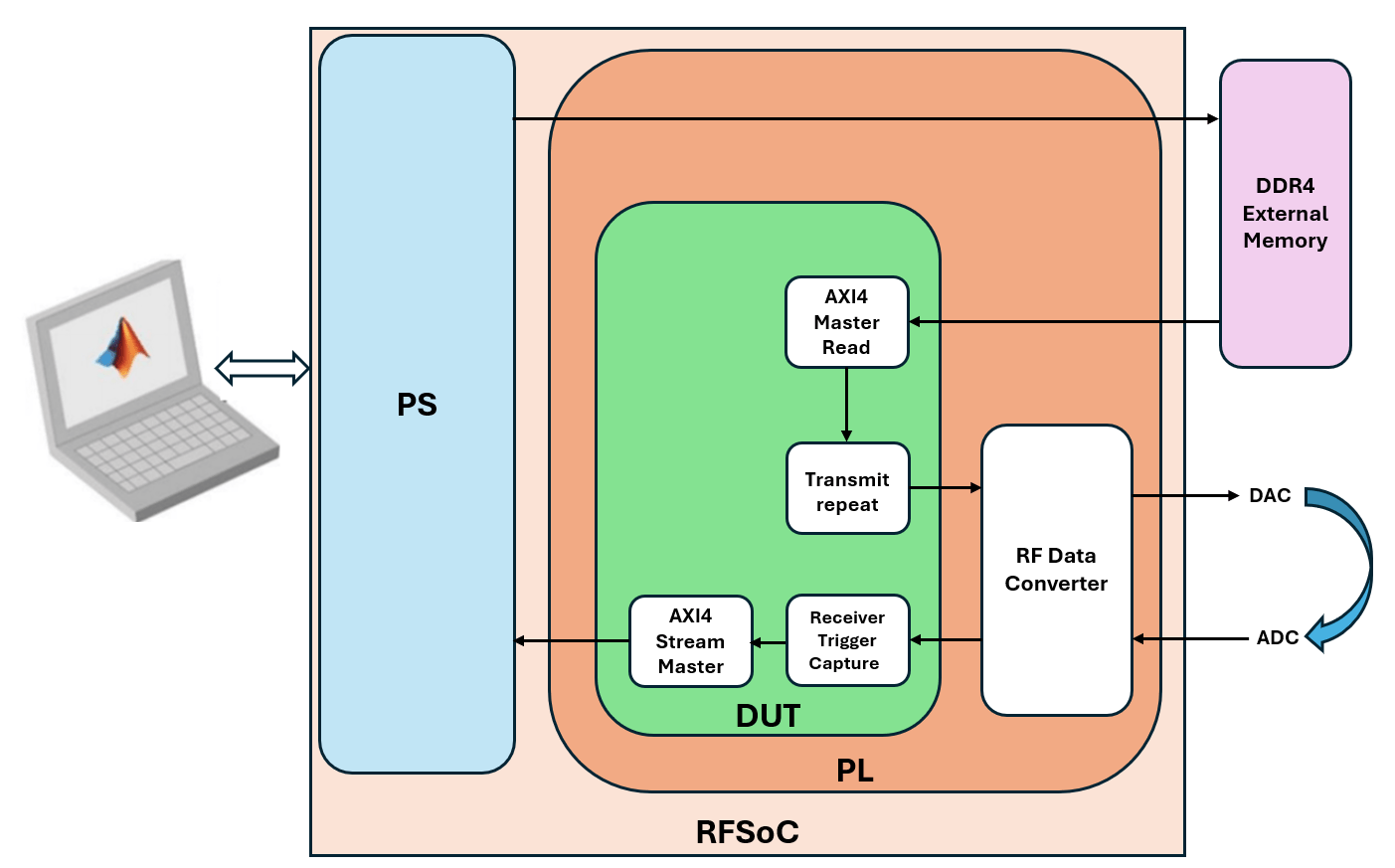

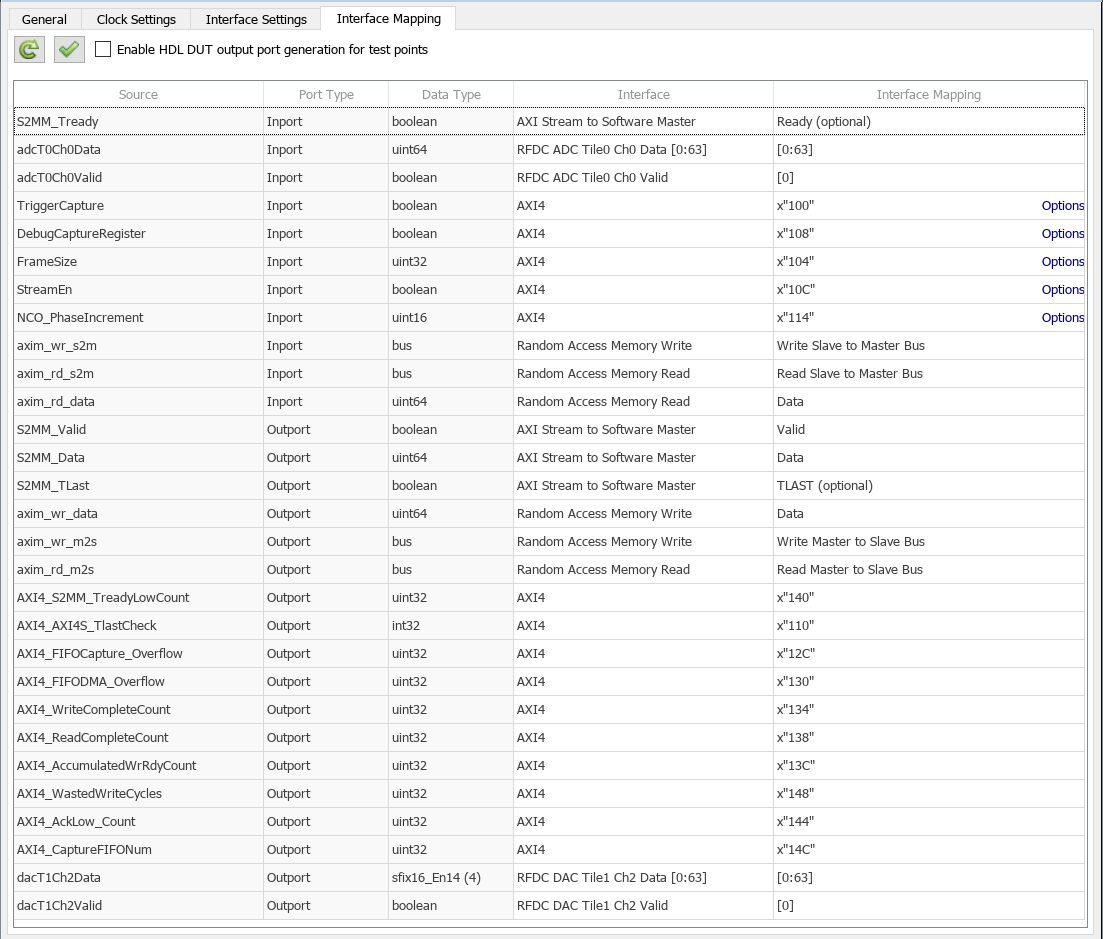

This workflow enables algorithm and system designers to generate an HDL IP core and integrate it into a fixed reference design for rapid prototyping. Create an SoC model based on the selected reference design for the supported AMD® MPSoC, RFSoC, and Versal adaptive SoC devices by using the SoC Model Creator tool. Use the created model as a template to design and simulate your FPGA algorithm and processor algorithm. Then, generate a bitstream and host I/O model, build a software application, and program the board by using the SoC Builder tool.

Topics

- Configure Design Using SoC Model Creator

Customize and design an SoC model by using the SoC Model Creator tool.

- Generate Design Using SoC Builder

Generate an SoC design and run it on the target hardware board using the SoC Builder tool.

- SoC Generation Workflows

Choose between SoC Builder workflow or IP Core Generation workflow for deploying your design on an SoC device.

- Reference Design for Zynq-7000 and MPSoC Devices

Learn about how to use Default System with SoC Blockset reference design and its requirements.

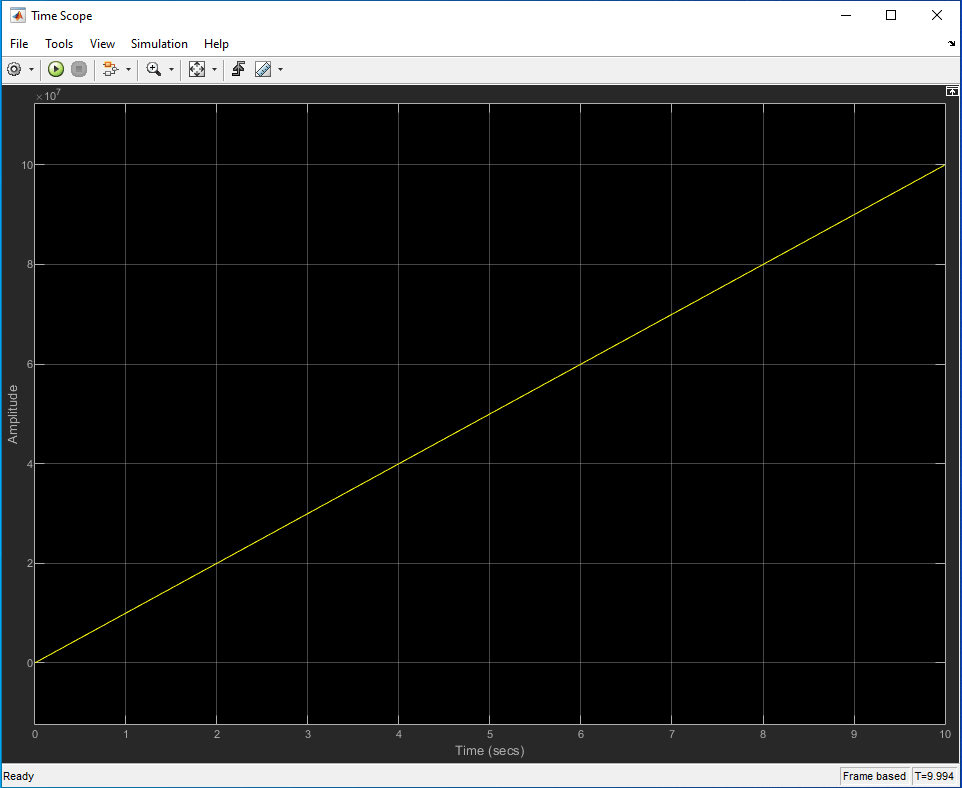

- Reference Designs for RFSoC Devices

Learn about how to use RFSoC reference designs and their requirements.

Tools

| SoC Model Creator | Create SoC model based on selected reference design (Since R2021b) |

Objects

soc.RFDataConverter | Configure the RF Data Converter on the RFSoC device from MATLAB |