Hardware I/O Devices

Model the connection between the IO devices on your board and your FPGA

logic

Use these blocks to create models that simulate the connection between your SoC design and these IO devices.

Blocks

| AD936x Receiver | Receive data from AD936x-based Zynq radio hardware (Since R2024b) |

| AD936x Transmitter | Send data to AD936x-based Zynq radio hardware (Since R2024b) |

| AD936x Data Read | Read data from AD936x-based Zynq radio hardware (Since R2024b) |

| AD936x Data Write | Write data to AD936x-based Zynq radio hardware (Since R2024b) |

| HDMI Rx | Convert video stream to YCbCr 4:2:2 pixel stream |

| HDMI Tx | Convert YCbCr 4:2:2 pixel stream to video frame |

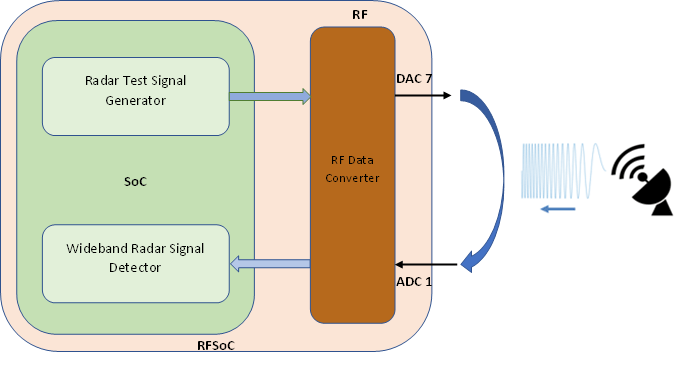

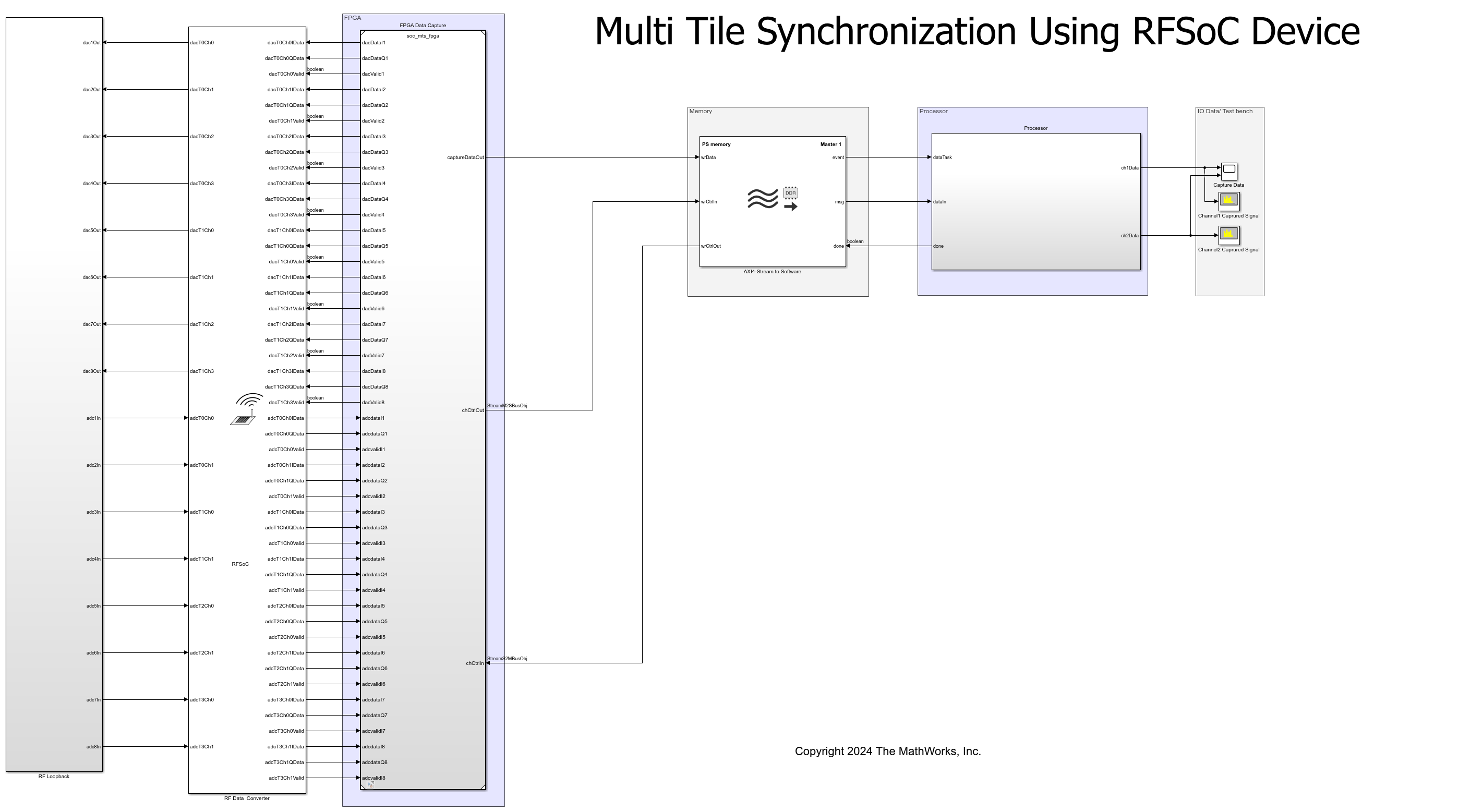

| RF Data Converter | Provide RF data path interface to hardware logic |

| ADC To Vector | Convert concatenated 16-bit ADC input samples to vector outputs |

| Vector To DAC | Convert vector inputs to concatenated 16-bit DAC output samples |

| RFDC Bus Creator | Convert control signals into RF Data Converter real-time interface-compatible bus (Since R2022a) |

| RFDC Bus Selector | Convert RF Data Converter real-time interface-compatible bus into control signals (Since R2022a) |

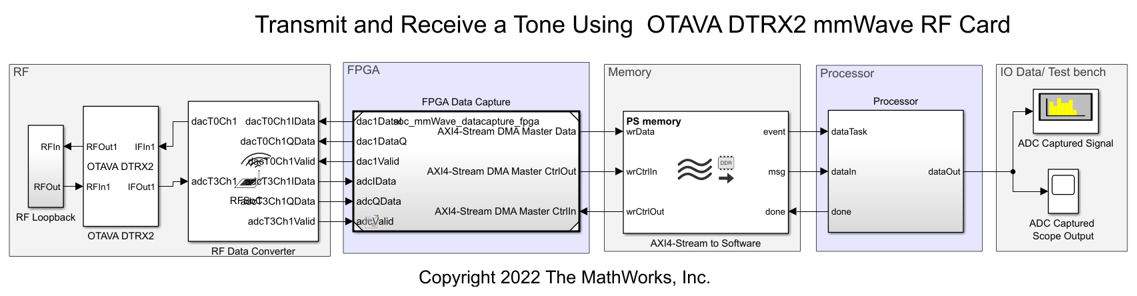

| OTAVA DTRX2 | Integrate OTAVA DTRX2 mmWave radio card with ZCU208 board (Since R2023a) |

| Aurora 64B66B | Provide high-speed serial communication using Xilinx Aurora interface (Since R2023a) |

Tools

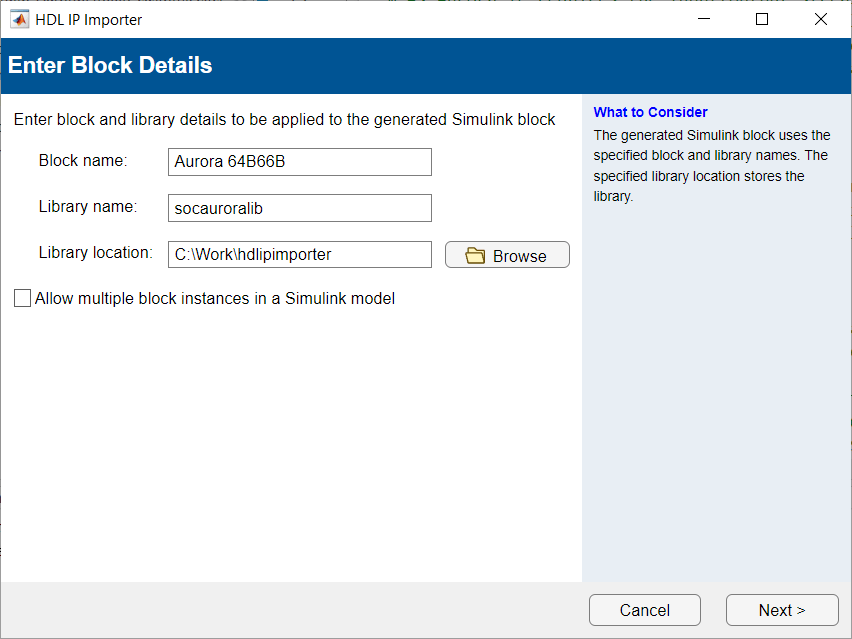

| HDL IP Importer | Import HDL IP core into SoC model (Since R2023a) |

Topics

Wireless Applications

- Introduction To Custom OFDM Using AMD RFSoC

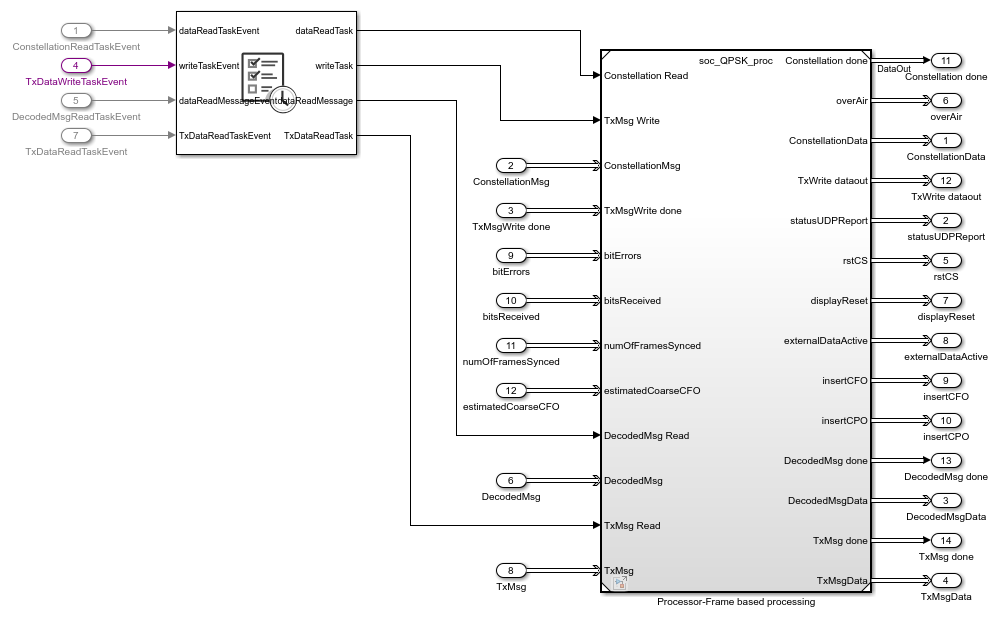

Design and verify a transmitter and receiver for a custom OFDM communication system by using SoC Blockset™ on AMD® RFSoC device. - OFDM Transmit and Receive Using AMD RFSoC Device

Simulate and deploy OFDM transmit and receive algorithm using SoC Blockset on Xilinx® RFSoC device. - Introduction to 5G NR Signal Detection using AMD RFSoC

Deploy primary synchronization signal (PSS) correlation and synchronization signal block (SSB) demodulation using SoC Blockset on Xilinx RFSoC device. - 5G NR SIB1 Recovery for FR1 and FR2 Using AMD RFSoC Device

Deploy 5G NR SIB1 recovery algorithm for FR1 and FR2 using SoC Blockset on Xilinx RFSoC device. - 5G NR Downlink Signal Measurements Using AMD RFSoC Device

Measure SSB signal quality and error vector magnitude (EVM) of the received resource grid using SoC Blockset on Xilinx RFSoC device. - DVB-S2 HDL PL Header Recovery Using Analog Devices AD9361/AD9364

Deploy Digital Video Broadcasting Satellite Second Generation (DVB-S2) time, frequency, and phase synchronization and PL header recovery algorithm using SoC Blockset. - DVB-S2 Receive Using AMD RFSoC Device

Simulate and deploy DVB-S2 transmit and receive algorithm using SoC Blockset on Xilinx RFSoC device. - WLAN Receiver Using AMD RFSoC Device

Simulate and deploy WLAN transmit and receive algorithm using SoC Blockset on Xilinx RFSoC device. - Pulse-Doppler Radar Using AMD RFSoC Device

Build, simulate, and deploy pulse-Doppler radar system using SoC Blockset on Xilinx RFSoC device. - GPS Acquisition Using AMD RFSoC Device

Simulate and deploy global positioning system (GPS) acquisition algorithm on ZCU111 evaluation kit. - Monitor and Analyze Applications Targeted to AMD RFSoC Devices

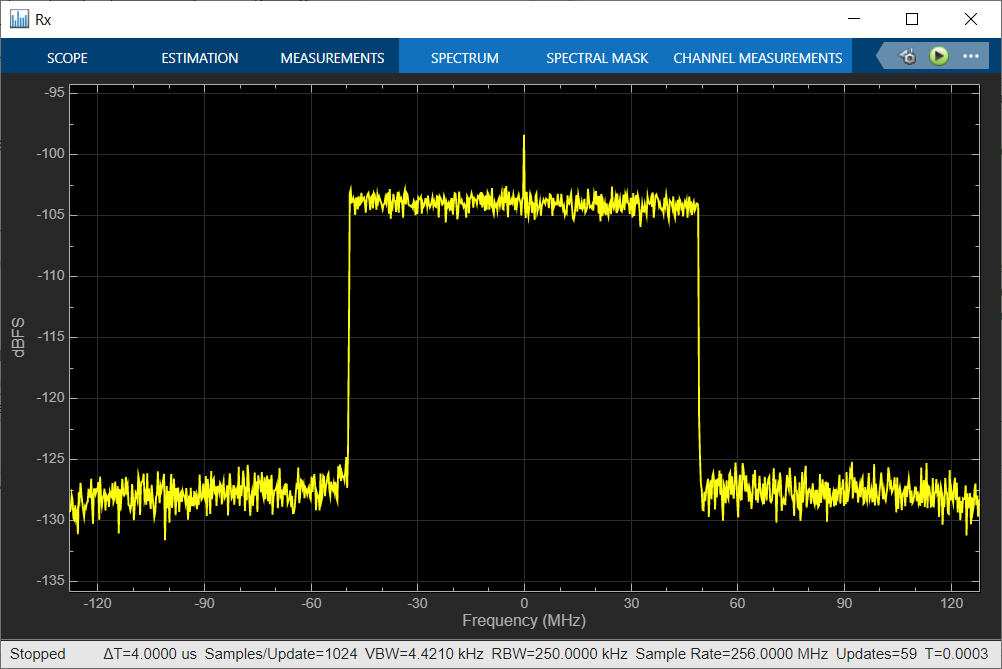

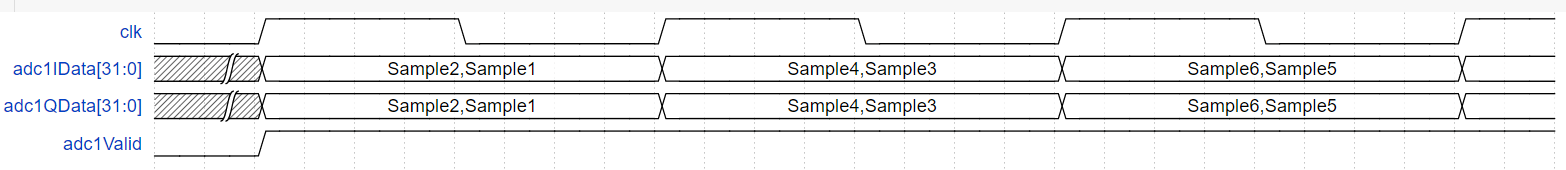

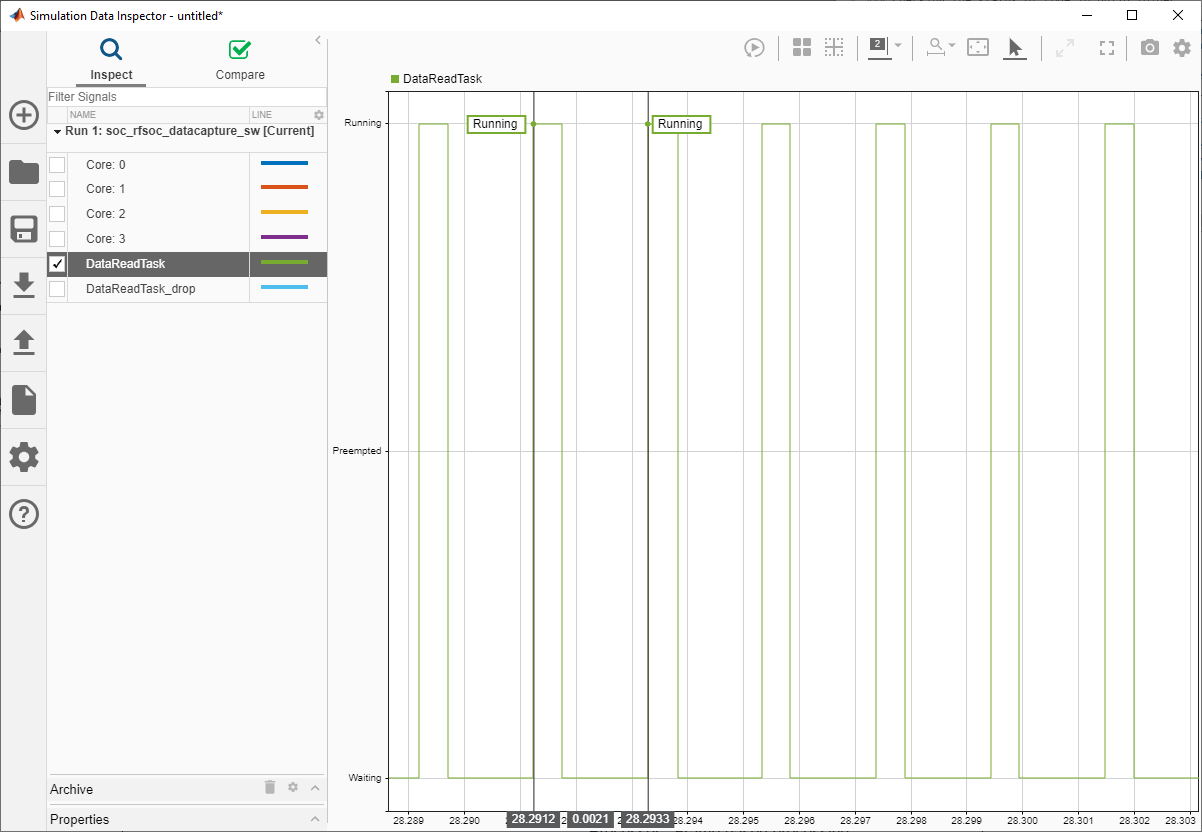

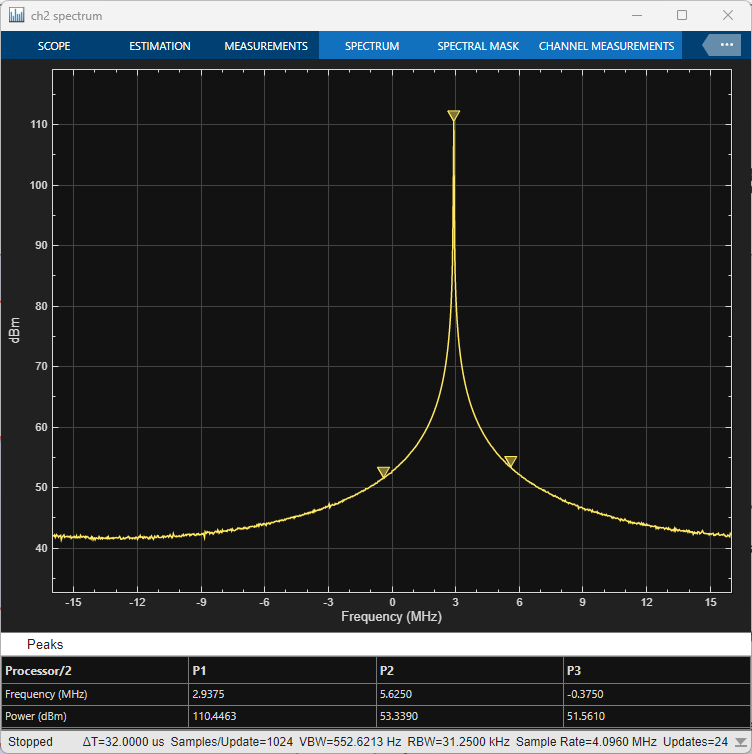

Monitor, analyze, and debug ADC, DAC, and valid signals of AXI4-Stream interface of RF Data Converter using FPGA data capture.

Video Applications

- Edge Detection and Image Overlay

Implement an edge detection and image overlay system with HDMI input and output. - Vertical Video Flipping Using External Memory

Flip an incoming video stream vertically by using a random-access external memory interface. - Contrast Limited Adaptive Histogram Equalization with External Memory

This example shows how to implement the contrast-limited adaptive histogram equalization (CLAHE) algorithm for FPGA, including an external memory interface.