RF Data Converter

Provide RF data path interface to hardware logic

Libraries:

SoC Blockset Support Package for AMD FPGA and SoC Devices /

RFSoC /

ZCU111

SoC Blockset Support Package for AMD FPGA and SoC Devices /

RFSoC /

ZCU208

SoC Blockset Support Package for AMD FPGA and SoC Devices /

RFSoC /

ZCU216

SoC Blockset Support Package for AMD FPGA and SoC Devices /

RFSoC /

ZCU670

Description

Add-On Required: This feature requires the SoC Blockset Support Package for AMD FPGA and SoC Devices add-on.

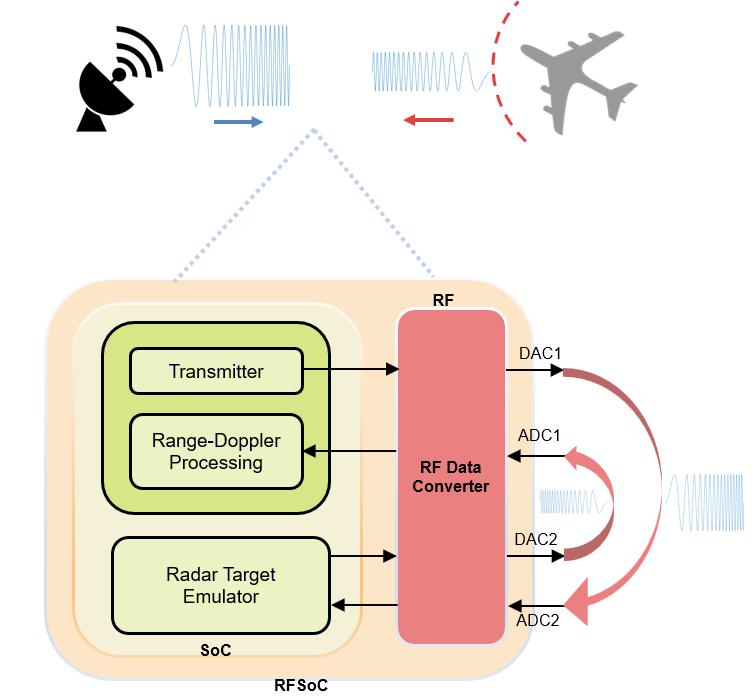

The RF Data Converter block provides an RF data path interface to the hardware logic. In generation, the SoC Builder tool maps the block parameters to the RF Data Converter IP on the hardware.

The block consists of interpolation and decimation filters, complex mixers, analog-to-digital converters (ADCs), and digital-to-analog converters (DACs).

The interpolation filters upsample the input signal by the specified interpolation factor. Specify the interpolation factor by using the Interpolation mode (xN) parameter.

The decimation filters downsample the input signal by the specified decimation factor. Specify the decimation factor by using the Decimation mode (xN) parameter.

A complex mixer shifts the center frequency of the input signal to the specified carrier frequency. Specify the carrier frequency by using the Mixer frequency and NCO frequency (GHz) parameters.

The block supports a maximum of 16 ADC and 16 DAC data paths connecting to the hardware logic. In the Behavioral simulation mode, you can simulate the interpolation and decimation filters and complex mixers.

The block supports Zynq® UltraScale+™ RFSoC Gen 1, Gen 2, Gen 3, and DFE devices. For a full list of supported devices, see Supported RFSoC Devices for RF Data Converter. For specific Zynq UltraScale+ RFSoC device information, see Zynq UltraScale+ RFSoC Product Information from the AMD® website.

Examples

Transmit and Receive Tone Using AMD RFSoC Device - Part 1 System Design

Design and simulate data path using SoC Blockset™ on Xilinx® RFSoC device.

Transmit and Receive Tone Using AMD RFSoC Device - Part 2 Deployment

Implement and verify design using SoC Blockset on Xilinx RFSoC device.

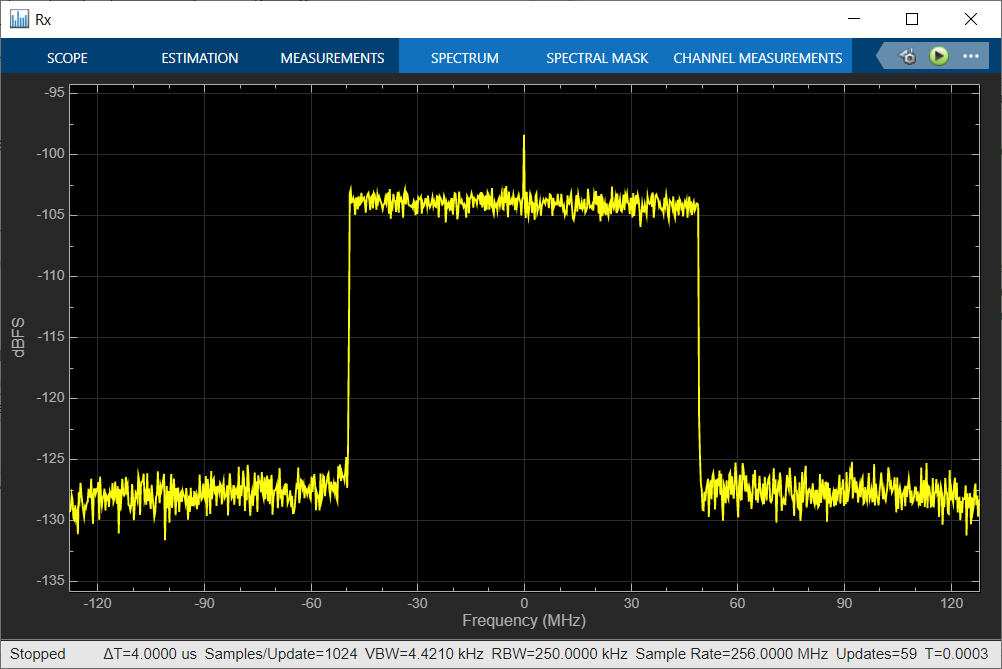

OFDM Transmit and Receive Using AMD RFSoC Device

Simulate and deploy OFDM transmit and receive algorithm using SoC Blockset on Xilinx RFSoC device.

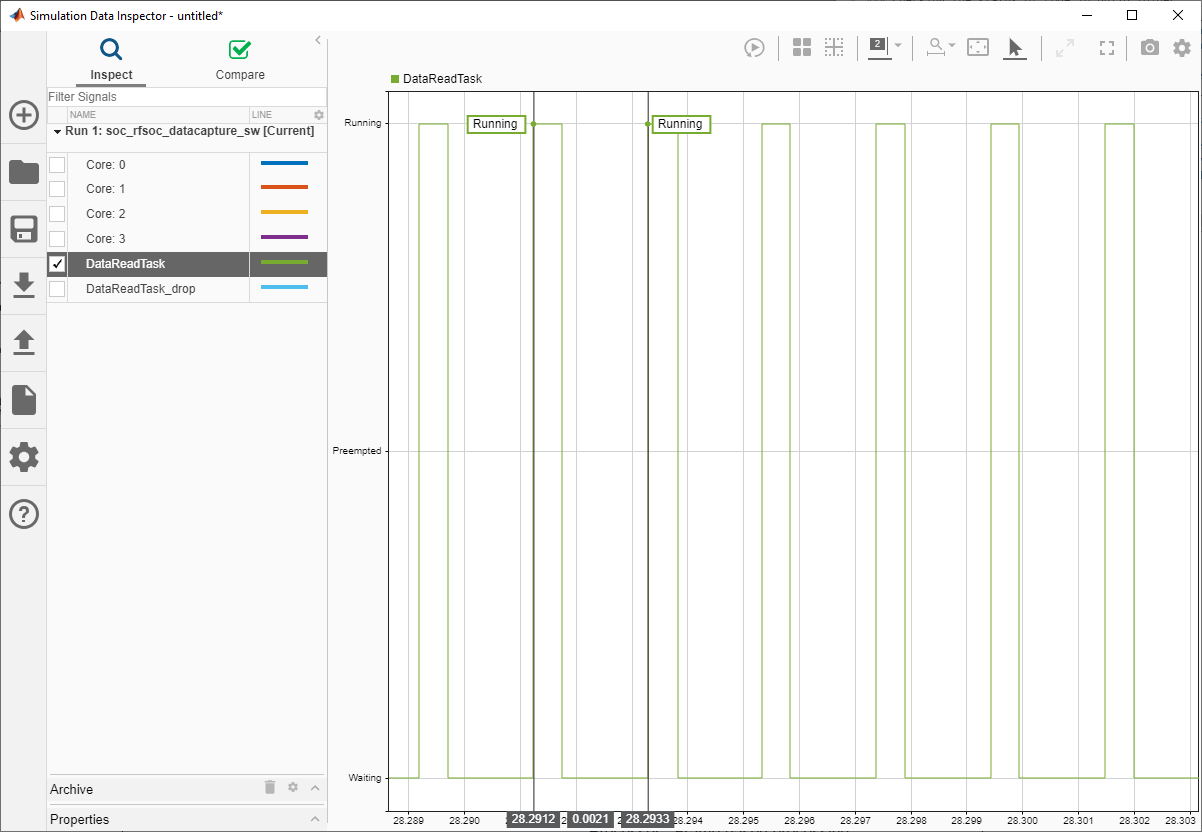

Pulse-Doppler Radar Using AMD RFSoC Device

Build, simulate, and deploy pulse-Doppler radar system using SoC Blockset on Xilinx RFSoC device.

Frequency Hopping Using Xilinx RFSoC Device

Design and implement frequency hopping algorithm using Xilinx RF Data Converter numerically controlled oscillator (NCO) real time ports.

Validate RF Data Converter Configuration

Validate RF data converter (RFDC) configuration in simulation.

Multi-Channel Transceiver Using Xilinx RFSoC Device

Implement multi-channel transceiver using RF Data Converter on Xilinx RFSoC device.

Receive Tone with DDR4 Using IP Core Generation Workflow on Xilinx RFSoC Device

Design, simulate, and deploy algorithm to write and read captured RF samples from external DDR4 memory on Xilinx RFSoC device.

Minimum Variance Distortionless Response Beamformer Using AMD RFSoC Device

Deploy minimum variance distortionless response algorithm on AMD RFSoC device.

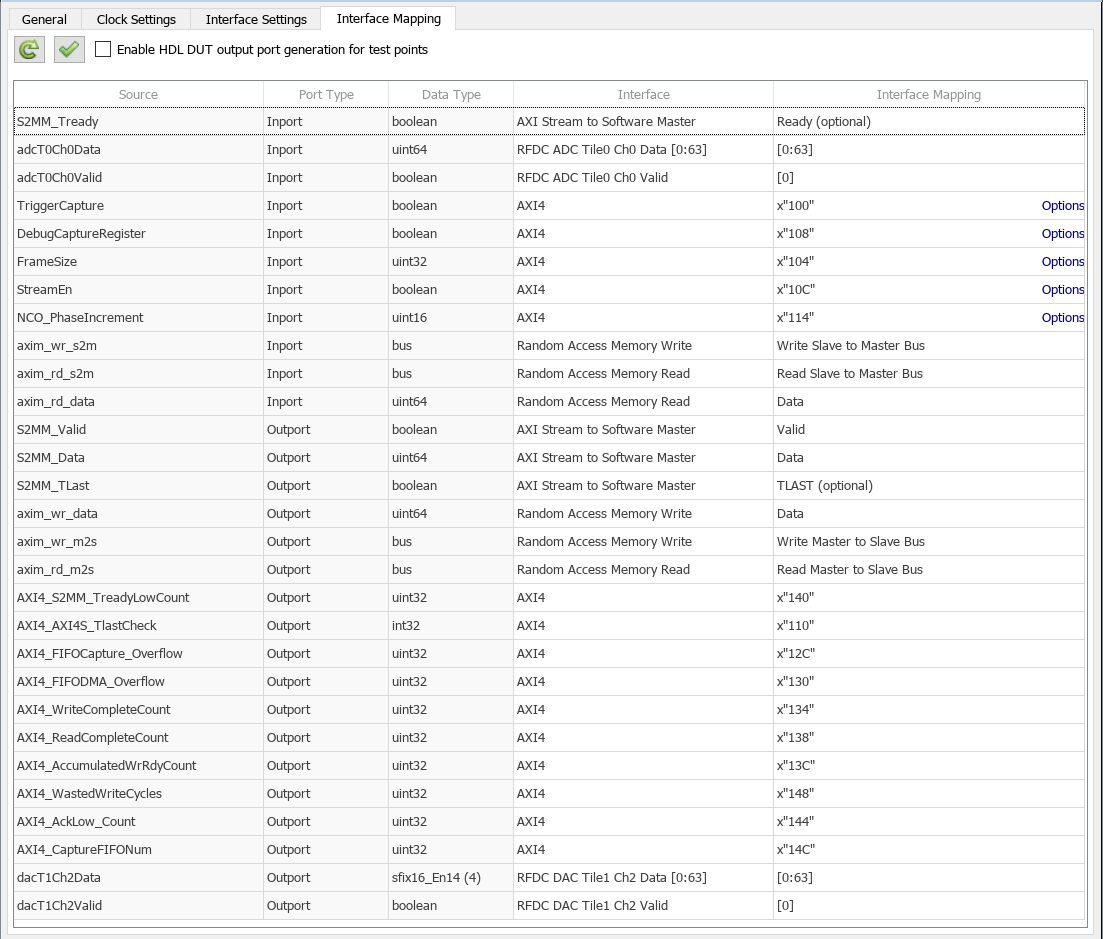

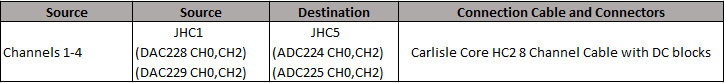

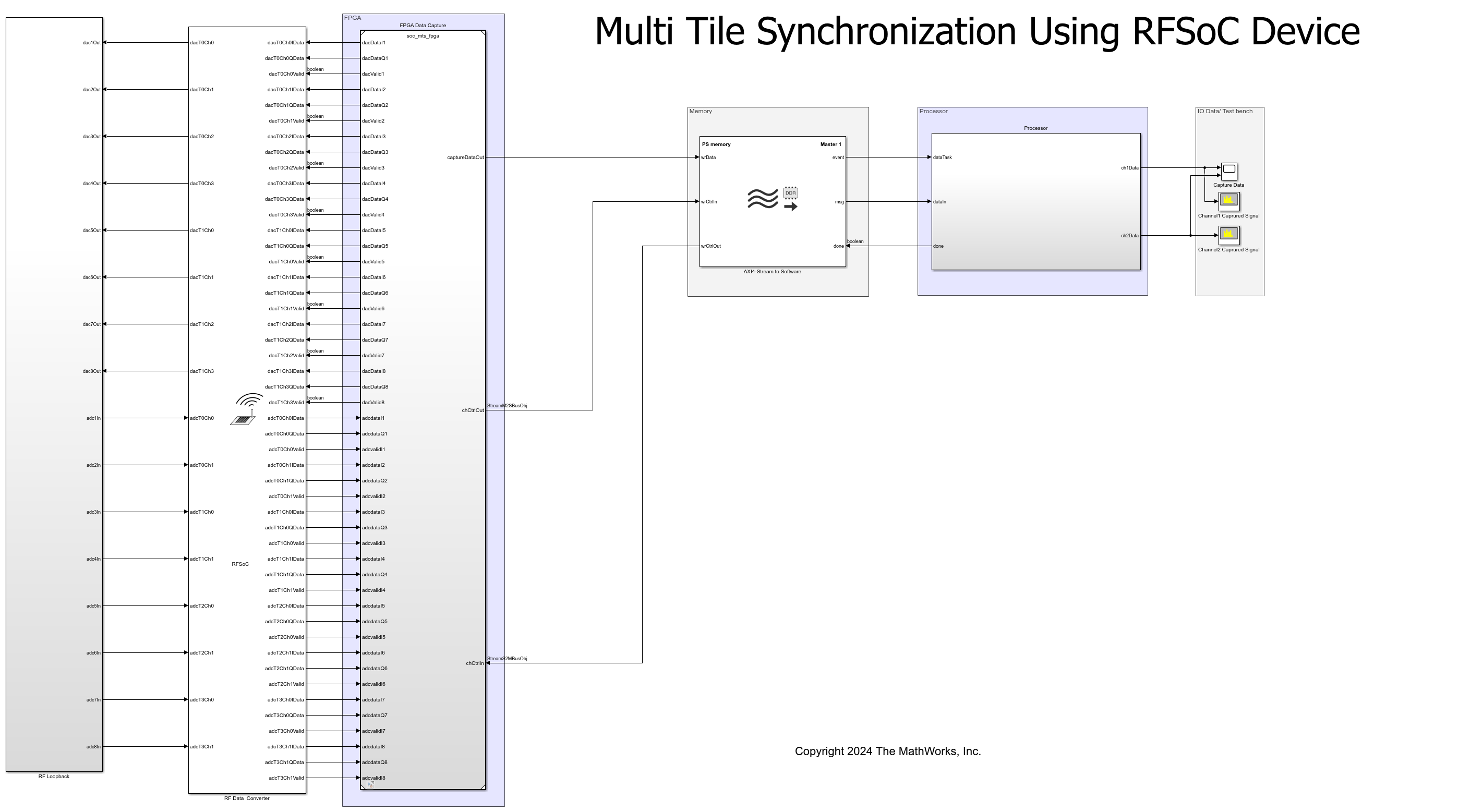

Multi-Tile Synchronization Using AMD RFSoC Device

Implement and use multi-tile synchronization using RF Data Converter block on AMD RFSoC device.

Derive RF Data Converter Configuration Using Frequency Planner App

Use Frequency Planner app to derive RF data converter configuration based on required signal specifications.

- Since R2026a

- Open Live Script

Ports

Input

ADC input data, specified as a column vector.

x indicates the ADC tile number

and y indicates the ADC channel

number. The RF interface parameter sets the number of

adc ports. For example, if RF interface is

set to ADC & DAC 2x2 RF Interface, the block has ports

adcT0Ch0 and adcT0Ch1, that is, one input

port per ADC channel interface.

Valid values for this port depend on the simulation mode and the Digital interface parameter value.

In the Pass-through simulation mode, the block accepts inputs of

int16anduint16data types. In this mode:If you set the Digital interface parameter to

Real, specify this value as an N-element column vector, where N is the number of samples per clock cycle that you set in the Samples per clock cycle parameter.Use this option to specify real-valued data. For example, consider N equal to 2 and data containing two real values D0 and D1. In this case, specify this port value as a vector in the form [D0 D1].

If you set the Digital interface parameter to

I/Q, specify this value as a 2N-element column vector, where N is the number of samples per clock cycle that you set in the Samples per clock cycle parameter.Use this option to specify complex-valued data. For example, consider N equal to 2 and data containing two complex values with real parts I0 and I1 and imaginary parts Q0 and Q1, respectively. In this case, specify this port value as a vector in the form [I0 Q0 I1 Q1].

Data Types:

int16|uint16In the Behavioral simulation mode, the block accepts inputs of

doubledata type. Specify this value as an RN-element column vector, where R is the decimation factor that you set in the Decimation mode (xN) parameter and N is the number of samples per clock cycle that you set in the Samples per clock cycle parameter.Data Types:

double

Data Types: int16 | uint16 | double

DAC input data, specified as a scalar or column vector with a length in the range [1, N], where N is the number of samples per clock cycle that you specify in the Samples per clock cycle parameter.

x indicates the DAC tile number

and y indicates the DAC channel

number. The RF interface parameter sets the number of

dacTxChyData

ports.

For more information about the data format, see Data Format Between RF Data Converter Block and Hardware Logic.

Dependencies

To enable this port, set the Digital interface parameter to

Real.

Data Types: int16 | int32 | int64 | uint16 | uint32 | uint64 | fixed point

Real part of the DAC input, specified as a scalar or column vector with a length in the range [1, N], where N is the number of samples per clock cycle that you specify in the Samples per clock cycle parameter.

x indicates the DAC tile number

and y indicates the DAC channel

number. The RF interface parameter sets the number of

dacTxChyIData

ports.

For more information about the data format, see Data Format Between RF Data Converter Block and Hardware Logic.

Dependencies

To enable this port, set the Digital interface parameter to

I/Q.

Data Types: int16 | int32 | int64 | uint16 | uint32 | uint64 | fixed point

Imaginary part of the DAC input, specified as a scalar or column vector with a length in the range [1, N], where N is the number of samples per clock cycle that you specify in the Samples per clock cycle parameter.

x indicates the DAC tile number

and y indicates the DAC channel

number. The RF interface parameter sets the number of

dacTxChyQData

ports.

For more information about the data format, see Data Format Between RF Data Converter Block and Hardware Logic.

Dependencies

To enable this port, set the Digital interface parameter to

I/Q.

Data Types: int16 | int32 | int64 | uint16 | uint32 | uint64 | fixed point

Indication of valid DAC input data, specified as a scalar.

A value of 1 indicates that the data on the

dacTxChyData

port is valid or that the data on the

dacTxChyIData

and

dacTxChyQData

ports is valid.

x indicates the DAC tile number

and y indicates the DAC channel

number. The RF interface parameter sets the number of

dacTxChyValid

ports.

Data Types: Boolean

ADC real-time control input, specified as a bus.

x indicates the ADC tile number

and y indicates the ADC channel

number. The RF interface parameter sets the number of

adcTxChyRealTimeCtrlIn

ports. For example, if you set the RF interface parameter to

ADC & DAC 2x2 RF Interface, the block has two input

ports, one per ADC channel interface.

Dependencies

To enable this port, select Real-time ports or Real-time NCO ports on the Advanced tab.

Data Types: DUT2RFDCRealTimeCtrlBusObj

ADC numerically controlled oscillator (NCO) update request, specified as a Boolean

scalar. To request an update of the ADC NCO settings, set this input signal to

High.

x indicates the ADC tile number.

The RF interface parameter sets the number of

adcTxNCOUpdateReq ports. For

example, if you set the RF interface parameter to

ADC & DAC 2x2 RF Interface, the block has one input

port, one per ADC tile.

Dependencies

To enable this port, select Real-time NCO ports under the ADC section on the Advanced tab.

Data Types: Boolean

DAC real-time control input, specified as a bus.

x indicates the DAC tile number

and y indicates the DAC channel

number. The RF interface parameter sets the number of

dacTxChyRealTimeCtrlIn

ports. For example, if you set the RF interface parameter to

ADC & DAC 2x2 RF Interface, the block has two input

ports, one per DAC channel interface.

Dependencies

To enable this port, select Real-time NCO ports under the DAC section on the Advanced tab.

Data Types: DUT2RFDCRealTimeCtrlBusObj

DAC NCO update request, specified as a Boolean scalar. To request an update of the

DAC NCO settings, set this input signal to High.

x indicates the DAC tile number.

The RF interface parameter sets the number of

dacTxNCOUpdateReq ports. For

example, if you set the RF interface parameter to

ADC & DAC 2x2 RF Interface, the block has one input

port, one per DAC tile.

Dependencies

To enable this port, select Real-time NCO ports under the DAC section on the Advanced tab.

Data Types: Boolean

Synchronous clock gating for the multi-tile synchronization (MTS) mode, specified

as a Boolean scalar. To disable the DAC tile from the Sysref clock

signal, set this input signal to High.

Dependencies

To enable this port, select Multi tile sync under the Common Parameters section and select Real-time NCO ports under the DAC section on the Advanced tab.

Data Types: Boolean

Synchronous clock re-enabling for the MTS mode, specified as a Boolean scalar. To

re-enable the Sysref clock signal, set this input signal to

High.

Dependencies

To enable this port, select Multi tile sync under the Common Parameters section and select Real-time NCO ports under the DAC section on the Advanced tab.

Data Types: Boolean

Output

DAC output data, returned as a column vector.

In the Pass-through simulation mode, the block returns outputs of

int16data type. In this mode:If you set the Digital interface parameter to

Real, the block returns outputs as a N-element column vector, where N is the number of samples per clock cycle that you set in the Samples per clock cycle parameter.For example, consider N equal to 2 and an input to the dacT0Ch1Data port with a size of 32 bits. In this case, this port returns a vector [S0 S1], where S0 is a16-bit value sliced from 0 to 15 bits of input data on the dacT0Ch1Data port and S1 is a 16-bit value sliced from 16 to 31 bits of input data on the dacT0Ch1Data port.

If you set the Digital interface parameter to

I/Q, the block returns outputs as a 2N-element column vector, where N is the number of samples per clock cycle that you set in the Samples per clock cycle parameter.For example, consider N equal to 2 and inputs to the dacT0Ch1IData and dacT0Ch1QData ports with a size of 32 bits. In this case, this port returns a vector [I0 Q0 I1 Q1], where I0 is a16-bit value sliced from 0 to 15 bits of input data on the dacT0Ch1IData port, I1 is a 16-bit value sliced from 16 to 31 bits of input data on the dacT0Ch1IData port, Q0 is a16-bit value sliced from 0 to 15 bits of input data on the dacT0Ch1QData port, and Q1 is a 16-bit value sliced from 16 to 31 bits of input data on the dacT0Ch1QData port.

Data Types:

int16In the Behavioral simulation mode, the block returns outputs of

doubledata type. The block returns outputs as an RN-element column vector, where R is the interpolation factor that you set in the Interpolation mode (xN) parameter and N is the number of samples per clock cycle that you set in the Samples per clock cycle parameter.Data Types:

double

x indicates the DAC tile number

and y indicates the DAC channel

number. The RF interface parameter sets the number of

dacTxChy

ports.

Data Types: int16 | double

ADC output data, returned as a scalar or column vector with a length in the range [1, N], where N is the number of samples per clock cycle that you specify in the Samples per clock cycle parameter.

x indicates the ADC tile number

and y indicates the ADC channel

number. The RF interface parameter sets the number of

adcTxChyData

ports.

For more information about the data format, see Data Format Between RF Data Converter Block and Hardware Logic.

Dependencies

To enable this port, set the Digital interface parameter to

Real.

Data Types: uint16 | uint32 | uint64 | fixed point

Real part of the ADC output, returned as a scalar or column vector with a length in the range [1, N], where N is the number of samples per clock cycle that you specify in the Samples per clock cycle parameter.

x indicates the ADC tile number

and y indicates the ADC channel

number. The RF interface parameter sets the number of

adcTxChyIData

ports.

For more information about the data format, see Data Format Between RF Data Converter Block and Hardware Logic.

Dependencies

To enable this port, set the Digital interface parameter to

I/Q.

Data Types: uint16 | uint32 | uint64 | fixed point

Imaginary part of the ADC output, returned as a scalar or column vector with a length in the range [1, N], where N is the number of samples per clock cycle that you specify in the Samples per clock cycle parameter.

x indicates the ADC tile number

and y indicates the ADC channel

number. The RF interface parameter sets the number of

adcTxChyQdata

ports.

For more information about the data format, see Data Format Between RF Data Converter Block and Hardware Logic.

Dependencies

To enable this port, set the Digital interface parameter to

I/Q.

Data Types: uint16 | uint32 | uint64 | fixed point

Indication of valid ADC output data, returned as a Boolean scalar.

A value of 1 indicates that the data on the

adcTxChyData

port is valid or that the data on the

adcTxChyIData

and

adcTxChyQData

ports is valid.

x indicates the ADC tile number

and y indicates the ADC channel

number. The RF interface sets the number of

adcTxChyValid

ports.

Data Types: Boolean

ADC real-time control output, returned as a bus. In the

Pass-through simulation mode, this port always has a value of

Low.

x indicates the ADC tile number

and y indicates the ADC channel

number. The RF interface parameter sets the number of

adcTxChyRealTimeCtrlOut

ports. For example, if you set the RF interface parameter to

ADC & DAC 2x2 RF Interface, the block has two output

ports, one per ADC channel interface.

Dependencies

To enable this port, select Real-time ports on the Advanced tab.

Data Types: RFDC2DUTRealTimeCtrlBusObj

Indication that a DAC NCO update is in progress, returned as a Boolean scalar. In

MTS mode, for Tile 0, this value returned as a scalar of type

fixdt(0,2,0). In the Pass-through simulation

mode, this port always has a value of Low.

x indicates the DAC tile number.

The RF interface parameter sets the number of

dacTxNCOUpdateBusy ports. For

example, if you set the RF interface parameter to

ADC & DAC 2x2 RF Interface, the block has one output

port, one per DAC tile.

Dependencies

To enable this port, select Real-time NCO ports under the DAC section on the Advanced tab.

Data Types: Boolean | fixdt(0,2,0)

Indication that an ADC NCO update is in progress, returned as a Boolean scalar. In

the Pass-through simulation mode, this port always has a value of

Low.

x indicates the ADC tile number.

The RF interface parameter sets the number of

adcTxNCOUpdateBusy ports. For

example, if you set the RF interface parameter to

ADC & DAC 2x2 RF Interface, the block has one output

port, one per ADC tile.

Dependencies

To enable this port, select Real-time NCO ports under the ADC section on the Advanced tab.

Data Types: Boolean

Parameters

Select the simulation mode.

Pass-through — In this simulation mode, the block outputs the same data as the input. The interpolation, decimation, and mixers settings do not impact the block output values.

Behavioral — In this simulation mode, the interpolation, decimation, and mixers settings impact the block output values.

This parameter is read-only.

For details about how to choose a hardware board and configure its parameters, see Hardware Implementation Pane.

Specify the RF channel interface type.

To select a predefined set of ADC and DAC combinations, set this parameter to

ADC & DAC 1x1 RF Interface, ADC & DAC

2x2 RF Interface, ADC & DAC 4x4 RF

Interface, ADC & DAC 8x8 RF Interface, or

ADC & DAC 16x16 RF Interface. Available options for

this parameter vary as per the selected hardware board. To select the required number of

DAC or ADC combinations, set this parameter to

Customize.

Example: ADC & DAC 2x2 RF Interface specifies two ADC

and two DAC RF channel interfaces.

Specify the digital interface type.

Real— Supports real dataI/Q— Supports complex data by using real and imaginary ports

DAC

The number of panes and number of DACs in each pane in the DAC tab depend on the RFSoC device in the selected hardware board. The tiles and DACs shown on the block mask indicate the corresponding tiles and DACs on the selected hardware board. For example, if you select the Xilinx Zynq UltraScale+ RFSoC ZCU111 evaluation kit, the DAC tab contains two panes (Tile 0 and Tile 1), and each pane contains four DACs. For a ZCU111 board, DAC 0, DAC 1, DAC 2, and DAC 3 in Tile 0 correspond to DAC 0, DAC 1, DAC 2, and DAC 3 in DAC tile 228, respectively. DAC 0, DAC 1, DAC 2, and DAC 3 in Tile 1 correspond to DAC 0, DAC 1, DAC 2, and DAC 3 in DAC tile 229, respectively.

The selection of tiles and the respective DACs is predefined when you set the

RF interface parameter to ADC & DAC 1x1 RF

Interface, ADC & DAC 2x2 RF Interface,

ADC & DAC 4x4 RF Interface, ADC & DAC 8x8

RF Interface, or ADC & DAC 16x16 RF

Interface. You cannot modify the tile and DAC selection when you select these

predefined options. To modify the tile and DAC selections, set the RF

interface parameter to Customize.

Select this parameter to apply the same parameter values to all of the selected DACs.

Clear this parameter to specify different parameter values for each of the selected DACs.

Dependencies

To enable this parameter, set the RF interface parameter to

Customize.

Specify the sampling rate as a scalar in a range that is based on the selected hardware board. Units are in mega samples per second.

This table shows the sampling rate range of the block for the supported Zynq UltraScale+ RFSoC Gen 1, Gen 2, Gen 3, and DFE devices.

| Generation | Device | Sampling Rate Range (MSPS) |

|---|---|---|

Gen 1 | ZU25DR | [500, 6554] |

ZU27DR | ||

ZU28DR | ||

ZU29DR | ||

Gen 2 | ZU39DR | [500, 6554] |

Gen 3 | ZU47DR | [500, 7000] |

ZU48DR | ||

ZU49DR | ||

| DFE | ZU63DR | |

ZU64DR | ||

ZU65DR | ||

ZU67DR |

Specify the interpolation factor.

Note

Gen 1 and Gen 2 devices support interpolation factors of 1, 2, 4, and 8. Gen 3 and DFE devices support interpolation factors of 1, 2, 3, 4, 5, 6, 8, 10, 12, 16, 20, 24, and 40.

Specify the number of samples per clock cycle. Available options for the number of samples per clock cycle vary with the selected hardware board and digital interface type.

The block calculates the stream data width as 16 x Samples per clock cycle.

The block calculates the stream clock frequency as Sample rate (MSPS) / Interpolation mode (xN) x Samples per clock cycle.

Specify the mixer type.

To use Bypassed, set the Digital

interface parameter to Real.

To select either Coarse or

Fine, set the Digital interface

parameter to I/Q.

This parameter is read-only.

To use Real->Real, set the Digital

interface parameter to Real.

To use I/Q->Real, set the Digital

interface parameter to I/Q.

Specify the mixer frequency.

Dependencies

To enable this parameter, set the Digital interface

parameter to I/Q and Mixer type

parameter to Coarse.

Specify the NCO frequency values as a scalar or m-element row vector, where m is the number of DACs.

When you set the RF interface parameter to

Customize and clear the Match parameters of all

DACs parameter, m must be 1.

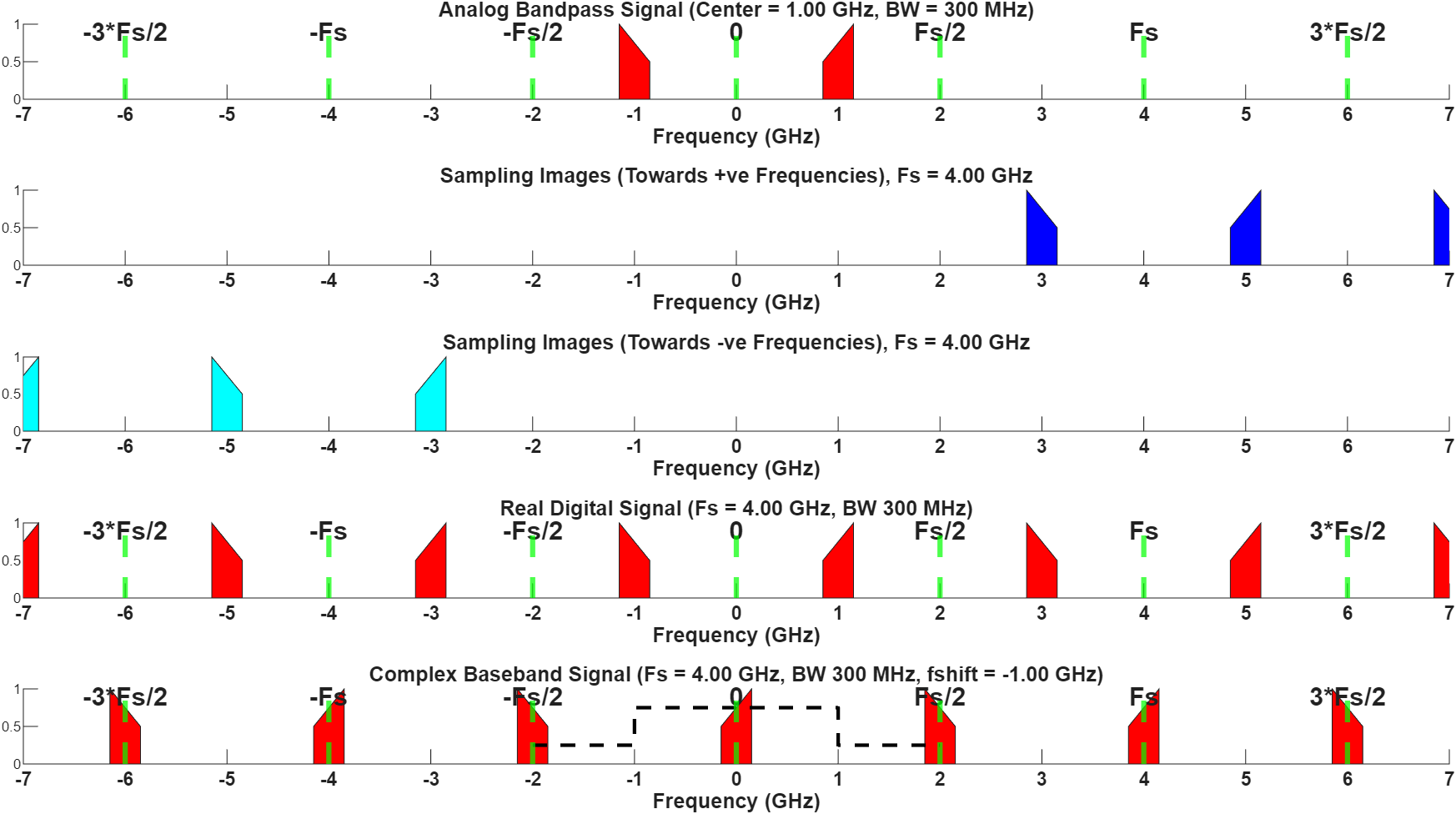

The block derives the Analog Nyquist zone for a DAC channel based on the NCO frequency and sample rate (Fs).

Zone 1 — The DAC output is in Nyquist zone 1 if NCO frequency is less than Fs/2. In this Nyquist zone, the block supports simulation capability.

Zone 2 — The DAC output is in Nyquist zone 2 if NCO frequency is greater than Fs/2. In this Nyquist zone, the block does not support simulation capability. In simulation, the DAC centers the output around a folded frequency of the specified NCO frequency in zone 1.

Dependencies

To enable this parameter, set the Digital interface

parameter to I/Q and the Mixer type

parameter to Fine.

Specify the NCO phase as a scalar or m-element row vector, where m is the number of DACs.

When you set the RF interface parameter to

Customize and clear the Match parameters of all

DACs parameter, m must be 1.

Dependencies

To enable this parameter, set the Digital interface

parameter to I/Q and the Mixer type

parameter to Fine.

Select this parameter to convert the analog sinc output response from the DAC to a flat-output response.

ADC

The number of panes and number of ADCs in each pane in the ADC tab depend on the selected hardware board. The tiles and ADCs shown on the block mask indicate the corresponding tiles and ADCs on the selected hardware board. For example, if you select the Xilinx Zynq UltraScale+ RFSoC ZCU111 evaluation kit, the ADC tab contains four panes (Tile 0, Tile 1, Tile 2, and Tile 3), and each pane contains two ADCs. For a ZCU111 board, ADC 0 and ADC 1 in Tile 0 correspond to ADC 0 and ADC 1 in ADC tile 224, respectively. ADC 0 and ADC 1 in Tile 1 correspond to ADC 0 and ADC 1 in ADC tile 225, respectively. ADC 0 and ADC 1 in Tile 2 correspond to ADC 0 and ADC 1 in ADC tile 226, respectively. ADC 0 and ADC 1 in Tile 3 correspond to ADC 0 and ADC 1 in ADC tile 227, respectively.

The selection of tiles and the respective ADCs is predefined when you set the

RF interface parameter to ADC & DAC 1x1 RF

Interface, ADC & DAC 2x2 RF Interface,

ADC & DAC 4x4 RF Interface, ADC & DAC 8x8

RF Interface, or ADC & DAC 16x16 RF

Interface. You cannot modify the tile and ADC selection when you select these

predefined options. To modify the tile and ADC selections, set the RF

interface parameter to Customize.

Select this parameter to output data as a frame of samples. Clear this parameter to output data as a scalar.

Select this parameter to apply the same parameter values to all of the selected ADCs.

Clear this parameter to specify different parameter values for each of the selected ADCs.

Dependencies

To enable this parameter, set the RF interface parameter to

Customize.

Specify the sampling rate as a scalar in a range that is based on the selected hardware board. Units are in mega samples per second.

This table shows the sampling rate range of the block for the supported Zynq UltraScale+ RFSoC Gen 1, Gen 2, Gen 3, and DFE devices.

| Generation | Device | Sampling Rate Range (MSPS) |

|---|---|---|

Gen 1 | ZU25DR | [1000, 4096] |

ZU27DR | [1000, 4096] | |

ZU28DR | [1000, 4096] | |

ZU29DR | [500, 2058] | |

Gen 2 | ZU39DR | [500, 2220] |

Gen 3 | ZU47DR | [1000, 5000] |

ZU48DR | [1000, 5000] | |

ZU49DR | [500, 2500] | |

| DFE | ZU63DR | [500, 2950] — For quad ADC tiles [1000, 5900] — For dual ADC tiles |

ZU64DR | [500, 2950] — For quad ADC tiles [1000, 5900] — For dual ADC tiles | |

ZU65DR | [1000, 5900] | |

ZU67DR | [500, 2950] — For quad ADC tiles [1000, 5900] — For dual ADC tiles |

Specify the decimation factor.

Note

Gen 1 and Gen 2 devices support decimation factors of 1, 2, 4, and 8. Gen 3 and DFE devices support decimation factors of 1, 2, 3, 4, 5, 6, 8, 10, 12, 16, 20, 24, and 40.

Specify the number of samples per clock cycle. Available options for the number of samples per clock cycle vary with the selected hardware board and digital interface type.

The block calculates the stream data width as: 16 x Samples per clock cycle.

The block calculates the stream clock frequency as: Sample rate (MSPS) / Decimation mode (xN) x Samples per clock cycle.

Specify the mixer type.

To use Bypassed, set the Digital

interface parameter to Real.

To select either Coarse or

Fine, set the Digital interface

parameter to I/Q.

This parameter is read-only.

To use Real->Real, set the Digital

interface parameter to Real.

To use Real->I/Q, set the Digital

interface parameter to I/Q.

Specify the mixer frequency.

Dependencies

To enable this parameter, set the Digital interface

parameter to I/Q and Mixer type

parameter to Coarse.

Specify the NCO frequency values as a scalar or m-element row vector, where m is the number of ADCs.

When you set the RF interface parameter to

Customize and clear the Match parameters of all

ADCs parameter, m must be 1.

Dependencies

To enable this parameter, set the Digital interface

parameter to I/Q and Mixer type

parameter to Fine.

Specify the NCO phase as a scalar or m-element row vector, where m is the number of ADCs.

When you set the RF interface parameter to

Customize and clear the Match parameters of all

ADCs parameter, m must be 1.

Dependencies

To enable this parameter, set the Digital interface

parameter to I/Q and Mixer type

parameter to Fine.

Advanced

Common Parameters

Select this parameter to enable MTS.

In generation, the Xilinx

RF Data Converter tool provides synchronization clocks and ADC and DAC

clocks to the RF Data Converter hardware IP. In MTS mode, these synchronization clocks

depend on the ADC and DAC sampling rates. Because, the Xilinx RF Data

Converter tool provides a set of fixed default synchronization clocks in MTS

mode and supports only these sample rates: 737.28,

1474.56, 1966.08, 2457.6,

2949.12, 3072, 3932.16,

4669.44, 4915.2, 5898.24,

and 6144.

For more information on MTS mode, see Zynq UltraScale+ RFSoC RF Data Converter Gen 1/2/3/DFE LogiCORE IP Product Guide (PG269) in the AMD documentation.

Limitations

This parameter is not supported for the Zynq UltraScale+ RFSoC DFE ZCU670 Evaluation Kit and other DFE devices.

Select this parameter to enable the external phase-locked loop (PLL).

Each ADC and DAC tile includes an internal PLL. This internal PLL together with a

clocking instance provides ADC and DAC clocks for each tile as per the ADC or DAC

sampling rates. When you select this parameter, the internal PLL disables, and the

clocking circuit directly provides ADC and DAC clocks for each tile. The Xilinx

RF Data Converter tool supports only these external PLL clock

frequencies: 737.28, 1474.56,

1966.08, 2048, 2457.6,

2949.12, 3072, 3194.88,

3276.8, 3686.4, 3932.16,

4096, 4423.68, 4669.44,

4915.2, 5734.4, 5898.24,

6144, 6389.76, 6400, and

6553.6.

DAC

Select this parameter to add real-time NCO ports for the DAC. You can use these ports to modify the NCO frequency and phase during run time.

Follow these instructions to modify the NCO frequency and phase for the DAC based on the MTS mode selection.

Multi tile sync is off

Set the required NCO frequency, phase, and phase reset values by using the NCOFrequency, NCOPhase, and NCOPhaseReset signals, respectively, of the dacTxChyRealTimeCtrlIn port.

Set the update enable bits to determine which NCO frequency and phase bits to update by using the NCOUpdateEnable signal of the dacTxChyRealTimeCtrlIn port.

Request an update of the DAC NCO settings by setting the dacTxNCOUpdateReq port to

High.Hold the frequency, phase, and phase rest values until the dacTxNCOUpdateBusy port remains

High.

Multi tile sync is on

Set the required NCO frequency, phase, and phase reset values by using the NCOFrequency, NCOPhase, and NCOPhaseReset signals, respectively, of all the dacTxChyRealTimeCtrlIn ports that you want to update. At the same time, set the update enable bits to determine which NCO frequency and phase bits to update by using the NCOUpdateEnable signal of all the dacTxChyRealTimeCtrlIn ports.

Disable the DAC from the

Sysrefclock signal by setting the dacT0SysrefGating port toHigh. Let this port remainHighor set it toLowafter the update is complete.Request an update of the DAC NCO settings for Tile 0 by setting the dacT0NCOUpdateReq port to

High. It sets Bit 1 of the dacT0NCOUpdateBusy port toHigh.Set all the dacTxNCOUpdateReq ports in MTS mode to

High.The NCO register writes are complete when all the dacTxNCOUpdateBusy ports in MTS mode, other than Bit 1 of the dacT0NCOUpdateBusy port, are

Low.Re-enable the

Sysrefclock signal by setting the dacT0SysrefReEnable port toHigh. The NCO update is complete when Bit 1 of the dacT0NCOUpdateBusy port goesLow.

For more information on NCO settings, see NCO Frequency Hopping in the AMD documentation.

Dependencies

To enable this parameter, set the Digital interface

parameter to I/Q and the Mixer type

parameter on the DAC tab to

Fine.

ADC

Select this parameter to add real-time NCO ports for the ADC. You can use these ports to modify the NCO frequency and phase during run time.

Follow these instructions to modify the NCO frequency and phase for the ADC based on the MTS mode selection.

Multi tile sync is off

Set the required NCO frequency, phase, and phase reset values by using the NCOFrequency, NCOPhase, and NCOPhaseReset signals, respectively, of the adcTxChyRealTimeCtrlIn port.

Set the update enable bits to determine which NCO frequency and phase bits to update by using the NCOUpdateEnable signal of the adcTxChyRealTimeCtrlIn port.

Request an update of the ADC NCO settings by setting the adcTxNCOUpdateReq port to

High.Hold the frequency, phase, and phase reset values until the adcTxNCOUpdateBusy port remains

High.

Follow these instructions to modify the NCO frequency and phase for the ADC when

Multi tile sync is on.

Multi tile sync is on

Set the required NCO frequency, phase, and phase reset values by using the NCOFrequency, NCOPhase, and NCOPhaseReset signals, respectively, of all the adcTxChyRealTimeCtrlIn ports that you want to update. At the same time, set the update enable bits to determine which NCO frequency and phase bits to update by using the NCOUpdateEnable signal of all the adcTxChyRealTimeCtrlIn ports.

Disable the ADC from the

Sysrefclock signal by setting the dacT0SysrefGating port toHigh. Let this port remainHighor set it toLowafter the update is complete.Request an update of the DAC NCO settings for Tile 0 by setting the dacT0NCOUpdateReq port to

High. It sets Bit 1 of the dacT0NCOUpdateBusy port toHigh.Set all the adcTxNCOUpdateReq ports in MTS mode to

High.The NCO register writes are complete when all the adcTxNCOUpdateBusy ports in MTS mode, other than Bit 1 of the dacT0NCOUpdateBusy port, are

Low.Re-enable the

Sysrefclock signal by setting the dacT0SysrefReEnable port toHigh. The NCO update is complete when Bit 1 of the dacT0NCOUpdateBusy port goesLow.

For more information on NCO settings, see NCO Frequency Hopping in the AMD documentation.

Dependencies

To enable this parameter, set the Digital interface

parameter to I/Q and the Mixer type

parameter on the ADC tab to

Fine.

Select this parameter to add real-time ports for the ADC. Selecting this parameter enables the threshold monitoring circuit, which compares the ADC sampled data with the specified threshold values.

For more information on real-time ports and threshold settings, see Zynq UltraScale+ RFSoC RF Data Converter Gen 1/2/3/DFE LogiCORE IP Product Guide (PG269) in the AMD documentation.

Select threshold mode for the first threshold as one of these options.

Sticky over— Set the threshold status signal toHighwhen the ADC sampled data exceeds the threshold value that you set in the Threshold1 parameter. The threshold status signal remainsHighuntil you set thePLEventsignal in the adcTxChyRealTimeCtrlIn input bus port toHigh.Sticky under— Set the threshold status signal toHighwhen the ADC sampled data remains below the threshold value, which you set in the Threshold1 parameter, for the number of samples that you set in the Number of sample(s) below threshold1 parameter. The threshold status signal remainsHighuntil you set thePLEventsignal in the adcTxChyRealTimeCtrlIn input bus port toHigh.Hysteresis— Set the threshold status signal toHighwhen the ADC sampled data exceeds the upper threshold value. Set the threshold status signal toLowwhen the ADC sampled data remains below the lower threshold value for the number of samples that you specify in the Number of sample(s) below threshold1 parameter.

Dependencies

To enable this parameter, select Real-time ports.

Specify the threshold value for the first threshold. For the sticky over threshold mode, this value serves as the upper threshold value. For the sticky under threshold mode, this value serves as the lower threshold value. For the hysteresis threshold mode, specify the threshold values in the format [Tlower Tupper], where Tlower is the lower threshold value and Tupper is the upper threshold value.

Dependencies

To enable this parameter, select Real-time ports.

Specify the number of samples below the threshold value for the first threshold.

Dependencies

To enable this parameter, set the Threshold1 mode parameter

to Sticky under or

Hysteresis.

Select threshold mode for the second threshold as one of these options.

Sticky over— Set the threshold status signal toHighwhen the ADC sampled data exceeds the threshold value that you set in the Threshold2 parameter. The threshold status signal remainsHighuntil you set thePLEventsignal in the adcTxChyRealTimeCtrlIn input bus port toHigh.Sticky under— Set the threshold status signal toHighwhen the ADC sampled data remains below the threshold value, which you set in the Threshold2 parameter, for the number of samples that you set in the Number of sample(s) below threshold2 parameter. The threshold status signal remainsHighuntil you set thePLEventsignal in the adcTxChyRealTimeCtrlIn input bus port toHigh.Hysteresis— Set the threshold status signal toHighwhen the ADC sampled data exceeds the upper threshold value. Set the threshold status signal toLowwhen the ADC sampled data remains below the lower threshold value for the number of samples that you specify in the Number of sample(s) below threshold2 parameter.

Dependencies

To enable this parameter, select Real-time ports.

Specify the threshold value for the second threshold. For the sticky over threshold mode, this value serves as the upper threshold value. For the sticky under threshold mode, this value serves as the lower threshold value. For the hysteresis threshold mode, specify the threshold values in the format [Tlower Tupper], where Tlower is the lower threshold value and Tupper is the upper threshold value.

Dependencies

To enable this parameter, select Real-time ports.

Specify the number of samples below the threshold value for the second threshold.

Dependencies

To enable this parameter, set the Threshold2 mode parameter

to Sticky under or

Hysteresis.

Frequency Planner

Launch

Specify the DAC channel whose configuration you want to export to the Frequency Planner app. When you open the app from the block mask, it automatically preconfigures itself to match the configuration of the DAC that you specify in this parameter.

The available options for this parameter depend on the DAC channels that you

select on the DAC tab. Specify None if

you do not want the Frequency Planner app to preconfigure itself with the

DAC configuration.

The selection of tiles and the respective DACs is predefined when you set the

RF interface parameter to ADC & DAC 1x1 RF

Interface, ADC & DAC 2x2 RF Interface,

ADC & DAC 4x4 RF Interface, ADC &

DAC 8x8 RF Interface, or ADC & DAC 16x16 RF

Interface. You cannot modify the tile and DAC selection when you

select these predefined options.

Dependencies

To enable this parameter, set the RF interface parameter to

Customize, then clear the Match parameters of

all DACs parameter on the DAC tab.

Specify the ADC channel whose configuration you want to export to the Frequency Planner app. When you open the app from the block mask, it automatically preconfigures itself to match the configuration of the ADC that you specify in this parameter.

The available options for this parameter depend on the ADC channels that you

select on the ADC tab. Specify None if

you do not want the Frequency Planner app to preconfigure itself with the

ADC configuration.

The selection of tiles and the respective ADCs is predefined when you set the

RF interface parameter to ADC & DAC 1x1 RF

Interface, ADC & DAC 2x2 RF Interface,

ADC & DAC 4x4 RF Interface, ADC &

DAC 8x8 RF Interface, or ADC & DAC 16x16 RF

Interface. You cannot modify the tile and ADC selection when you

select these predefined options.

Dependencies

To enable this parameter, set the RF interface parameter to

Customize, then clear the Match parameters of

all ADCs parameter on the ADC tab.

Launch the Frequency Planner app, configured to match the settings of the selected DAC and ADC channels.

Note

When you set Digital interface to

Real, the app does not automatically configure the

Samples per clock cycle values to match the block. For real

data, you must manually set the Samples per clock cycle values

in the app.

Import

Specify the DAC channel whose parameters must align with the corresponding values in the Frequency Planner app when imported as a MAT file. The available options for this parameter depend on the values of the RF interface and Match parameters of all DACs parameters.

All channels— Align the parameters of all DAC channels with the corresponding values from the configuration imported via a MAT file.None— Do not align any DAC channel parameters with the values from the configuration imported via a MAT file.DAC channels — Select the DAC channels whose parameters you want to align with the corresponding values from the configuration imported via a MAT file.

To enable selection of DAC channels, set the RF interface parameter to

Customize, then clear the Match parameters of all DACs parameter on the DAC tab.

Specify the ADC channel whose parameters must align with the corresponding values in the Frequency Planner app when imported as a MAT file. The available options for this parameter depend on the values of the RF interface and Match parameters of all ADCs parameters.

All channels— Align the parameters of all ADC channels with the corresponding values from the configuration imported via a MAT file.None— Do not align any ADC channel parameters with the values from the configuration imported via a MAT file.ADC channels — Select the ADC channels whose parameters you want to align with the corresponding values from the configuration imported via a MAT file.

To enable selection of ADC channels, set the RF interface parameter to

Customize, then clear the Match parameters of all ADCs parameter on the ADC tab.

Import the DAC and ADC configuration saved in a MAT file. The block automatically aligns this configuration with the corresponding parameters of the selected DAC and ADC channels.

More About

In general, the interface from the hardware logic to the ADC and DAC operates at a single sample per clock cycle. However, the RF Data Converter block can operate on single or multiple samples per clock cycle, where each sample is of 16 bits. You must select the number of samples per clock cycle based on your input data.

For example, to send four samples per clock cycle, first concatenate these samples.

Then, provide the concatenation as a 64-bit input to the block and set the Samples

per clock cycle parameter to 4. The block outputs 64-bit

data, which comprises four 16-bit samples.

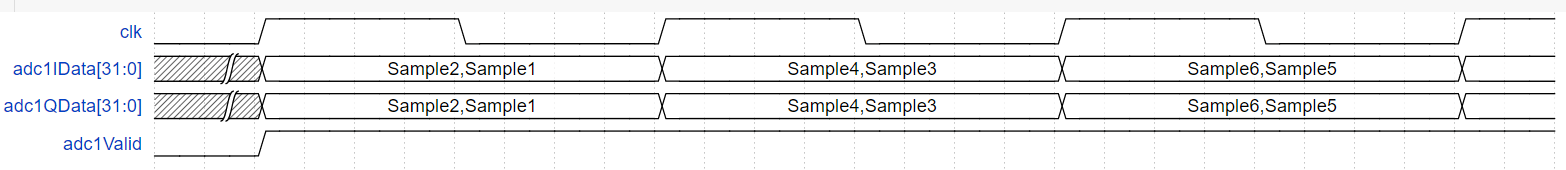

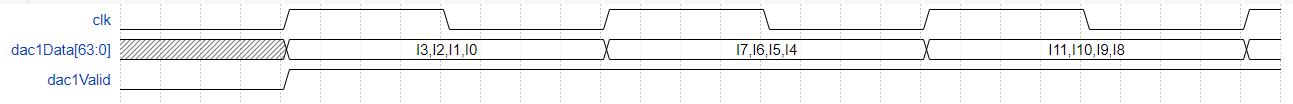

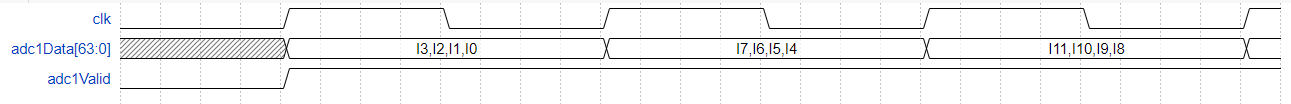

These figures show the input format to the DAC and the output format from the ADC when

the RF interface parameter is set to ADC & DAC 1x1 RF

Interface and the Digital interface parameter is set to

Real.

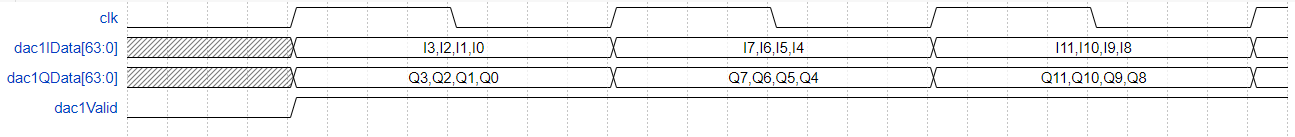

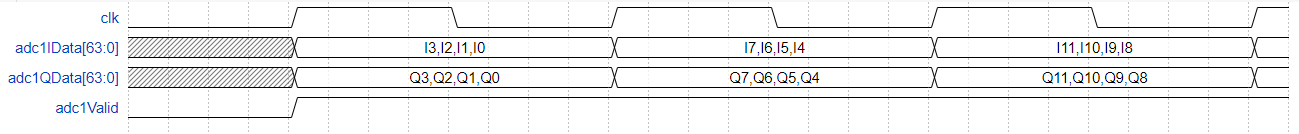

These figures show the input format to the DAC and the output format from the ADC when

the RF interface parameter is set to ADC & DAC 1x1 RF

Interface and the Digital interface parameter is set to

I/Q.

Extended Capabilities

To automatically generate HDL code for your design and execute on an SoC device, use the SoC Builder tool.

Version History

Introduced in R2020aThe block now supports the Frequency Planner tab. Use this tab to open the Frequency Planner app with settings that match the selected DAC and ADC channels. You can also import a MAT file to apply saved DAC and ADC configuration to the selected channels.

The block now supports the Zynq UltraScale+ RFSoC DFE devices. For a full list of supported devices, see Supported RFSoC Devices for RF Data Converter.

The block now supports the behavioral simulation of the real-time ports for the DACs and ADCs.

The block now supports the simulation capability. Open the block mask and select one of these simulation modes.

Pass-through (default) — In this simulation mode, the block outputs the same data as the input. The interpolation, decimation, and mixers settings do not impact the input data while the block computes output values.

Behavioral — In this simulation mode, the interpolation, decimation, and mixers settings impact the input data while the block computes output values.

Support for more than eight samples per clock cycle — Before R2022a, the block supports a maximum of eight samples per clock cycle. Starting from R2022a, the block supports a maximum of 16 samples per clock cycle for DACs and ADCs.

Support for real-time NCO ports — The block now supports real-time NCO ports for DACs and ADCs.

Support for real-time ports — The block now supports real-time ports for ADCs.

Support for I/Q digital interface for ZCU208 board — The block now supports the I/Q digital interface for the Xilinx Zynq UltraScale+ RFSoC ZCU208 Evaluation Kit.

Starting from R2021a, you can use an external PLL clock source to provide ADC and DAC clocks for each tile. To use this feature, select the External PLL parameter of the RF Data Converter block.

Starting from R2021a, the RF Data Converter block supports these generations of Zynq UltraScale+ RFSoC devices. For a full list of supported devices, see Supported RFSoC Devices for RF Data Converter.

| Generation | Device |

|---|---|

Gen 1 | ZU25DR |

ZU27DR | |

ZU29DR | |

Gen 2 | ZU39DR |

Gen 3 | ZU47DR |

ZU48DR | |

ZU49DR |

In R2020a, the RF Data Converter block has two valid ports

adcxIValid and

adcxQValid corresponding to I and Q

data ports adcxIData

and adcxQdata,

respectively.

In R2020b, the two valid output ports

adcxIValid and

adcxQValid are removed and replaced

with one output port adcxValid that

corresponds to both I and Q data ports. When you open a model containing an RF Data

Converter block that was created in R2020a and has its Digital

interface parameter set to I/Q, the output ports of

the block might not be correctly connected.

In this case, manually check and correct the port connections in your model to proceed further.

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

选择网站

选择网站以获取翻译的可用内容,以及查看当地活动和优惠。根据您的位置,我们建议您选择:。

您也可以从以下列表中选择网站:

如何获得最佳网站性能

选择中国网站(中文或英文)以获得最佳网站性能。其他 MathWorks 国家/地区网站并未针对您所在位置的访问进行优化。

美洲

- América Latina (Español)

- Canada (English)

- United States (English)

欧洲

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)