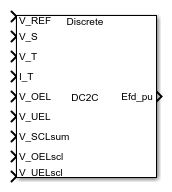

SM DC2C

Discrete- or continuous-time synchronous machine DC2C or DC2A excitation system including an automatic voltage regulator and an exciter

Libraries:

Simscape /

Electrical /

Control /

SM Control

Description

The SM DC2C block implements a synchronous machine (SM) DC2C excitation system model in conformance with IEEE Std 421.5-2016 [1]. You can also use the SM DC2C block to implement an DC2A model from previous versions of IEEE Std 421.5 [2-3]. For more information about implementing an DC2A model, see DC2A Model.

Use this block to model the control and regulation of the field voltage of a synchronous machine that operates as a generator using a DC commutator rotating exciter.

You can switch between continuous and discrete implementations of the block by using the

Sample time (-1 for inherited) parameter. To configure the

integrator for continuous time, set the Sample time (-1 for

inherited) property to 0. To configure the integrator

for discrete time, set the Sample time (-1 for inherited) property

to a positive, nonzero value, or to -1 to inherit the sample time

from an upstream block.

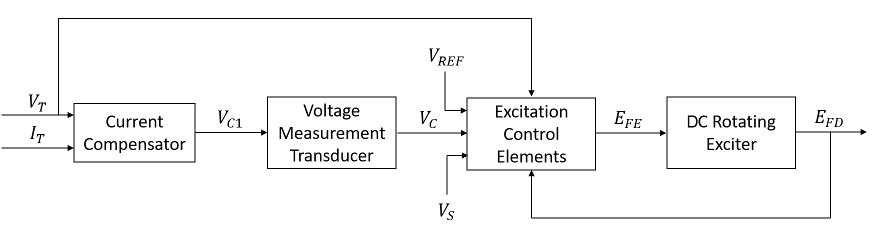

The SM DC2C block is made up of four major components:

The current compensator modifies the measured terminal voltage as a function of terminal current.

The voltage measurement transducer simulates the dynamics of a terminal voltage transducer by using a low-pass filter.

The excitation control elements component compares the voltage transducer output with a terminal voltage reference to produce a voltage error. This voltage error is then passed through a voltage regulator to produce the exciter field voltage.

The DC rotating exciter models the DC commutator rotating exciter and produces a field voltage that is applied to the controlled synchronous machine. The block also feeds the field voltage back to the excitation system.

This diagram shows the overall structure of the DC2C excitation system model:

In the diagram:

VT and IT are the measured terminal voltage and current of the synchronous machine.

VC1 is the current-compensated terminal voltage.

VC is the filtered, current-compensated terminal voltage.

VREF is the reference terminal voltage.

VS is the power system stabilizer voltage.

EFE is the exciter field voltage.

EFD is the field voltage.

The following sections describe each of the major parts of the block in detail.

Current Compensator and Voltage Measurement Transducer

The current compensator is modeled as:

where:

RC is the load compensation resistance.

XC is the load compensation reactance.

The voltage measurement transducer is implemented as a Low-Pass Filter block with the time constant TR. Refer to the documentation for this block for the exact discrete and continuous implementations.

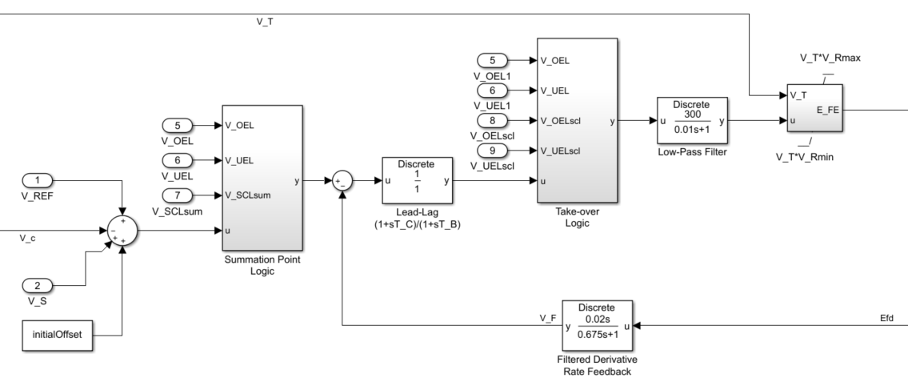

Excitation Control Elements

This diagram illustrates the overall structure of the excitation control elements:

In the diagram:

The Summation Point Logic subsystem models the summation point input location for the overexcitation limiter (OEL), underexcitation limiter (UEL), and stator current limiter (SCL) voltages. For more information about using limiters with this block, see Field Current Limiters.

The Lead-Lag block models additional dynamics associated with the voltage regulator. Here, TC is the lead time constant and TB is the lag time constant. Refer to the Lead-Lag block documentation for the exact discrete and continuous implementations.

The Low-Pass Filter block models the major dynamics of the voltage regulator. Here, KA is the regulator gain and TA is the major time constant of the regulator. The minimum and maximum anti-windup saturation limits for the block are VRmin and VRmax, respectively.

The Take-over Logic subsystem models the take-over point input location for the OEL, UEL, and SCL voltages. For more information about using limiters with this block, see Field Current Limiters.

The Filtered Derivative block models the rate feedback path for stabilization of the excitation system. Here, KF and TF are the gain and time constant of this system, respectively. Refer to the documentation for the Filtered Derivative block for the exact discrete and continuous implementations.

VT*VRmax and VT*VRmin are the minimum and maximum saturation limits for the output exciter field voltage EFE.

Field Current Limiters

You can use various field current limiters to modify the output of the voltage regulator under unsafe operating conditions:

Use an overexcitation limiter to prevent overheating of the field winding due to excessive field current demand.

Use an underexcitation limiter to boost field excitation when it is too low, which can risk desynchronization.

Use a stator current limiter to prevent overheating of the stator windings due to excessive current.

Attach the output of any of these limiters at one of these points:

The summation point as part of the automatic voltage regulator (AVR) feedback loop

The take-over point to override the usual behavior of the AVR

If you are using the stator current limiter at the summation point, use the single input VSCLsum. If you are using the stator current limiter at the take-over point, use both an overexcitation input VOELscl and an underexcitation input VUELscl.

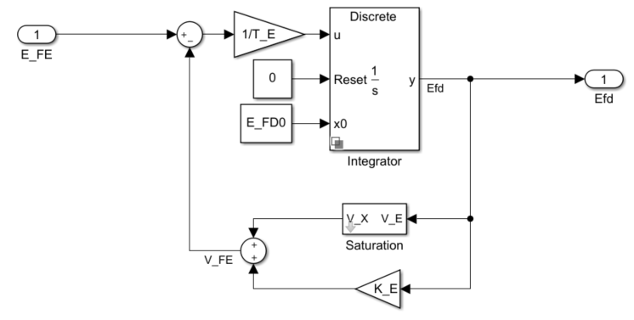

DC Rotating Exciter

This diagram illustrates the overall structure of the DC commutator rotating exciter:

In the diagram:

The exciter field current VFE is modeled as the summation of two signals:

The nonlinear function Vx models the saturation of the exciter output voltage.

The proportional term KE models the linear relationship between exciter output voltage and the exciter field current.

The Integrator subsystem integrates the difference between EFE and VFE to generate the output field voltage Efd. TE is the time constant for this process.

DC2A Model

You can represent existing DC2A excitation systems using the DC2C model. The DC2C model introduced a lower limit for the field voltage. The model also introduced additional options for the OEL and SCL input locations. To implement a DC2A model using the SM DC2C block, set the parameters to the values shown in this table. The default block parameter values satisfy these conditions.

| Block Parameter | Parameter Value |

|---|---|

| Lower limit, E_FDmin (pu) | -99 |

| Alternate OEL input locations (V_OEL) | Unused |

| Alternate SCL input locations (V_SCL) | Unused |

Ports

Input

Output

Parameters

References

[1] “IEEE Recommended Practice for Excitation System Models for Power System Stability Studies.” IEEE Std 421.5-2016 (Revision of IEEE Std 421.5-2005), August 2016, 1–207. https://doi.org/10.1109/IEEESTD.2016.7553421.

[2] “IEEE Recommended Practice for Excitation System Models for Power System Stability Studies.” IEEE Std 421.5-2005 (Revision of IEEE Std 421.5-1992), April 2006, 1–93. https://doi.org/10.1109/IEEESTD.2006.99499.

[3] “IEEE Recommended Practice for Excitation System Models for Power System Stability Studies.” IEEE Std 421.5-1992, August 1992, 1–56. https://doi.org/10.1109/IEEESTD.1992.106975.

Extended Capabilities

Version History

Introduced in R2020a