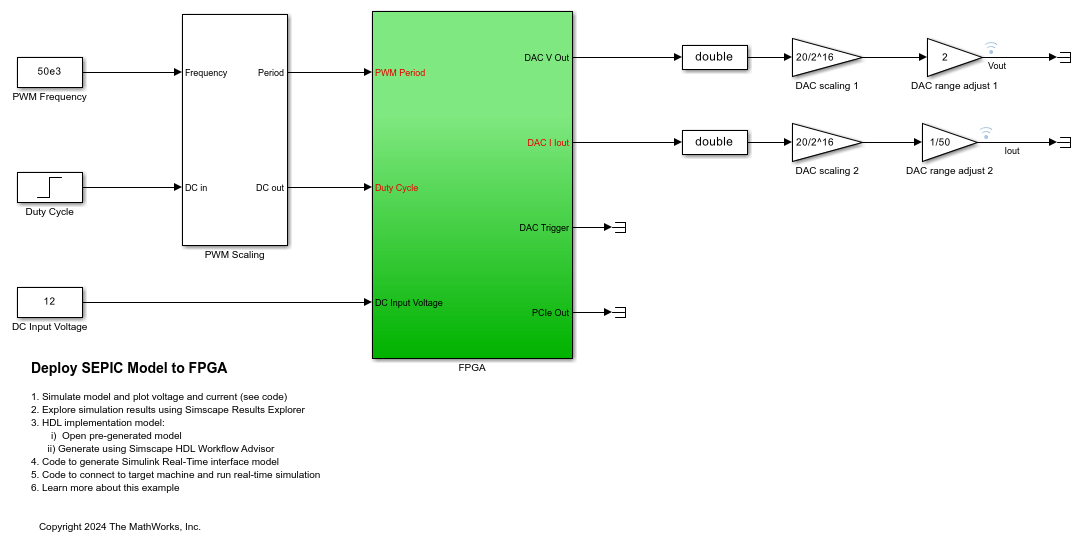

Deploy SEPIC Model to FPGA

This example shows how to deploy a single-ended primary-inductor converter (SEPIC) model to a Speedgoat® IO334-325K Simulink®-programmable I/O module and then run the model in real-time at a sample step size of 1 microsecond. The parts of the model that you deploy to CPU, run at 50 microseconds.

To deploy the SEPIC model to FPGA follow these steps:

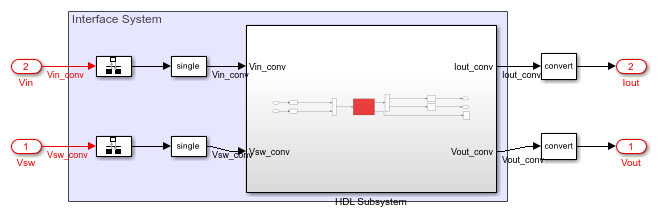

Convert the Simscape™ model into an HDL-compatible implementation model by using the Simscape HDL Workflow Advisor.

Generate HDL code and FPGA bitstream for the IO334-325K module by using the HDL Workflow Advisor.

Deploy the real-time model to the Speedgoat real-time target machine by using Simulink Real-Time™.

Model

Simscape SEPIC Model

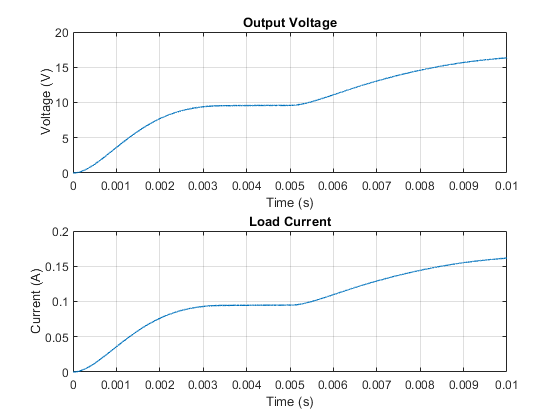

Simscape Simulation Results

The plot below shows the requested and measured output voltage for the test and the load current in the circuit.

HDL Implementation Model

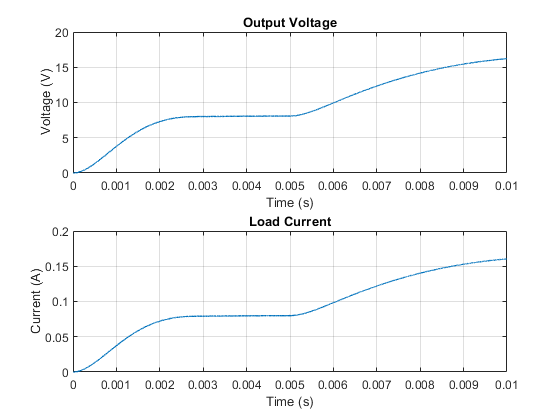

Simulation of HDL Implementation Model

The plot below shows the requested and measured output voltage for the test and the load current in the circuit.