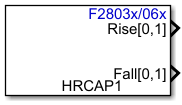

HRCAP

Capture pulse width in normal or high resolution modes for F2803x and F2806x processors

Since R2023b

Libraries:

C2000 Microcontroller Blockset /

C2803x

C2000 Microcontroller Blockset /

C2806x

Description

Use the high resolution capture (HRCAP) block to capture the pulse width in the normal or high resolution modes and perform conventional and high resolution delta time measurements. The block uses the HRCAP type 0 module for F2803x and F2806x processors.

Note

You can enable high resolution mode (HRCAP mode) using eCAP block for TI F28002x, F28003x, F28004x, F2838x, F28P55x, and F28P65x processors. For more, see C28x/C29x eCAP

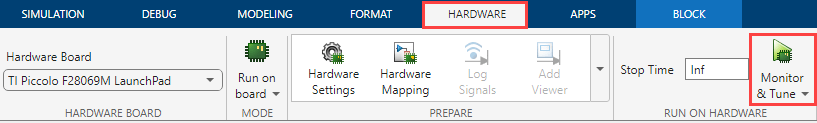

You can operate the block in normal or high resolution mode. In high resolution mode, the calibration function uses additional HRCAP and HRPWM modules internally in the ePWM module. The block supports only the PLL clock in the high resolution mode and uses the PLLCLK or PLL2CLK as the PLL clock source based on the processor.

The block does not support SYSCLK in the high resolution mode. For the block to calibrate the output, the clock frequency has to be higher than 98 MHz, and the maximum SYSCLK frequency for the F2806x is 90MHz and F2803x boards is 60MHz.

For high resolution mode, only PLL clock is supported and clock frequency should be in the range between 98 to 120 MHz for calibration.

Output in high resolution mode will be in counts of HCCAPCLK (16-bit HRCAP clock) cycles in Q16 format and output in normal mode will be vector outputs for rise (0,1) and fall (0,1) signals which can be in microseconds or HRCAPCLK cycles.

Examples

Ports

Output

Parameters

Version History

Introduced in R2023b