Pixel Stream FIFO

Buffer input stream to create image lines that have contiguous valid pixels

Libraries:

Vision HDL Toolbox /

Utilities

Description

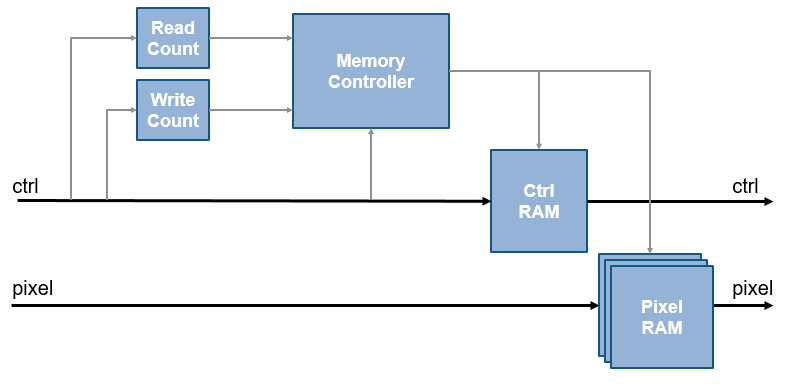

The Pixel Stream FIFO block stores incoming valid pixels and accompanying control signals and returns the same pixel stream without gaps between the valid pixels of each line. The block preserves the total line size and total frame size of the video stream, including invalid cycles.

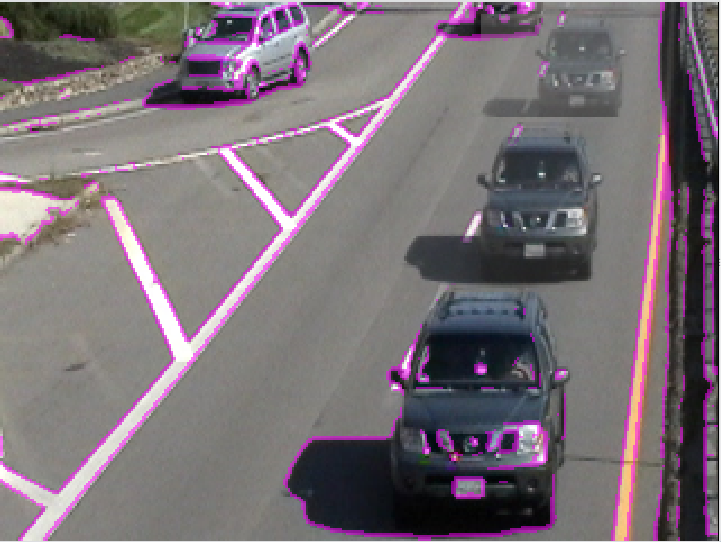

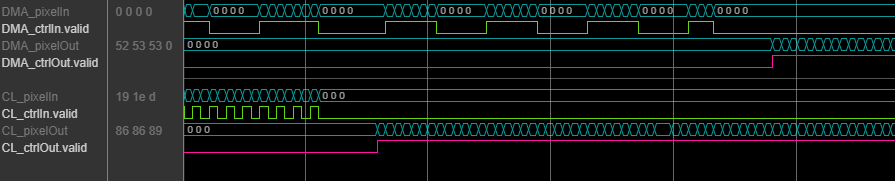

Use the Pixel Stream FIFO block to buffer video sources. The waveform shows a direct memory access (DMA) video source, where pixels are read in bursts, and a Camera Link® video source, where pixels are valid every second clock cycle. To create contiguous video lines, a Pixel Stream FIFO block buffers the input pixels and control signals of each source.

Examples

Ports

This block uses a streaming pixel interface with a bus for

frame control signals. This interface enables the block to operate independently of image size

and format. The pixel ports on this block support single pixel streaming or

multipixel streaming. Single pixel streaming accepts and returns a single pixel value each clock

cycle. Multipixel streaming accepts and returns a vector of M pixels per

clock cycle to support high-frame-rate or high-resolution formats. The M

value corresponds to the Number of pixels parameter of the Frame

To Pixels block. Along with the pixel, the block accepts and returns a

pixelcontrol bus that contains five control signals. The control signals

indicate the validity of each pixel and their location in the frame. For multipixel streaming,

one set of control signals applies to all pixels in the vector. To convert a frame (pixel

matrix) into a serial pixel stream and control signals, use the Frame

To Pixels block. For a full description of the interface, see Streaming Pixel Interface.

This block also supports multipixel-multicomponent streams, where the pixel input is a matrix of M-by-N values. M is number of pixels and N is number of components. These values correspond to the Number of pixels and Number of components parameters of the Frame To Pixels block.