RS Encoder

Encode message to RS codeword

Libraries:

Wireless HDL Toolbox /

Error Detection and Correction

Description

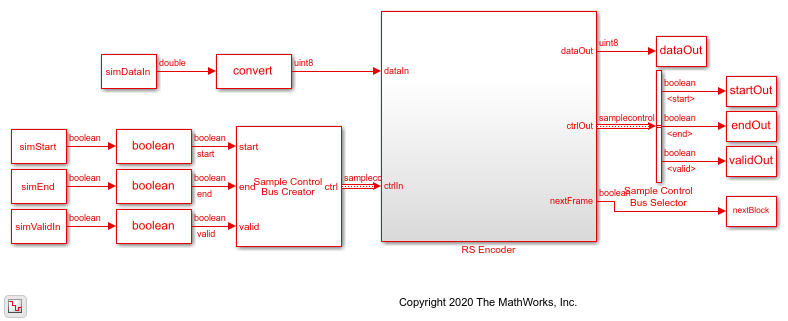

The RS Encoder block encodes message data to a Reed-Solomon (RS) codeword.

The block accepts message data and a samplecontrol bus and outputs codeword

data symbols and a samplecontrol bus.

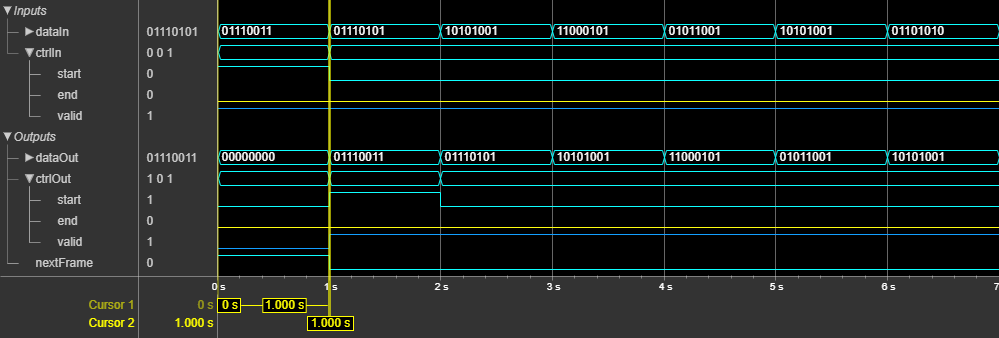

Because the latency of the block varies, the block provides output port nextFrame that indicates when the block is ready to accept new input message data. The block provides an architecture suitable for HDL code generation and hardware deployment and supports shortened message lengths.

You can use this block to model many communication system forward error correcting (FEC) codes. The block supports digital subscriber line (DSL), WiMAX (802.16 m and e), digital video broadcast handheld (DVB-H) terminals, digital video broadcast satellite (DVB-S) services, and digital video broadcast satellite services to handheld (DVB-SH) devices below 3 MHz.

Examples

Ports

Input

Output

Parameters

Algorithms

References

[1] Wicker, Stephen B. Error Control Systems for Digital Communication and Storage. Englewood Cliffs, NJ: Prentice Hall, 1995.

[2] Clark, George C., and J. Bibb Cain. Error-Correction Coding for Digital Communications. Applications of Communications Theory. New York: Plenum Press, 1981.

Extended Capabilities

Version History

Introduced in R2020b