HDL-Optimized System Design

These blocks implement hardware-friendly architectures and support HDL code generation when used with HDL Coder™. The blocks on this page also have streaming interfaces that process a single sample or a vector of samples at a time, hardware control signals, and options to select different hardware implementations of their algorithms.

Blocks

| CCSDS RS Encoder | Encode message into RS codeword according to CCSDS standard (Since R2022a) |

| CCSDS RS Decoder | Decode and recover message from RS codeword according to CCSDS standard (Since R2021b) |

| CCSDS LDPC Decoder | Decode LDPC code according to CCSDS standard (Since R2022b) |

| CCSDS LDPC Encoder | Encode data with LDPC code according to CCSDS Telemetry standard (Since R2025a) |

| DVB-S2 BCH Decoder | Decode and recover message from BCH codeword according to DVB-S2 standard (Since R2022a) |

| DVB-S2 LDPC Decoder | Decode LDPC code according to DVB-S2 standard (Since R2022a) |

| NR LDPC Encoder | Perform LDPC encoding according to 5G NR standard |

| NR LDPC Decoder | Decode LDPC code according to 5G NR standard |

| NR Polar Encoder | Perform polar encoding according to 5G NR standard |

| NR Polar Decoder | Perform polar decoding according to 5G NR standard |

| WLAN LDPC Decoder | Decode LDPC code according to WLAN standard (Since R2021b) |

| RS Encoder | Encode message to RS codeword |

| RS Decoder | Decode and recover message from RS codeword |

| LDPC Encoder | Encode data with quasi-cyclic low-density parity-check code (Since R2023a) |

| LDPC Decoder | Decode quasi-cyclic low-density parity-check code (Since R2023b) |

| APP Decoder | Decode convolutionally-coded LLR values using MAP algorithm (Since R2021b) |

| LTE Convolutional Encoder | Encode binary samples using tail-biting convolutional algorithm |

| LTE Convolutional Decoder | Decode convolutional-encoded samples using Viterbi algorithm |

| LTE Turbo Encoder | Encode binary samples using turbo algorithm |

| LTE Turbo Decoder | Decode turbo-encoded samples |

| Convolutional Encoder | Encode data bits using convolution coding — optimized for HDL code generation |

| Puncturer | Puncture data according to puncture vector |

| Depuncturer | Reverse puncturing scheme to prepare for decoding |

| Viterbi Decoder | Decode convolutionally encoded data using Viterbi algorithm |

| LTE CRC Encoder | Generate checksum and append to input sample stream |

| LTE CRC Decoder | Detect errors in input samples using checksum |

| NR CRC Encoder | Generate CRC code bits and append them to input data |

| NR CRC Decoder | Detect errors in input data using CRC |

| DVB-S2 Symbol Demodulator | Demodulate complex constellation symbol to set of LLR values or data bits according to DVB-S2 standard (Since R2021b) |

| DVB-S2 Symbol Modulator | Modulate data bits to complex constellation symbols according to DVB-S2 standard (Since R2022b) |

| LTE OFDM Modulator | Modulate LTE resource grid and return time-domain OFDM samples |

| LTE OFDM Demodulator | Demodulate time-domain OFDM samples and return LTE resource grid |

| LTE Symbol Modulator | Modulate data bits to complex LTE data symbols |

| LTE Symbol Demodulator | Demodulate complex LTE data symbols to data bits or LLR values |

| NR Symbol Modulator | Modulate data bits to complex NR data symbols |

| NR Symbol Demodulator | Demodulate complex NR data symbols to data bits or LLR values |

| FFT 1536 | Computes fast-fourier-transform (FFT) for LTE standard transmission bandwidth of 15 MHz |

| Frequency Estimator | Estimate carrier frequency offset (CFO) using open-loop approach (Since R2026a) |

| OFDM Channel Estimator | Estimate channel using input data and reference subcarriers |

| OFDM Equalizer | Equalize OFDM data using channel estimates |

| OFDM Modulator | Modulate frequency-domain OFDM subcarriers to time-domain samples for custom communication protocols |

| OFDM Demodulator | Demodulate time-domain OFDM samples and return subcarriers for custom communication protocols |

| Symbol Demodulator | Demodulate complex constellation symbol to set of LLR values or data bits (Since R2022a) |

| Symbol Modulator | Modulate data bits to complex data symbols (Since R2025a) |

| GMSK Modulator | Modulate data bits using Gaussian minimum shift keying (GMSK) method (Since R2024a) |

| GMSK Demodulator | Demodulate GMSK-modulated symbols to set of LLR values or bits (Since R2026a) |

| LTE Gold Sequence Generator | Generate Gold sequence |

| WGN Generator | Generate white Gaussian noise samples (Since R2026a) |

Featured Examples

Sample Rate Conversion for an LTE Receiver

Implement sample rate converter for LTE receiver front end.

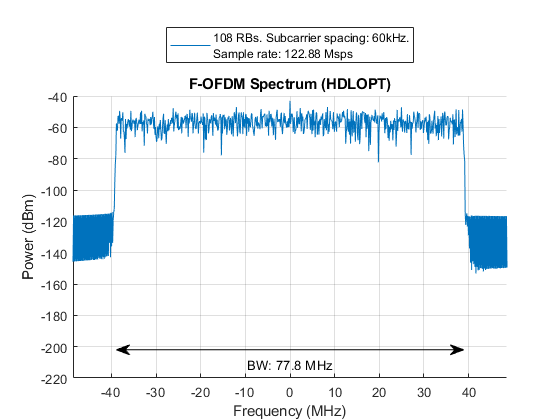

HDL Code Generation for Filtered OFDM (F-OFDM) Transmitter

Filter symbols after IFFT to improve bandwidth while maintaining orthogonality.

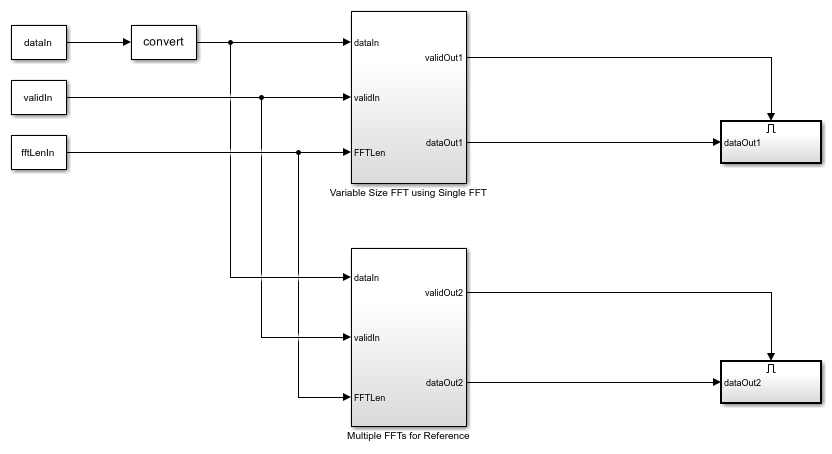

HDL Implementation of Variable-Size FFT

Implement variable-size FFT by using single FFT core.

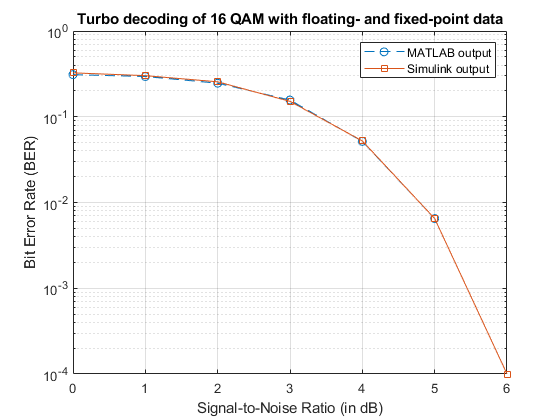

Accelerate BER Measurement for Wireless HDL LTE Turbo Decoder

Measure BER of LTE Turbo Decoder block using parsim to parallelize simulations across EbNo points.

HDL Implementation of AWGN Generator

Implement AWGN generator that is optimized for HDL code generation and hardware implementation.

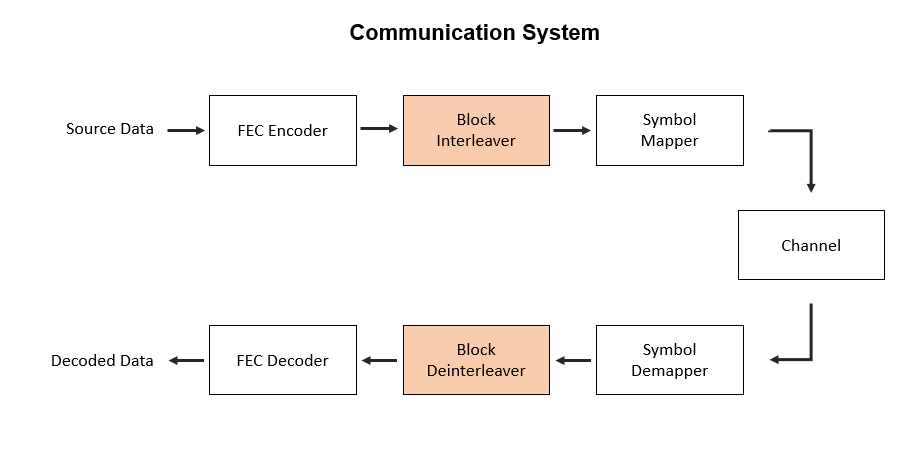

HDL Interleaver and Deinterleaver

Design and implement interleaving and deinterleaving in communication systems.

HDL Implementation of Digital Predistorter

Implement Digital Predistorter that is optimized for HDL code generation and hardware implementation.

HDL Implementation of Digital Predistorter with LMS Coefficient Estimation

Implement DPD with LMS coefficients and pre-calculated coefficients optimized for HDL code generation.

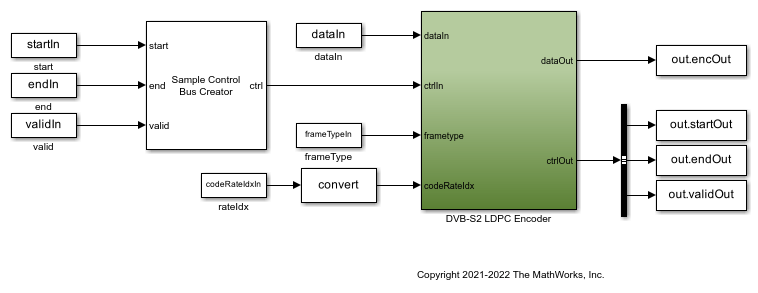

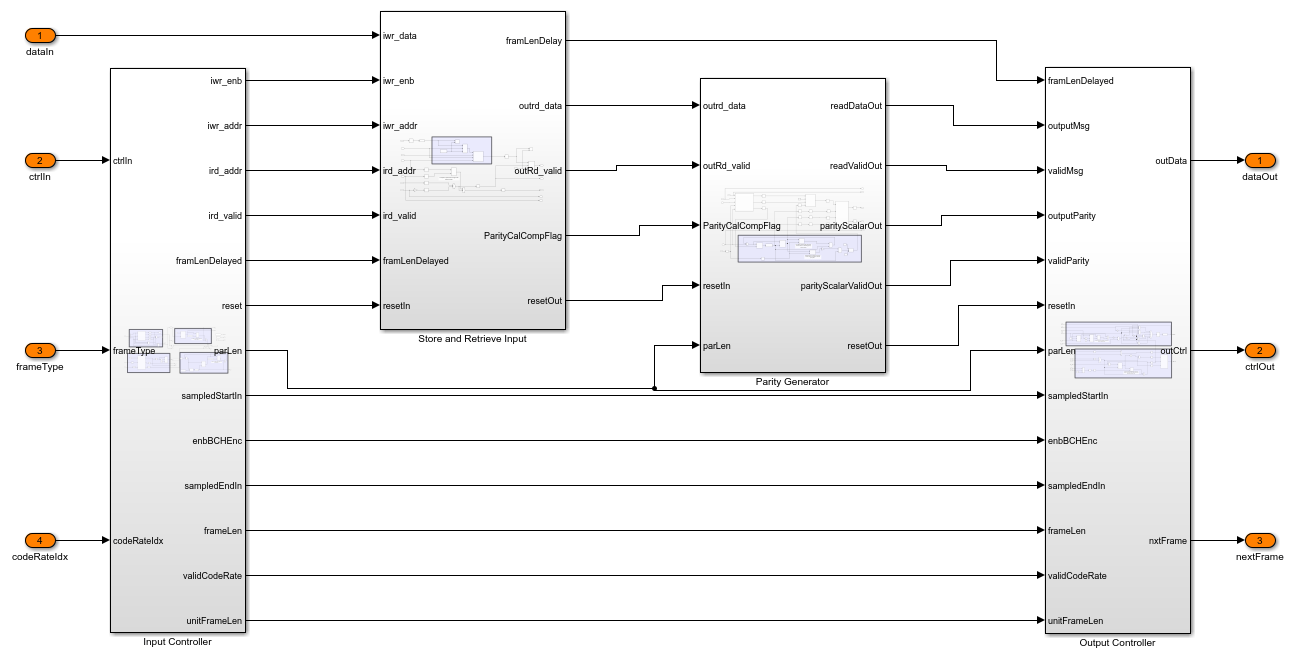

DVB-S2 HDL LDPC Encoder

Implement DVB-S2 LDPC encoding using Simulink® blocks that are optimized for HDL code generation.

DVB-S2 HDL BCH Encoder

Implement DVB-S2 BCH encoder using Simulink® blocks that are optimized for HDL code generation.

WLAN HDL LDPC Encoder

Implement WLAN LDPC encoder using Simulink® blocks that are optimized for HDL code generation.

HDL Digital Automatic Gain Control for Single and Multicarrier Systems

Implement digital AGC for single-carrier and multicarrier systems using Simulink® blocks optimized for HDL code generation.

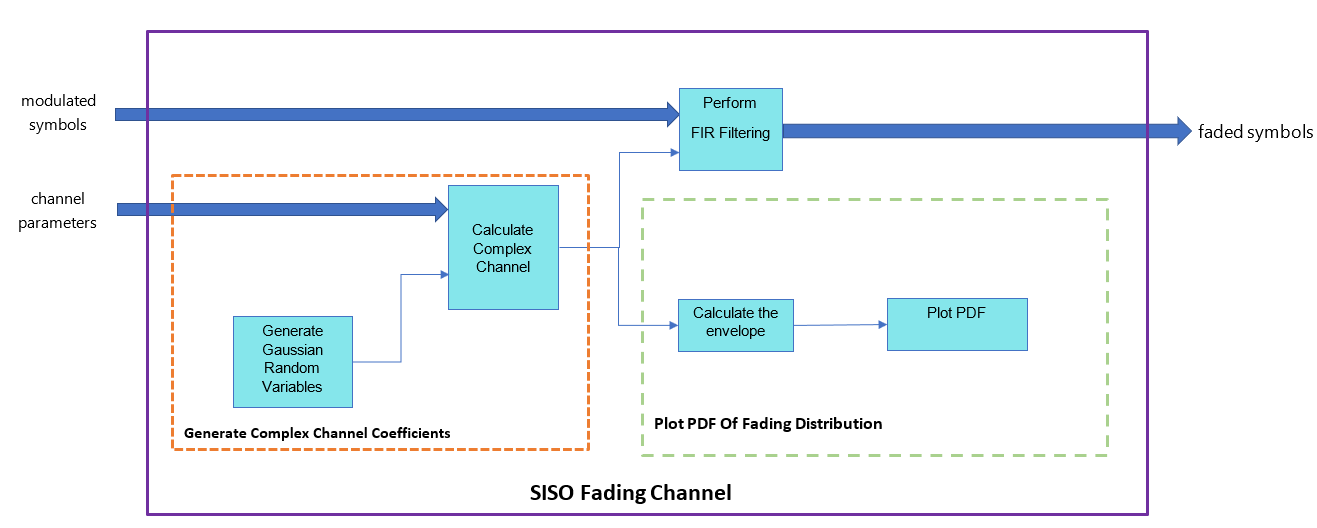

HDL Implementation of Fading Channel

Use SISO fading channel to evaluate performance of wireless communication systems over Rayleigh and Rician fading channels.

Parallel Concatenation Using APP Decoder

Decode parallel concatenated convolution codes using APP Decoder block.

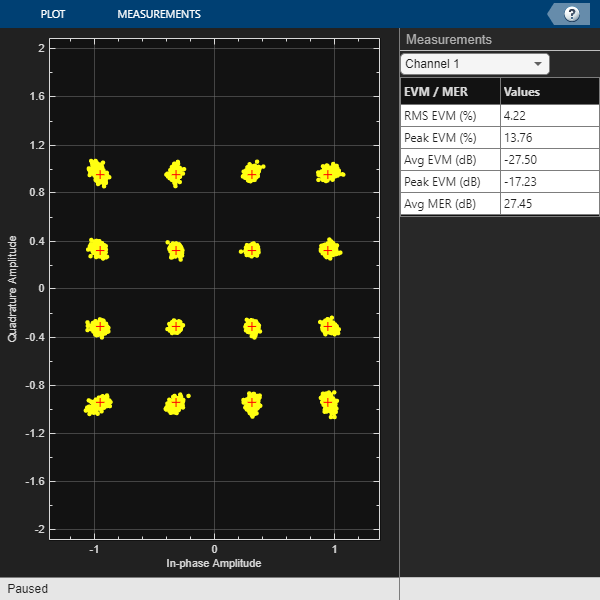

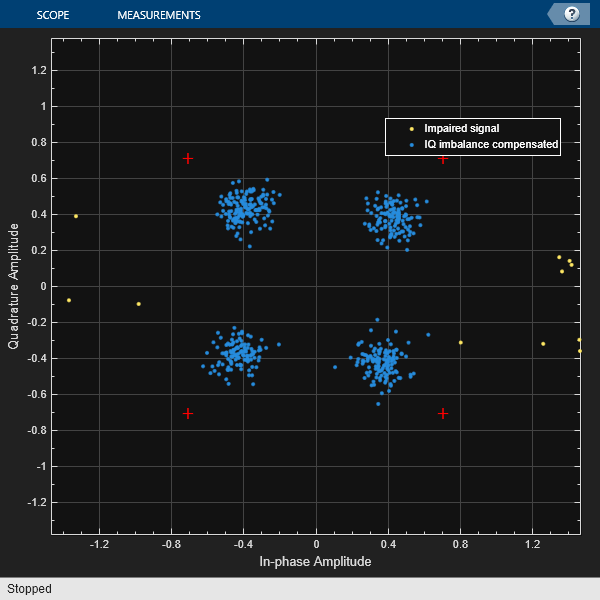

HDL Implementation of IQ Imbalance Estimation and Compensation

Implement IQ imbalance estimation and compensation on QAM/PSK modulated signals.

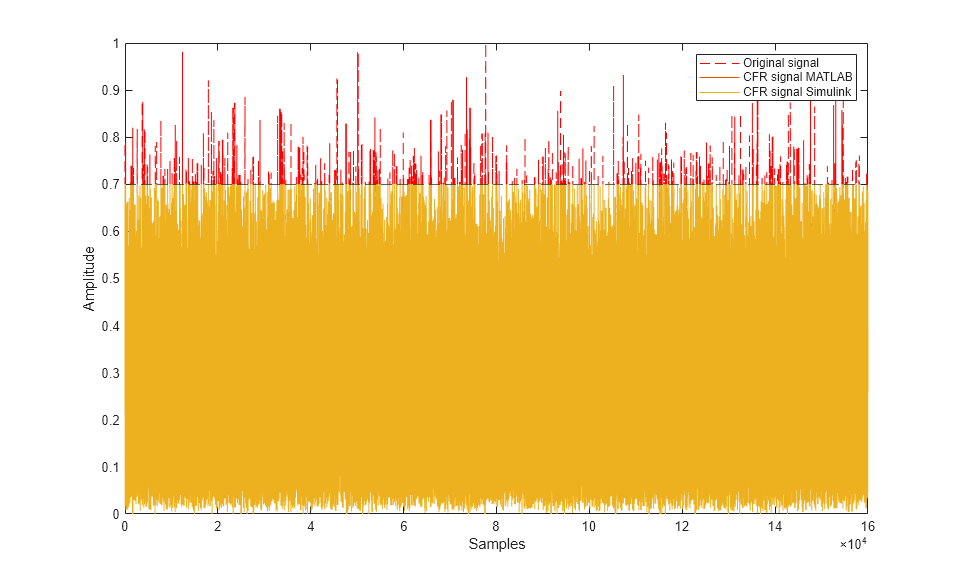

Improve Power Amplifier Efficiency Using Crest Factor Reduction

Implement CFR technique in OFDM communication.

- Since R2025a

- Open Script

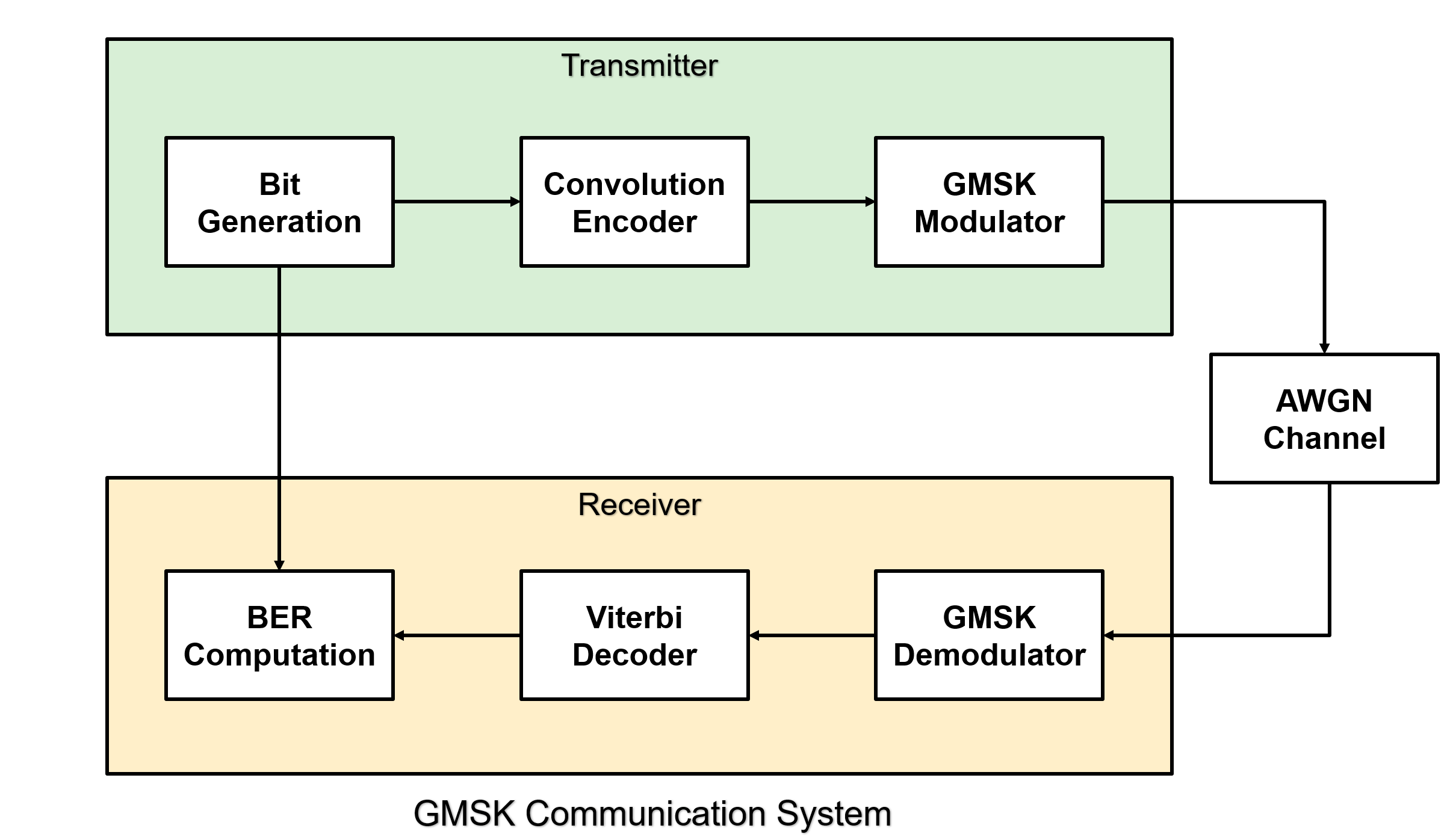

Accelerate BER Simulations of GMSK System Using FPGA-in-the-Loop Workflow

Accelerate BER simulations of GMSK system using FPGA-in-loop workflow.

- Since R2026a

- Open Live Script

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

选择网站

选择网站以获取翻译的可用内容,以及查看当地活动和优惠。根据您的位置,我们建议您选择:。

您也可以从以下列表中选择网站:

如何获得最佳网站性能

选择中国网站(中文或英文)以获得最佳网站性能。其他 MathWorks 国家/地区网站并未针对您所在位置的访问进行优化。

美洲

- América Latina (Español)

- Canada (English)

- United States (English)

欧洲

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)