Symbol Demodulator

Demodulate complex constellation symbol to set of LLR values or data bits

Since R2022a

Libraries:

Wireless HDL Toolbox /

Modulation

Description

The Symbol Demodulator block demodulates a complex constellation symbol to

a set of log-likelihood ratio (LLR) values or data bits. The block accepts equalized complex

data symbols and a samplecontrol bus or a valid signal

and outputs demodulated LLR values or data bits and a samplecontrol bus or

a valid signal based on the selected output type. The block provides an

option to select the output type as vector or scalar and provides an input port to specify the

noise variance.

The block supports BPSK, QPSK, 8-PSK, 16-PSK, 32-PSK, 16-QAM, 64-QAM, and 256-QAM modulations. The number of demodulated LLR values or data bits for a given symbol depends on the modulation type, as shown in this table.

| Modulation Type | Number of LLR Values or Data Bits per Symbol |

|---|---|

| BPSK | 1 |

| QPSK | 2 |

| 8-PSK | 3 |

| 16-PSK | 4 |

| 16-QAM | 4 |

| 32-PSK | 5 |

| 64-QAM | 6 |

| 256-QAM | 8 |

This block provides an interface and architecture for HDL code generation with HDL Coder™. You can use this block in the development of a digital receiver.

Examples

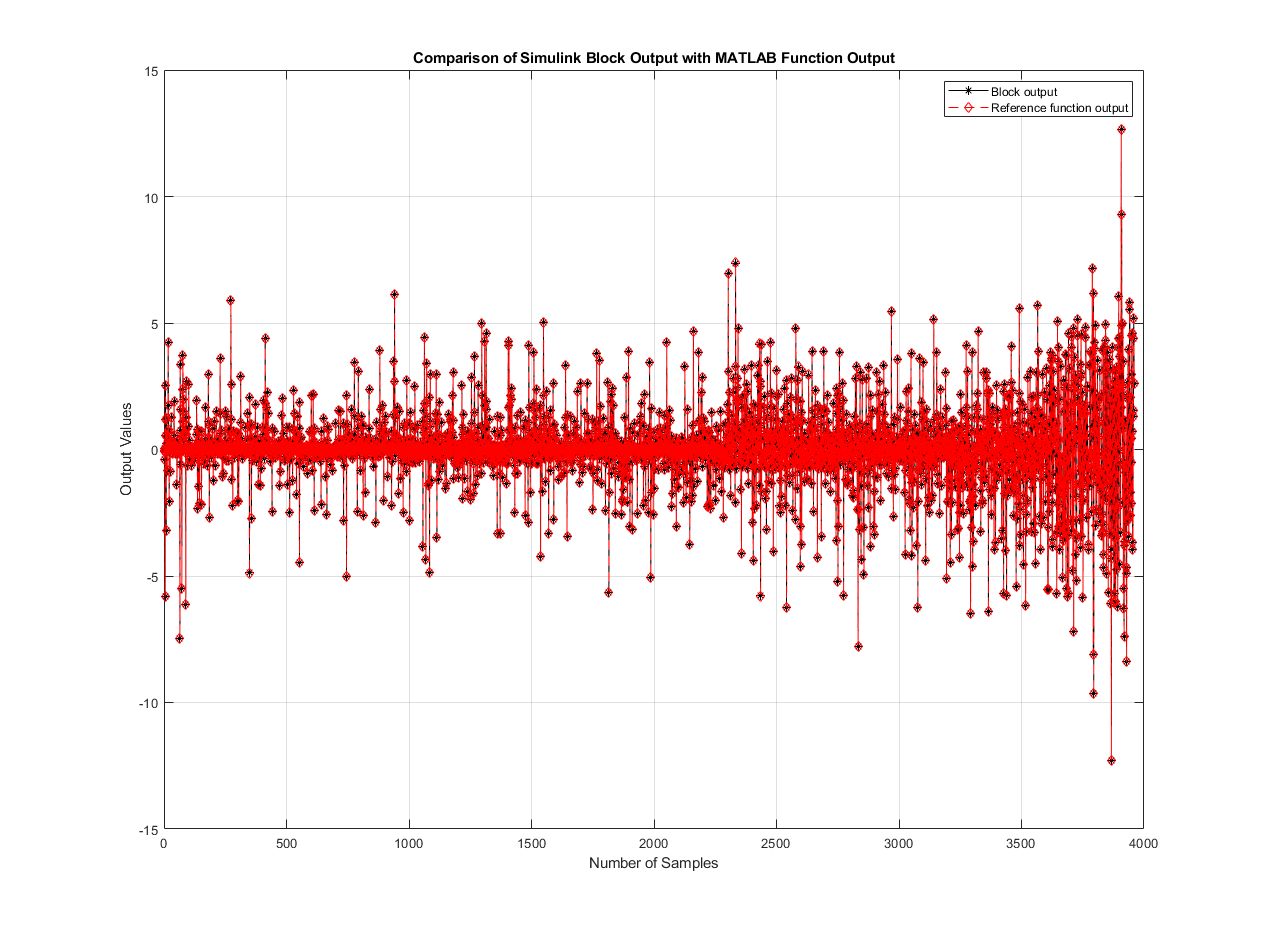

Symbol Demodulation of Complex Data Symbols

Demodulate complex data symbol using Symbol Demodulator block.

Ports

Input

Data symbols, specified as a real- or complex-valued scalar.

double and

single data types are supported for simulation, but not for HDL

code generation.

For HDL code generation, the input data type must be signed fixed

point and the maximum input word length the block supports is 32

bits.

Data Types: single | double | int8 | int16 | int32 | signed fixed point

Complex Number Support: Yes

Control signal that indicates if the input data is valid. When this value is

1 (true), the block accepts the values on the

data input port. When this value is 0

(false), the block ignores the values on the data input

port.

Dependencies

To enable this port, set the Output type parameter to

Scalar.

Data Types: Boolean

Control signals accompanying the sample stream, specified as a

samplecontrol bus. The bus includes the start,

end, and valid control signals, which indicate

the boundaries of the frame and the validity of the samples.

start— Indicates the start of the input frameend— Indicates the end of the input framevalid— Indicates that the data on the input data port is valid

For more detail, see Sample Control Bus.

Dependencies

To enable this port, set the Modulation source parameter to

Input port and set the Output type

parameter to Vector.

Data Types: bus

Modulation selection, specified as 0, 1,

2, 3, 4,

5, 6, or 7. Each value

represents a specific modulation type, as shown in this table.

| Modulation Selection Value | Modulation Type |

|---|---|

0

| BPSK |

1 | QPSK |

2 | 8-PSK |

3 | 16-PSK |

4 | 16-QAM |

5 | 32-PSK |

6 | 64-QAM |

7

| 256-QAM |

If you specify a value other than the values listed in this table or greater than the value specified on the block mask using the Maximum modulation parameter, the block displays a warning message and applies BPSK modulation. The values specified through the modSel port must be with respect to the value set with the Maximum modulation parameter.

For example, if the Maximum modulation parameter is set to

32-PSK, the block allows the modSel

values 0, 1, 2,

3, 4, and 5. For the

modSel values 6 and 7,

the block displays a warning message and applies BPSK modulation.

Dependencies

To enable this port, set the Modulation source parameter to

Input port.

Data Types: single | double | fixdt(0,3,0)

Noise variance, specified as a real-valued positive scalar.

This value must be of data type

fixdt(0,k,m), where

k is less than or equal to 32 and m is less

than or equal to k.

When the Output type parameter is set to

Scalar or Vector, the block

samples the values on this port when the input valid is set to

1.

The software supports double and

single data types for simulation, but not for HDL code generation.

Dependencies

To enable this port, select the Enable noise variance input port parameter.

Data Types: single | double | uint8 | uint16 | unsigned fixed point

Output

Demodulated LLR values or data bits, returned as a scalar when the

Output type parameter is set to

Scalar and as a real-valued column vector when the

Output type parameter is set to

Vector.

If you set the Modulation source parameter to

Property, the output vector size is based on the

Modulation parameter value. If you set the Modulation

source parameter to Input port, the output

vector size is based on the Maximum modulation parameter

value.

When the Decision type parameter is set to

Approximate log-likelihood ratioFor

doubleandsingleinputs, the output data type is same as the input data type.doubleandsingledata types are supported for simulation data types are supported for simulation.For

fixed pointinputs, the block provides the output with an integer bit growth of 4 bits and supports HDL code generation. If the Enable noise variance input port parameter is selected, the integer bit growth of the output is 13 bits.

When the Decision type parameter is set to

Hard, the output data type isBooleanirrespective of the input data type.

Data Types: single | double | Boolean | signed fixed point

Control signals accompanying the sample stream, returned as a

samplecontrol bus. The bus includes the start,

end, and valid control signals, which indicate

the boundaries of the frame and the validity of the samples.

start— Indicates the start of the output frameend— Indicates the end of the output framevalid— Indicates that the data on the output data port is valid

For more detail, see Sample Control Bus.

Dependencies

To enable this port, set the Modulation source parameter to

Input port and set the Output type

parameter to Vector.

Data Types: bus

Control signal that indicates if data from the data output

port is valid. When this value is 1 (true), the block returns valid

data on the data output port. When this value is

0 (false), the values on the data output

port are not valid.

Dependencies

To enable this port:

Set the Modulation source parameter to

Input portorPropertyand set the Output type parameter toScalar.Set the Modulation source parameter to

Propertyand set the Output type parameter toVector.

Data Types: Boolean

Control signal that indicates when the block is ready to accept new input data.

When this value is 1 (true), the block accepts input data in the

next time step. When this value is 0 (false), the block ignores the

input data in the next time step.

The ready signal remains 0 (false) until

the block outputs data of the corresponding input data symbol. The number of clock

cycles that the ready signal remains 0 (false)

depends on the selected modulation type.

Dependencies

To enable this port, set the Output type parameter to

Scalar.

Data Types: Boolean

Parameters

To specify the modulation type from the Modulation parameter,

select Property. To specify the modulation type from the

modIdx port during run time, select Input

port.

Select the modulation type.

Dependencies

To enable this parameter, set the Modulation source parameter

to Property.

Select the maximum modulation type. This parameter value defines the modulation types that the block can support through the modSel port.

For example, when you specify 16-PSK using this

parameter, the number of hardware resources the block generates for the

16-PSK modulation type can accommodate configurations with

BPSK, QPSK, and

8-PSK modulation types specified through the

modSel port, but not configurations with the

16-QAM, 32-PSK,

64-QAM, and 256-QAM modulation

types.

Dependencies

To enable this parameter, set the Modulation source parameter

to Input port.

Select the constellation ordering, that is, how the block assigns binary words to points of the signal constellation.

Default— Specifies default constellation ordering values[2, 3, 1, 0, 6, 7, 5, 4, 14, 15, 13, 12, 10, 11, 9, 8]User defined— Enables you to specify custom constellation ordering values using the Constellation mapping parameter

Dependencies

To enable this parameter, set the Modulation source parameter to

Propertyand set the Modulation parameter to16-QAM,64-QAM, or256-QAM.To enable this parameter, set the Modulation source parameter to

Input portand set the Maximum modulation parameter to16-QAM,64-QAM, or256-QAM.

Specify a unique integer-valued gray-coded row vector corresponding to the modulation type selected using the Modulation parameter or Maximum modulation parameter. The first element of this vector corresponds to the top-leftmost point of the constellation, with subsequent elements running down column-wise, from left to right. The last element corresponds to the bottom rightmost point. For more information on supported gray codes, see Specify Gray Code.

This parameter is specific to the 16-QAM,

64-QAM, and 256-QAM modulation

types.

Dependencies

To enable this parameter, set the Constellation ordering

parameter to User defined.

Select the demapping type.

Approximate log-likelihood ratio— Demap data symbols to LLR values. This LLR value for each bit indicates how likely the bit is1or0.Hard— Demap data symbols to bits1or0.

Select the phase offset. This parameter is specific to the

BPSK, QPSK,

8-PSK, 16-PSK, and

32-PSK modulation types.

Dependencies

To enable this parameter, set the Modulation source parameter to

Propertyand set the Modulation parameter toBPSK,QPSK,8-PSK,16-PSK, or32-PSK.To enable this parameter, set the Modulation source parameter to

Input portirrespective of the modulation types specified for the Maximum modulation parameter.

Select the type of output as Vector or

Scalar.

Vector— Use this option to receive data in vector format from the output data port.When you set the Modulation source parameter to

Property, the output vector size is based on the Modulation parameter value. When you set the Modulation source parameter toInput port, the output vector size is based on the Maximum modulation parameter value.Scalar— Use this option to receive data in scalar format from the output data port.

Select how the block scales the signal constellation.

Unit average power— Normalizes the constellation to unit average powerCustom— Enables you to normalize the constellation by specifying the minimum distance between the constellation points using the Minimum distance between symbols parameter

Note

When you specify 0, 1, 2,

3, or 5 using the modSel

input port, the block ignores this parameter during its operation. This is parameter

is applicable for QAM-based modulations.

Dependencies

To enable this parameter, set the Modulation source parameter to

Propertyand set the Modulation parameter to16-QAM,64-QAM, or256-QAM.To enable this parameter, set the Modulation source parameter to

Input portand set the Maximum modulation parameter to16-QAM,64-QAM, or256-QAM.

Specify the minimum distance between the symbols with the values in the range from 1/32 to 2.

Note

When you specify 0, 1, 2,

3, or 5 using the modSel

input port, the block ignores this parameter during its operation. This parameter is

applicable for QAM-based modulations.

Dependencies

To enable this parameter, set the Normalization method

parameter to Custom.

Select this parameter to enable the noise variance input port.

More About

The block supports gray codes in constellation mapping with the following convention. A gray code sequence for k bits is calculated using the following equation:

The bit order of the in-phase and quadrature must follow the sequence given by the preceding equation. k is equal to 2 for 16-QAM, 3 for 64-QAM, and 4 for 256-QAM:

Alternatively, the bit order can be one of the following:

Bit-flipped version of the sequence

Reversed version of the sequence

Reversed version of the bit-flipped sequence

For example, consider 16-QAM modulation and two bits mapped to the in-phase and quadrature phase. The bit order given by the equation is 10 11 01 00. These sequences are also supported:

00 01 11 10 (reversed version of sequence)

01 00 10 11 (bit-flipped version of the sequence

11 10 00 01 (reversed version of the bit-flipped sequence)

Algorithms

The block uses the approximate LLR algorithm to demodulate equalized complex data symbols.

The block computes the approximate LLR by using the nearest constellation point to the received signal with a 0 (or 1) at that bit position. The LLR for a bit b can be defined as

where σ2 is the noise variance, z is the received sequence, s is a symbol from the constellation, and S0, S1 is the set of symbols that corresponds to bits that are 0 and 1, respectively. For more information, see [1].

The latency of the block varies based on the input data type and the selected modulation type and output type.

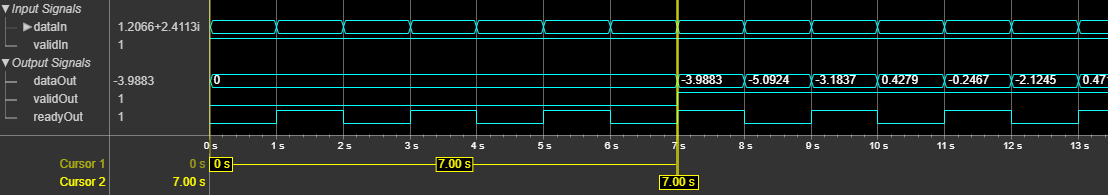

This figure shows a sample output and latency of the block for input data type

fixdt(1,16,14) when you set the Modulation source

parameter to Property, Modulation parameter

to QPSK, Decision type parameter to

Approximate log-likelihood ratio, Phase

offset parameter to pi/2, and Output

type parameter to Scalar. The latency of the block

is 7 clock cycles.

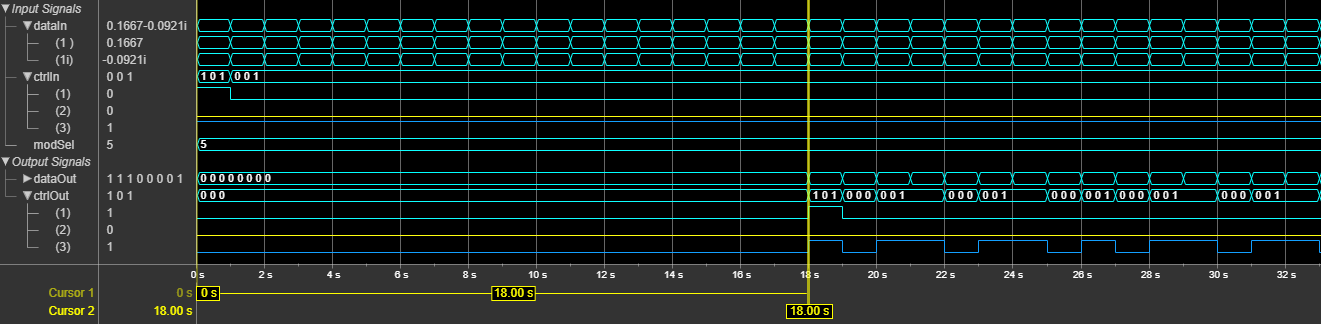

This figure shows a sample output and latency of the block for input data type

fixdt(1,16,14) when you set the Modulation source

parameter to Input port, Maximum modulation

parameter to 256-QAM port, Constellation

ordering parameter to Default port,

Decision type parameter to Hard,

Output type parameter to Vector, and

Normalization method parameter to Unit average

power, and specify the modSel input port value as

5 (32-PSK). The latency of the block is 18 clock cycles.

The performance of the synthesized HDL code varies with the target and synthesis options. It also varies based on the input data type and selected modulation type, decision type, and output type.

This table shows the resource and performance data synthesis results of the block for an

input data of type fixdt(1,16,14) when you set the Modulation

source parameter to BPSK,

Modulation parameter to Property the

Decision type parameter to Approximate log-likelihood

ratio, and the Output type parameter to

Scalar. The generated HDL code is targeted to an AMD®

Zynq®- 7000 ZC706 Evaluation Board. The design achieves a clock frequency of 244.02

MHz.

| Slice LUTs | Slice Registers | DSPs | Block RAM |

|---|---|---|---|

| 332 | 282 | 8 | 0 |

References

[1] Zhang, Meixiang, and Sooyoung Kim. "Universal Soft Demodulation Schemes for M ‐ary Phase Shift Keying and Quadrature Amplitude Modulation." IET Communications 10, no. 3 (February 2016): 316–26. https://doi.org/10.1049/iet-com.2015.0730.

Extended Capabilities

This block supports C/C++ code generation for Simulink® accelerator and rapid accelerator modes and for DPI component generation.

HDL Coder provides additional configuration options that affect HDL implementation and synthesized logic.

This block has one default HDL architecture.

| ConstrainedOutputPipeline | Number of registers to place at

the outputs by moving existing delays within your design. Distributed

pipelining does not redistribute these registers. The default is

|

| InputPipeline | Number of input pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| OutputPipeline | Number of output pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| SynthesisAttributes |

Specifies the synthesis attributes for the blocks and block output signals in the model. The generated HDL code contains these attributes. For more information, see SynthesisAttributes (HDL Coder). |

You cannot generate HDL for this block inside a Resettable Synchronous Subsystem (HDL Coder).

Version History

Introduced in R2022a

See Also

Functions

Blocks

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

选择网站

选择网站以获取翻译的可用内容,以及查看当地活动和优惠。根据您的位置,我们建议您选择:。

您也可以从以下列表中选择网站:

如何获得最佳网站性能

选择中国网站(中文或英文)以获得最佳网站性能。其他 MathWorks 国家/地区网站并未针对您所在位置的访问进行优化。

美洲

- América Latina (Español)

- Canada (English)

- United States (English)

欧洲

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)