NR LDPC Encoder

Perform LDPC encoding according to 5G NR standard

Libraries:

Wireless HDL Toolbox /

Error Detection and Correction

Description

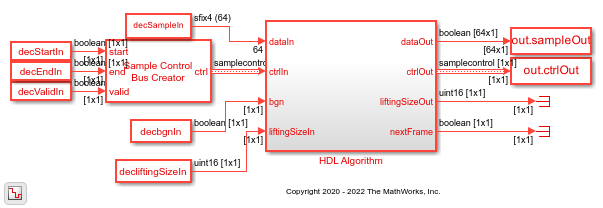

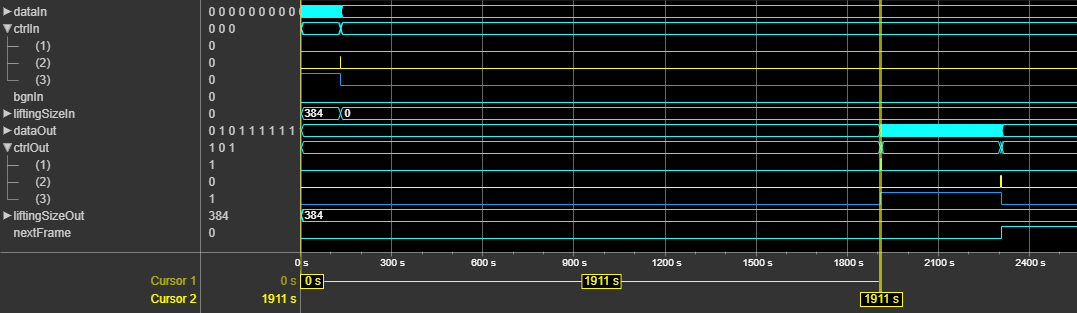

The NR LDPC Encoder block implements a low-density parity-check (LDPC) encoder with hardware-friendly control signals. The block accepts data bits, a stream of control signals, a base graph number, and lifting sizes. The block outputs encoded bits, a stream of control signals, lifting sizes, and a signal that indicates when the block is ready to accept new inputs.

The block functionality matches that of the function nrLDPCEncode (5G Toolbox). You can use this block

for channel coding of downlink and uplink shared channels and paging channel according to 5G

new radio (NR) standard TS 38.212 [1].

The block supports scalar and vector inputs. The block provides an architecture suitable for HDL code generation and hardware deployment. For more information, see Algorithms.

Examples

Ports

Input

Output

More About

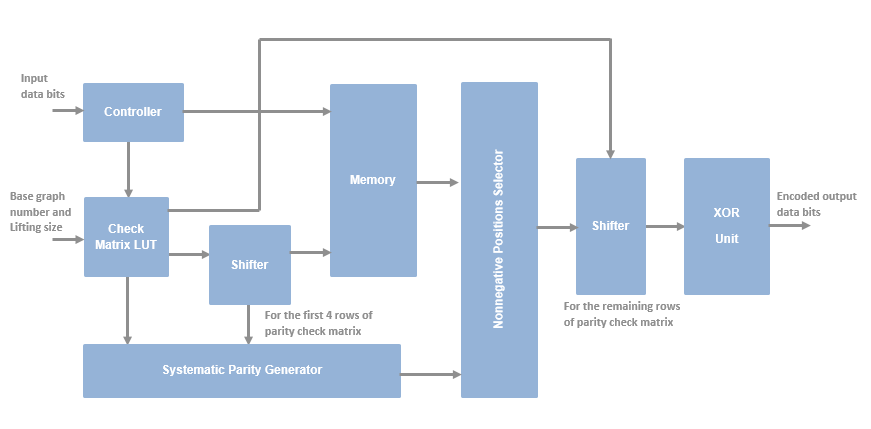

Algorithms

References

[1] 3GPP TS 38.212. “NR; Multiplexing and Channel Coding.” 3rd Generation Partnership Project; Technical Specification Group Radio Access Network.

[2] Gallager, R. “Low-Density Parity-Check Codes.” IEEE Transactions on Information Theory 8, no. 1 (January 1962): 21–28. www.doi.org/10.1109/TIT.1962.1057683.

Extended Capabilities

Version History

Introduced in R2020a