LTE Turbo Encoder

Encode binary samples using turbo algorithm

Libraries:

Wireless HDL Toolbox /

Error Detection and Correction

Description

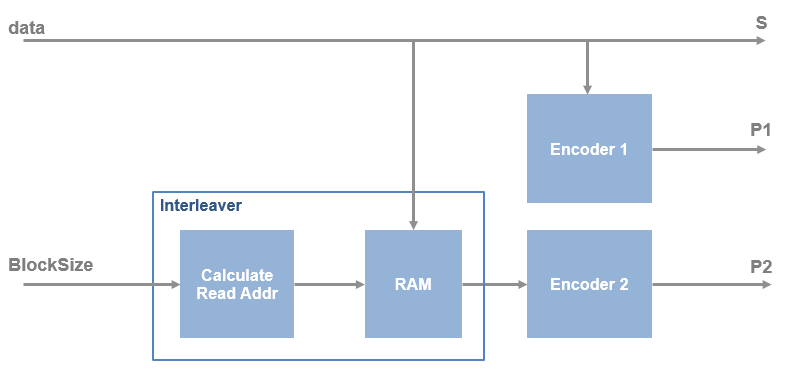

The LTE Turbo Encoder block implements the turbo encoder described by

LTE standard TS 36.212 [1] using an interface

and architecture optimized for HDL code generation and hardware deployment. The encoder

is a parallel concatenated convolutional code (PCCC) with two 8-state constituent

encoders and an internal interleaver. The first encoder operates on the input data

stream, and the second encoder operates on an interleaved version of the input data. The

block terminates each encoder output with independent tail bits. The coding rate is 1/3.

The encoded output bits for each input bit are returned as a 3-by-1 vector, [S

P1 P2]. In this vector, S is the systematic bit, and

P1 and P2 are the parity bits from the two

encoders.

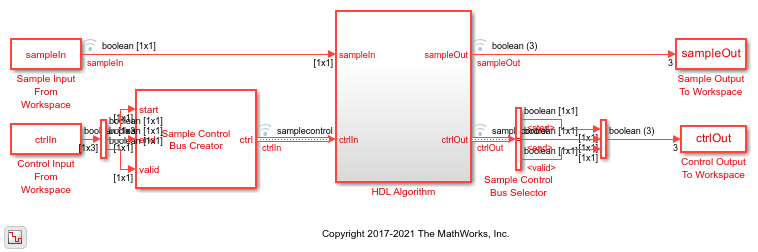

This block uses a

streaming sample interface with a bus for related control signals. This interface enables the

block to operate independently of frame size, and to connect easily with other Wireless HDL Toolbox™ blocks. The block accepts and returns a value representing a single sample, and a

bus containing three control signals. These signals indicate the validity of each sample and the

boundaries of the frame. To convert a matrix into a sample stream and these control signals, use

the Frame To Samples block

or the whdlFramesToSamples

function. For a full description of the interface, see Streaming Sample Interface.

The block can accept new input data after the previous frame is complete. Apply input

frames with at least BlockSize + 16 idle cycles between them. The 16

cycles consists of 12 cycles for pipeline delays in the algorithm, and 4 cycles of tail

bits. This latency does not vary with block size. Or, you can use the output signal

ctrl.end to determine when the block is

ready for new input.

This waveform shows an input frame of 40 samples, with 57 idle cycles between frames.

The input and output ctrl buses are expanded to show the control

signals. start and end show the frame boundaries,

and valid qualifies the data samples. The optional

tail1 and tail2 signals indicate the

cycles when the tail bits from each encoder are valid.

Examples

Ports

Input

Output

Parameters

Tips

You cannot use this block inside an Enabled Subsystem or Resettable Subsystem.

Algorithms

References

[1] 3GPP TS 36.212. "Multiplexing and channel coding." 3rd Generation Partnership Project; Technical Specification Group Radio Access Network; Evolved Universal Terrestrial Radio Access (E-UTRA). URL: https://www.3gpp.org.

Extended Capabilities

Version History

Introduced in R2017b

See Also

Blocks

Functions

lteTurboEncode(LTE Toolbox) |lteTurboDecode(LTE Toolbox) |lteDLSCHInfo(LTE Toolbox)