CCSDS LDPC Decoder

Libraries:

Wireless HDL Toolbox /

Error Detection and Correction

Description

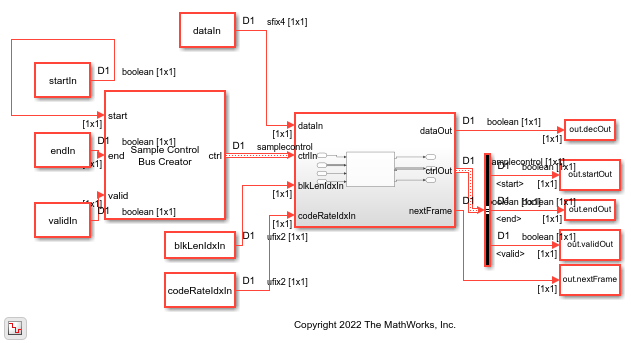

The CCSDS LPDC Decoder block implements a low-density parity-check (LDPC) decoder using a layered belief propagation algorithm with min-sum and normalized min-sum approximation for decoding LDPC codes according to the Consultative Committee for Space Data Systems (CCSDS) standard [1]. The block accepts log-likelihood ratio (LLR) values, a stream of control signals, a block length, and a code rate as inputs. The block outputs decoded bits, a stream of control signals, and a signal that indicates when the block is ready to accept new inputs.

The block supports scalar inputs and vector inputs of size 8. The block supports early termination to improve decoding performance and convergence speeds at high signal-to-noise ratio (SNR) conditions.

The block provides an architecture suitable for HDL code generation and hardware deployment. You can use this block in a CCSDS receiver for satellite communication.

Examples

Decode and Recover Message Using CCSDS LDPC Decoder

Decode and recover message from codeword using CCSDS LDPC Decoder.

Ports

Input

LLR values, specified as a scalar or an eight-element column vector.

For HDL code generation, specify this value in signed fixed-point format. The input word length must be an integer in the range [4, 16] and the fractional length must be in the range [0, 15].

Data Types: int8 | int16 | signed fixed point

Control signals accompanying the sample stream, specified as a

samplecontrol bus. The bus includes the start,

end, and valid control signals, which indicate the

boundaries of the frame and the validity of the samples.

start— Indicates the start of the input frameend— Indicates the end of the input framevalid— Indicates that the data on the input data port is valid

For more details, see Sample Control Bus.

Data Types: bus

Code rate index, specified as 0, 1, or

2. You must specify this value in the

fixdt(0,2,0) format. Each code rate index value represents a

specific code rate, as this table shows.

codeRateIdx Value | Code Rate |

|---|---|

0

| 1/2 |

1 | 2/3 |

2 | 4/5 |

Dependencies

To enable this port, set the Configuration type parameter

to AR4JA LDPC.

Data Types: fixdt(0,2,0)

Block length index, specified as 0, 1, or

2. You must specify this value in the

fixdt(0,2,0) format.

The block length varies with the specified block length index. The input block length must be a multiple of 8. This table shows the block length index values and their corresponding block lengths.

blkLenIdx Value | Block Length |

|---|---|

0

| 1024 |

1 | 4096 |

2 | 16384 |

Dependencies

To enable this port, set the Configuration type parameter

to AR4JA LDPC.

Data Types: fixdt(0,2,0)

Number of iterations, specified as an unsigned integer in the range [1, 63].

If you specify an iter value greater than 63 or less than 1,

the block overrides your specification and sets the iter value to

8 before it performs decoding.

Dependencies

To enable this port, set the Decoding termination criteria

parameter to Max and the Source for number of

iterations parameter to Input port.

Data Types: uint8

Since R2026a

Scaling factor index, specified as a scalar. Each scaling factor index value represents a specific scaling factor, as shown in this table.

scalingFactorIdx Value | Scaling Factor |

|---|---|

0

| 0.5 |

1 | 0.5625 |

2 | 0.6250 |

3 | 0.6875 |

4

| 0.7500 |

5 | 0.8125 |

6 | 0.8750 |

7 | 0.9375 |

8 | 1 |

You must specify this value in the fixdt(0,4,0) format. If you

specify a value other than one listed in this table, the block displays a warning

message and applies the scaling factor index as 4 and continues its

operation.

Dependencies

To enable this port, set the Algorithm parameter to

Normalized min-sum and then set the Source

for scaling factor parameter to Input

port.

Data Types: uint8

Output

Decoded bits, returned as a scalar or an eight-element column vector.

Data Types: Boolean

Control signals accompanying the sample stream, returned as a samplecontrol

bus. The bus includes the start, end, and

valid control signals, which indicate the boundaries of the frame

and the validity of the samples.

start— Indicates the start of the output frameend— Indicates the end of the output framevalid— Indicates that the data on the output data port is valid

For more details, see Sample Control Bus.

Data Types: bus

Block ready indicator, returned as a Boolean scalar.

The block sets this signal to 1 when the block is ready to

accept the start of the next frame. If the block receives an input

ctrl.start signal while nextFrame is

0, the block discards the frame in progress and begins processing

the new data.

Data Types: Boolean

Actual number of iterations the block takes to decode the output, returned as a positive scalar.

Dependencies

To enable this port, set the Decoding termination criteria

parameter to Early.

Data Types: uint8

Parity check status indicator, returned as a Boolean scalar. The port indicates the status of the parity check after the decoding operation.

0— Indicates that the parity check failed1— Indicates that the parity check passed

Dependencies

To enable this port, select the Enable parity check output port parameter.

Data Types: Boolean

Parameters

Select the configuration type. For more information about the supported configurations, see [1].

Since R2026a

Select the type of LDPC decoding algorithm. For more information, see Algorithm.

Min-sum— Use this option to select the layered belief propagation algorithm with a min-sum approximation. For more information, see Min-Sum Approximation.Normalized min-sum— Use this option to select the layered belief propagation algorithm with a normalized min-sum approximation. For more information, see Normalized Min-Sum Approximation.

Since R2026a

Specify the scaling factor as one of these:

Property— Select this option to enable the Scaling factor parameter.Input port— Select this option to enable the scalingFactorIdx port.

Dependencies

To enable this parameter, set the Algorithm parameter to

Normalized min-sum.

Since R2026a

Specify the scaling factor as a scalar in the range 0.5 to 1, incremented by 0.0625.

For better performance, it is recommended to use scaling factors 0.75

and 1.

Dependencies

To enable this parameter, set the Algorithm parameter to

Normalized min-sum and the Source for scaling

factor parameter to Property.

Select the decoding termination criteria.

Max— Terminate decoding when the block reaches the number of iterations specified in the block mask or the iter input port.Early— Terminate decoding when the block completes all of the parity checks or when the block reaches the maximum number of iterations specified in the block mask.

Select the source for specifying the number of iterations.

You can set the number of iterations by using an input port or a parameter.

Property— Select this option to enable the Number of iterations parameter.Input port— Select this option to enable the iter port.

Specify the number of decoding iterations.

Dependencies

To enable this parameter, set the Decoding termination

criteria parameter to Max and the

Source for number of iterations parameter to

Property.

Specify the maximum number of decoding iterations.

Dependencies

To enable this parameter, set the Decoding termination

criteria parameter to Early and set the

Source for number of iterations parameter to

Property.

Select this parameter to enable the parityCheck output port. Use this output port to view the status of the parity check.

Algorithms

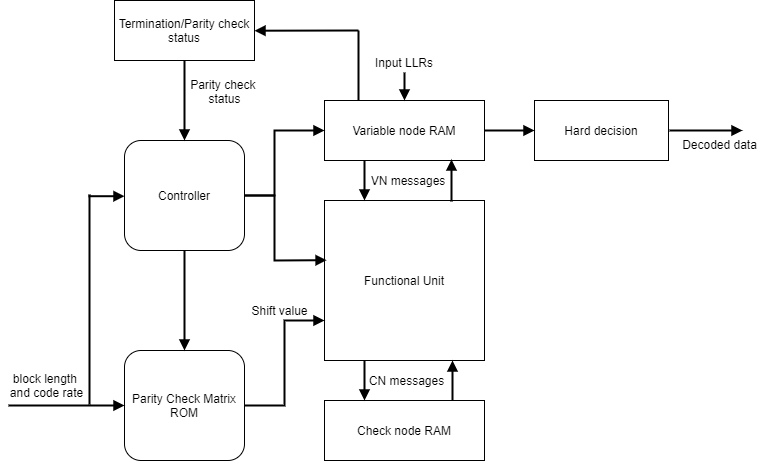

This figure shows the architecture block diagram of the CCSDS LDPC Decoder block. The Controller block controls the layer and iteration count of the decoding process. The Variable node RAM block stores the variable node (VN) messages, and the Check node RAM block stores the check node (CN) messages. The Functional Unit block calculates the VN messages and CN messages based on the layered belief propagation and either the normalized min-sum approximation algorithm or the min-sum approximation algorithm. The Termination/Parity check status block calculates the parity checks and provides the parity check status after each iteration. For more information about the decoding algorithms, see the following sections.

The implementation of the belief propagation algorithm is based on the decoding algorithm presented in [4]. For a transmitted LDPC-encoded codeword c, where , the input to the LDPC decoder is the log-likelihood ratio (LLR) value .

In each iteration, the key components of the algorithm are updated based on these equations:

,

, initialized as before the first iteration, and

.

At the end of each iteration, is an updated estimate of the LLR value for the transmitted bit . The value is the soft-decision output for . If , the hard-decision output for is 1. Otherwise, the output is 0.

The implementation of the layered belief propagation algorithm is based on the decoding algorithm presented in [5], section II.A. The decoding loop iterates over subsets of rows (layers) of the parity-check matrix (PCM). For each row m, in a layer and each bit index j, the implementation updates the key components of the algorithm based on these equations:

(1) ,

(2) ,

(3) ,

(4) , and

(5) .

For each layer, the decoding equation (5) works on the combined input obtained from the current LLR inputs and the previous layer updates .

Because only a subset of the nodes is updated in a layer, the layered belief propagation algorithm is faster than the belief propagation algorithm. To achieve the same error rate as attained with belief propagation decoding, use half the number of decoding iterations when using the layered belief propagation algorithm.

The implementation of the min-sum approximation algorithm follows the layered belief propagation algorithm with equation (2) replaced by

,

where α is 1.

The implementation of the normalized min-sum approximation algorithm follows the layered belief propagation algorithm with equation (2) replaced by

,

where α is in the range [0, 1] and is the scaling factor specified by the Scaling factor parameter. This equation is an adaptation of equation (4) presented in [4].

The latency of the block varies based on the selected Configuration type parameter value, the values of the blkLenIdx and codeRateIdx input ports, and the number of iterations. Because the latency varies, use the nextFrame control signal output port to determine when the block is ready for a new input frame.

The latency of the block is equal to rt + d + L. In this calculation, r is the number of iterations, t is the number of clocks required to decode one iteration, d is the pipeline delay, and L is the length of the input data.

| Configuration Type | Code Rate | Block Length | Number Of Clocks Per Iteration | Pipleline Delay (d) |

|---|---|---|---|---|

| (8160,7136) LDPC | 7/8 | 8160 | 2080 | 27 for scalar and 26 for vector |

| AR4JA LDPC | 1/2 | 2048 | 252 | 10 |

| 8192 | 1240 | |||

| 32768 | 4960 | |||

| 2/3 | 1536 | 316 | ||

| 6144 | 844 | |||

| 24576 | 3376 | |||

| 4/5 | 1280 | 444 | ||

| 5120 | 482 | |||

| 20480 | 2584 |

This figure shows a sample output and latency of the CCSDS LDPC Decoder

block for a vector input when you set the Configuration type parameter

to AR4JA LDPC, the Algorithm parameter to

Min-sum, the Decoding termination criteria

parameter to Max, the Number of iterations parameter

to 8, and the codeRateIdx input port value to

0. The latency of the block is 2281 clock cycles.

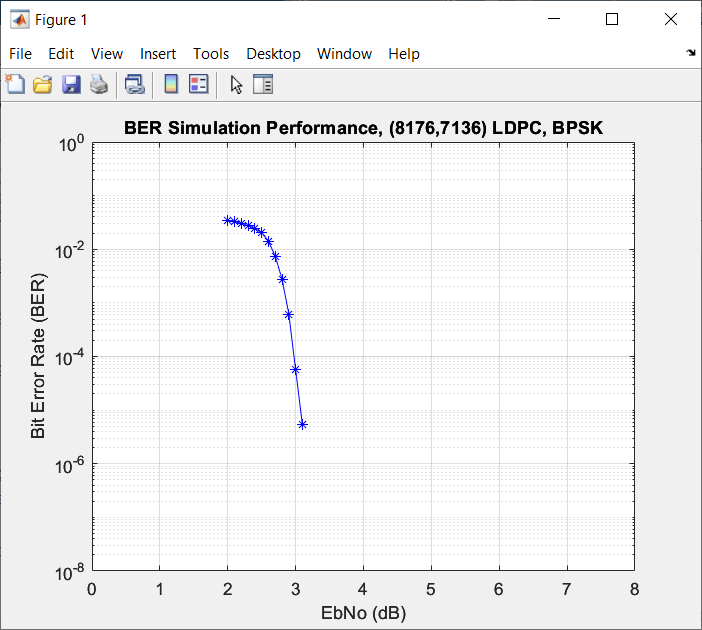

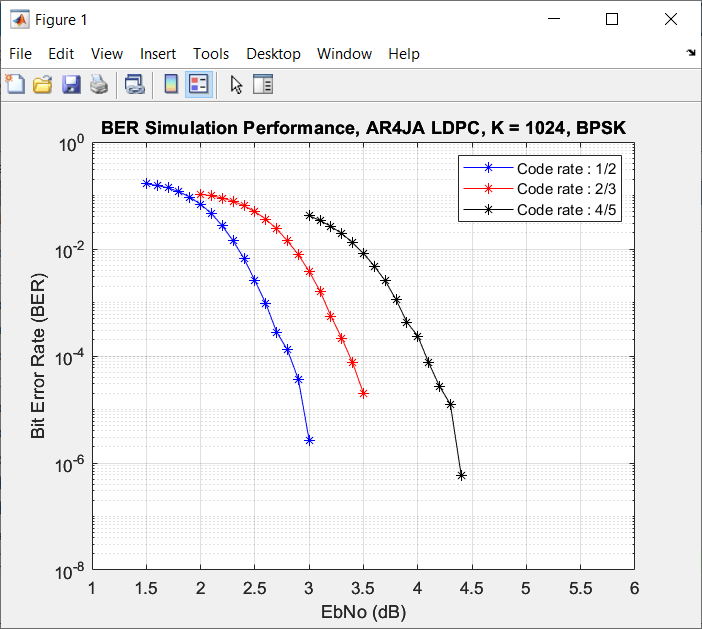

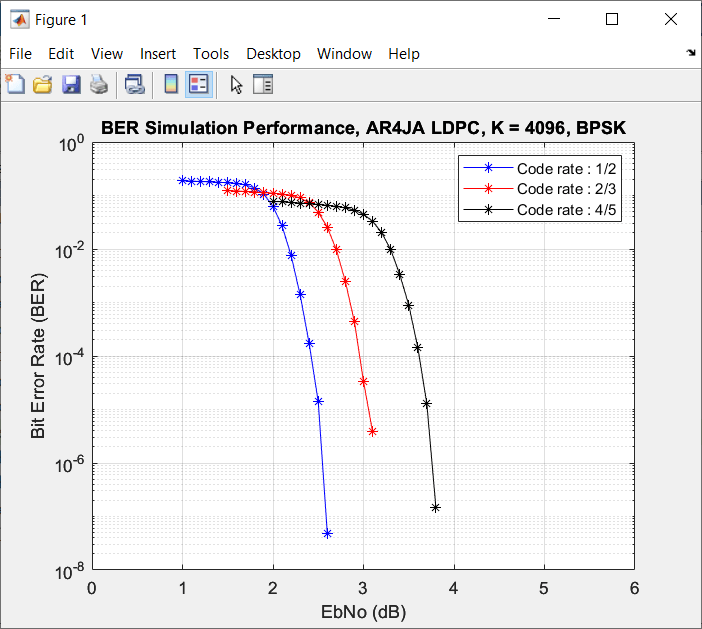

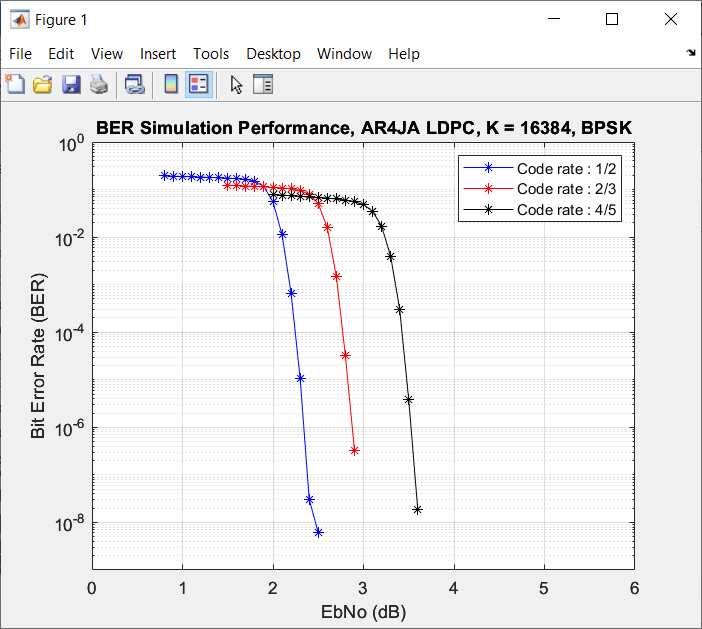

This section shows the EbNo and BER plots of the block for specified inputs and parameter settings.

This plot shows the performance of the block for a 4 bit QPSK modulated LLR input when

you set the Configuration type parameter to (8160,7136)

LDPC.

This plot shows the performance of the block for a 4 bit QPSK modulated LLR input for a

block length of 1024 with code rates of 1/2, 2/3, and 4/5, respectively, when you set the

Configuration type parameter to AR4JA

LDPC.

This plot shows the performance of the block for a 4 bit QPSK modulated LLR input for a

block length of 4096 with code rates of 1/2, 2/3, and 4/5, respectively, when you set the

Configuration type parameter to AR4JA

LDPC.

This plot shows the performance of the block for a 4 bit QPSK modulated LLR input for a

block length of 16384 with code rates of 1/2, 2/3, and 4/5, respectively, when you set the

Configuration type parameter to AR4JA

LDPC.

The performance of the synthesized HDL code varies with the target and synthesis options. The performance also varies based on the type of algorithm, decoding termination criteria, and the word length of the input LLR values.

This table shows the resource and performance data synthesis results of the block for

the supported CCSDS standards when you set the Configuration type

parameter to (8160,7136) LDPC or AR4JA

LDPC, the Number of iterations parameter to

8, and the input LLR values as a value with the

fixdt(1,4,0). The generated HDL targets to the AMD®

Zynq®

UltraScale+™ MPSoC - ZCU102 Evaluation Board.

| Configuration Type | Input Type | Slice LUTs | Slice Registers | Block RAMs | Maximum Frequency in MHz |

|---|---|---|---|---|---|

| (8160,7136) LDPC | Scalar | 20201 | 14749 | 96 | 377.1 |

| Vector | 20580 | 15146 | 96 | 372.4 | |

| AR4JA LDPC | Scalar | 29753 | 19786 | 192 | 291.9 |

| Vector | 28812 | 19854 | 192 | 287.9 |

This block has similar implementation for scalar and vector inputs. So, you do not find substantial difference in the resource utilization and latency.

References

[1] TM Synchronization and Channel Coding. Recommendation for Space Data System Standards. CCSDS 131.0-B-3. Blue Book. Issue 3. Washington, D.C.: CCSDS, September 2017.

[2] TM Synchronization and Channel Coding. Summary of Concept and Rationale CCSDS 130.1-G-3. Green Book. Issue 3, June 2020.

[3] Stephen B. Wicker. Error Control Systems for Digital Communication and Storage. Prentice Hall, 1995.

[4] Gallager, R. “Low-Density Parity-Check Codes.” IEEE Transactions on Information Theory 8, no. 1 (January 1962): 21–28. https://doi.org/10.1109/TIT.1962.1057683.

[5] Hocevar, D.E. “A Reduced Complexity Decoder Architecture via Layered Decoding of LDPC Codes.” In IEEE Workshop OnSignal Processing Systems, 2004. SIPS 2004., 107–12. Austin, Texas, USA: IEEE, 2004. https://doi.org/10.1109/SIPS.2004.1363033.

Extended Capabilities

This block supports C/C++ code generation for Simulink® accelerator and rapid accelerator modes and for DPI component generation.

HDL Coder™ provides additional configuration options that affect HDL implementation and synthesized logic.

This block has one default HDL architecture.

| ConstrainedOutputPipeline | Number of registers to place at

the outputs by moving existing delays within your design. Distributed

pipelining does not redistribute these registers. The default is

|

| InputPipeline | Number of input pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| OutputPipeline | Number of output pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| SynthesisAttributes |

Specifies the synthesis attributes for the blocks and block output signals in the model. The generated HDL code contains these attributes. For more information, see SynthesisAttributes (HDL Coder). |

You cannot generate HDL for this block inside a Resettable Synchronous Subsystem (HDL Coder).

Version History

Introduced in R2022bThe CCSDS LDPC Decoder block now supports the normalized min-sum option.

To enable the scalingFactorIdx input port, set the

Algorithm parameter to Normalized min-sum,

and then set the Source for scaling factor parameter to

Input port.

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

选择网站

选择网站以获取翻译的可用内容,以及查看当地活动和优惠。根据您的位置,我们建议您选择:。

您也可以从以下列表中选择网站:

如何获得最佳网站性能

选择中国网站(中文或英文)以获得最佳网站性能。其他 MathWorks 国家/地区网站并未针对您所在位置的访问进行优化。

美洲

- América Latina (Español)

- Canada (English)

- United States (English)

欧洲

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)