LTE CRC Decoder

Detect errors in input samples using checksum

Libraries:

Wireless HDL Toolbox /

Error Detection and Correction

Description

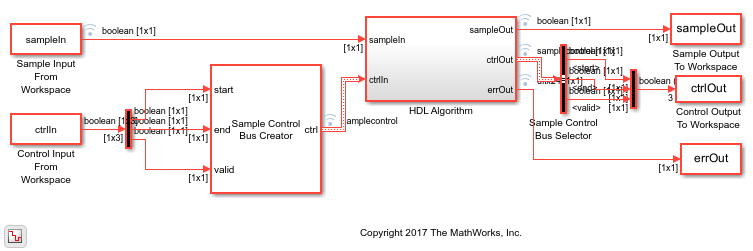

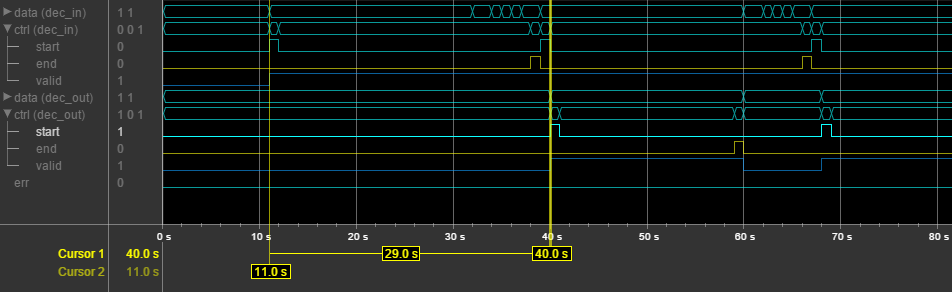

The LTE CRC Decoder block calculates a cyclic redundancy check (CRC) and compares it with the appended checksum, for each frame of streaming data samples. You can select from the polynomials specified by LTE standard TS 36.212 [1]. The block provides a hardware-optimized architecture and interface.

This block uses a

streaming sample interface with a bus for related control signals. This interface enables the

block to operate independently of frame size, and to connect easily with other Wireless HDL Toolbox™ blocks. The block accepts and returns a value representing a single sample, and a

bus containing three control signals. These signals indicate the validity of each sample and the

boundaries of the frame. To convert a matrix into a sample stream and these control signals, use

the Frame To Samples block

or the whdlFramesToSamples

function. For a full description of the interface, see Streaming Sample Interface.

Examples

Ports

Input

Output

Parameters

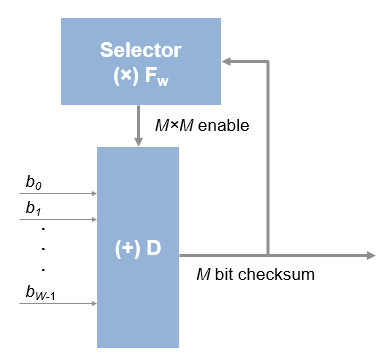

Algorithms

References

[1] 3GPP TS 36.212. "Multiplexing and channel coding." 3rd Generation Partnership Project; Technical Specification Group Radio Access Network; Evolved Universal Terrestrial Radio Access (E-UTRA). URL: https://www.3gpp.org.

[2] Campobello, Giuseppe, Giuseppe Patane, and Marco Russo. "Parallel CRC Realization." IEEE Transactions on Computers. Vol. 52, No. 10, October 2003, pp. 1312–1319.

Extended Capabilities

Version History

Introduced in R2017b