General CRC Syndrome Detector HDL Optimized

Detect errors in input data using CRC

Libraries:

Communications Toolbox HDL Support /

Error Detection and Correction /

CRC

Description

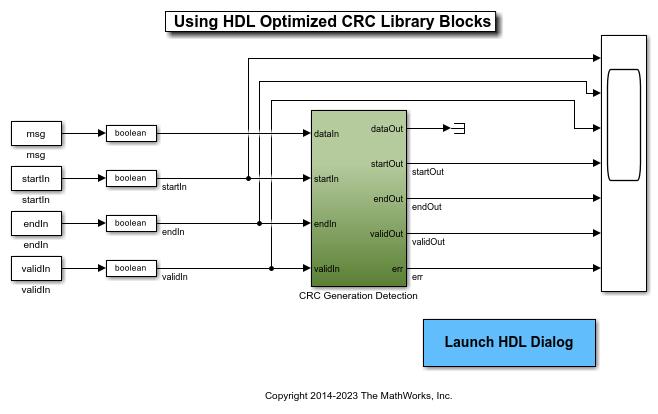

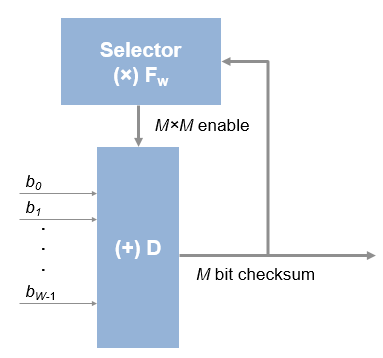

The General CRC Syndrome Detector HDL Optimized block performs a cyclic redundancy check (CRC) on data and compares the resulting checksum with the appended checksum. The General CRC Syndrome Detector HDL Optimized block processing is optimized for HDL code generation. If the two checksums do not match, the block reports an error. Instead of processing an entire frame at once, the block accepts and returns a data sample stream with accompanying control signals. The control signals indicate the validity of the samples and the boundaries of the frame. To achieve higher throughput, the block accepts vector data up to the CRC length and implements a parallel architecture.

Examples

Ports

Input

Output

Parameters

Algorithms

References

[1] Campobello, G., G. Patane, and M. Russo. “Parallel Crc Realization.” IEEE Transactions on Computers 52, no. 10 (October 2003): 1312–19. https://doi.org/10.1109/TC.2003.1234528.

Extended Capabilities

Version History

Introduced in R2012b