NR Polar Encoder

Perform polar encoding according to 5G NR standard

Libraries:

Wireless HDL Toolbox /

Error Detection and Correction

Description

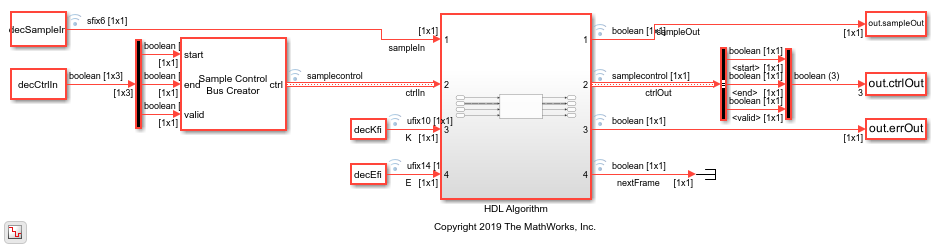

The NR Polar Encoder block implements a streaming polar encoder with hardware-friendly control signals. The 5G NR standard requires polar encoding for channel coding of the DCI, UCI, and BCH transmit channels.

The encoder implementation matches the nrPolarEncode (5G Toolbox) function.

You must specify the link direction because the coding scheme defined by the 5G NR standard is different for downlink and uplink messages. Downlink messages are encoded with interleaving and uplink messages do not use interleaving.

Because the latency of this operation can vary, the block provides an output signal, nextFrame, that indicates when the block is ready to accept new inputs. For more details, see the Latency section on this page.

Examples

Ports

Input

Output

Parameters

Tips

You cannot use this block inside an Enabled Subsystem or Resettable Subsystem.

Algorithms

References

[1] 3GPP TS 38.212. "NR; Physical channels and modulation." 3rd Generation Partnership Project; Technical Specification Group Radio Access Network. URL: https://www.3gpp.org.

[2] Arikan, Erdal. "Channel Polarization: A Method for Constructing Capacity-Achieving Codes for Symmetric Binary-Input Memoryless Channels." IEEE Transactions on Information Theory 55, no. 7 (July 2009): 3051–73. https://doi.org/10.1109/TIT.2009.2021379.

Extended Capabilities

Version History

Introduced in R2020a

See Also

nrPolarEncode (5G Toolbox) | NR Polar Decoder