NR HDL Receiver Performance

Wireless HDL Toolbox™ 5G NR reference applications implement and verify parts of a 5G NR downlink receiver. For information about the reference applications, see NR HDL Reference Applications Overview. This page shows the performance of the stages of the receiver over a range of signal conditions for both the MATLAB® reference design and the hardware implementation running on a board. For both MATLAB and hardware performance characterization, the design runs 1000 times at each SNR level, in 0.5 dB increments from –8 dB to 1 dB. The table shows the waveform and receiver configuration parameters.

| Parameter | Setting |

|---|---|

| SSB Pattern | Case C |

| SCS SSB | 30 |

| SCS Common | 30 |

| PDCCH Config SIB1 | 164 |

| Lmax | 8 |

| kSSB | 0 |

| Minimum channel bandwidth | 5 |

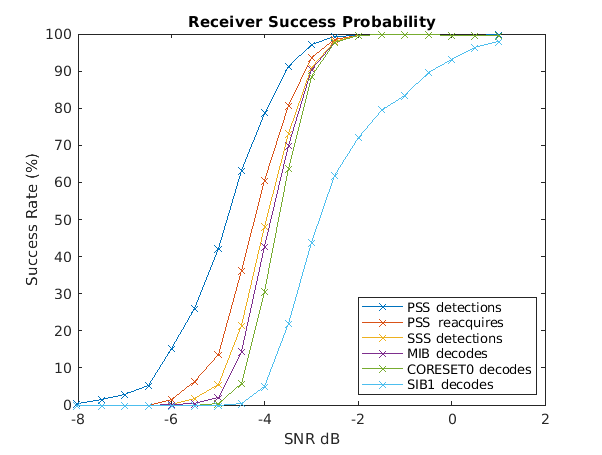

The first graph shows the success probability of the MATLAB reference design for the receiver. This reference design models the data flow and sample rate used in the hardware implementation and operates on vectors and matrices of floating-point data samples. For more information, see NR HDL Downlink Receiver MATLAB Reference. The plot shows the success rate at each receiver stage for a range of signal-to-noise ratios. The input waveforms are created by using 5G Toolbox™ functions to generate a 5G FR1 waveform that contains one SSB burst and the corresponding SIB1 transmission.

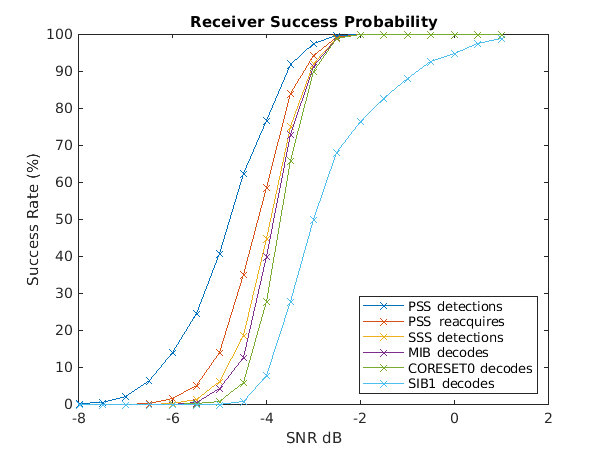

The second graph shows the success probability of the receiver when deployed on hardware, for the same range of signal-to-noise ratios. The receiver described in the 5G NR SIB1 Recovery for FR1 and FR2 Using AMD RFSoC Device (SoC Blockset) example is deployed to a Xilinx® Zynq® UltraScale+™ RFSoC ZCU111 board. The characterization script writes the generated input waveforms to DDR memory on the board, and the deployed receiver reads the input signals from the memory.