NR CRC Encode and Decode Streaming Data

This example shows how to use the NR CRC Encoder and NR CRC Decoder Simulink® blocks and compare the hardware-optimized results with the results from the 5G Toolbox™ functions nrCRCEncode (5G Toolbox) and nrCRCDecode (5G Toolbox), respectively. These blocks support scalar and vector inputs. The NR CRC Encoder and NR CRC Decoder blocks support hardware code generation.

Generate Input Data

Generate random frames of input data and a control signal that indicates the frame boundaries. The frame gap accommodates the latency of the NR CRC Encoder block.

CRCType = 'CRC24A'; numFrames = 4; scalar = true; % true for scalar inputs and false vector inputs parallel = false; % true for parallel architecture and false for % serial architecture msg = {numFrames}; dataIn = []; encStartIn = []; encEndIn = []; encValidIn = []; [poly,crcLen] = NRCRCEncodeAndDecoderHDLInitScript(CRCType); if parallel listN = divisors(crcLen); % Factors of length of CRC polynomial dataWidth = randsrc(1,1,listN(2:end)); else dataWidth = 1; end frameGap = 120; % Frame gap selected based on CRCType and dataWidth for ii = 1:numFrames len = randsrc(1,1,1:1000); frameLen = len*dataWidth; msg{ii} = randi([0 1],1,frameLen); % Generate data based on the selected dataWidth if scalar data = reshape(msg{ii},dataWidth,len); encIn = zeros(1,size(data,2)); for i = 1:size(data,2) encIn(i) = bit2int(data(:,i).',length(data(:,i))).'; %#ok<*SAGROW> end dataIn = fi([dataIn encIn zeros(size(encIn,1),frameGap)],0,dataWidth,0); else encIn = reshape(msg{ii},dataWidth,len); %#ok<*UNRCH> dataIn = logical([dataIn encIn zeros(size(encIn,1),frameGap)]); end encStartIn = logical([encStartIn 1 zeros(1,len-1) zeros(1,frameGap)]); encEndIn = logical([encEndIn zeros(1,len-1) 1 zeros(1,frameGap)]); encValidIn = logical([encValidIn ones(1,len) zeros(1,frameGap)]); end encSampleIn = timeseries(dataIn'); sampleTime = 1; simTime = length(encValidIn);

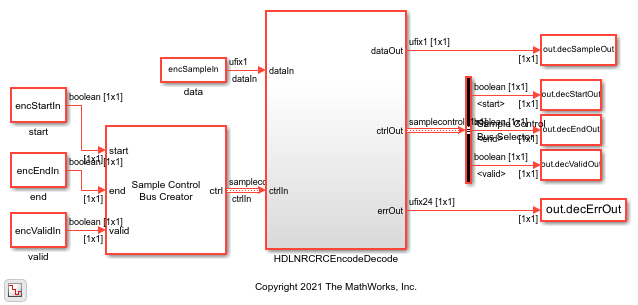

Run the Model

The HDLNRCRCEncodeDecode subsystem contains HDL NR CRC Encoder and HDL NR CRC Decoder subsystems that contain NR CRC Encoder and NR CRC Decoder blocks, respectively. Running the model imports the input signal variables encSampleIn, encStartIn, encEndIn, and encValidIn and exports variables encSampleOut and encCtrlOut to the MATLAB® workspace.

open_system('NRCRCEncodeAndDecodeHDLModel'); set_param('NRCRCEncodeAndDecodeHDLModel/HDLNRCRCEncodeDecode/HDL NR CRC Encoder/NR CRC Encoder','CRCType',CRCType); set_param('NRCRCEncodeAndDecodeHDLModel/HDLNRCRCEncodeDecode/HDL NR CRC Decoder/NR CRC Decoder','CRCType',CRCType); modelOut = sim('NRCRCEncodeAndDecodeHDLModel');

Verify Encoder Results

The HDL NR CRC Encoder subsystem contains the NR CRC Encoder block. Convert the streaming data output of the NR CRC Encoder block to frames, and then compare the output frames with the output of the nrCRCEncode 5G Toolbox function.

encOut = squeeze(modelOut.encSampleOut.Data); startIdx = find(modelOut.encCtrlOut.start.Data); endIdx = find(modelOut.encCtrlOut.end.Data); encValidOut = squeeze(modelOut.encCtrlOut.valid.Data); vector = ~scalar && parallel; for ii = 1:numFrames refEncBits{ii} = nrCRCEncode(msg{ii}',poly); % Extract actual encoded bits from output idx = startIdx(ii):endIdx(ii); if (vector) % For vector inputs encBits = encOut(:,idx); encBits = encBits(:,encValidOut(idx)); actEncBits{ii} = encBits(:); else encBits = encOut(idx); encBits = encBits(encValidOut(idx)); encBits = dec2bin(encBits,dataWidth)-'0'; actEncBits{ii} = reshape(encBits',length(refEncBits{ii}),1); end error = sum(abs(refEncBits{ii}-double(actEncBits{ii}))); fprintf(['CRC-encoded frame %d: Behavioral and ' ... 'HDL simulation differ by %d bits\n'],ii,error); end

CRC-encoded frame 1: Behavioral and HDL simulation differ by 0 bits CRC-encoded frame 2: Behavioral and HDL simulation differ by 0 bits CRC-encoded frame 3: Behavioral and HDL simulation differ by 0 bits CRC-encoded frame 4: Behavioral and HDL simulation differ by 0 bits

Verify Decoder Results

The HDL NR CRC Decoder subsystem contains the NR CRC Decoder block. The HDL NR CRC Encoder subsystem outputs are provided as an input to the HDL NR CRC Decoder subsystem. The HDL NR CRC Decoder subsystem exports a stream of decoded output samples decSampleOut and decErrOut along with a control signal decCtrlOut to the MATLAB workspace. Compare them with the output of the nrCRCDecode function.

dataOut = squeeze(modelOut.decSampleOut.Data); errOut = squeeze(modelOut.decErrOut.Data); startIdx = find(modelOut.decStartOut.Data); endIdx = find(modelOut.decEndOut.Data); validOut = squeeze(modelOut.decValidOut.Data); for ii = 1:numFrames [refDecBits{ii},refErr{ii}] = nrCRCDecode(double(actEncBits{ii}),poly); % Extract actual decoded bits from output idx = startIdx(ii):endIdx(ii); if (vector) % For vector inputs dataOutTmp = dataOut(:,idx); validOutTmp = validOut(:,idx); decBits = dataOutTmp(:,validOutTmp); actDecBits{ii} = decBits(:); else dataOutTmp = dataOut(idx); validOutTmp = validOut(idx); decBits = dataOutTmp(validOutTmp); decBits = dec2bin(decBits,dataWidth) - '0'; actDecBits{ii} = reshape(decBits',length(refDecBits{ii}),1); end actErr{ii} = errOut(endIdx(ii)); error_data = sum(abs(refDecBits{ii} - double(actDecBits{ii}))); error_err = double(refErr{ii}) - double(actErr{ii}); fprintf(['CRC-decoded frame %d: Behavioral and ' ... 'HDL simulation differ by %d bits and %d errors\n'],ii,error_data,error_err); end

CRC-decoded frame 1: Behavioral and HDL simulation differ by 0 bits and 0 errors CRC-decoded frame 2: Behavioral and HDL simulation differ by 0 bits and 0 errors CRC-decoded frame 3: Behavioral and HDL simulation differ by 0 bits and 0 errors CRC-decoded frame 4: Behavioral and HDL simulation differ by 0 bits and 0 errors

See Also

Blocks

Functions

nrCRCEncode(5G Toolbox) |nrCRCDecode(5G Toolbox)