Altera FPGA Board Support from HDL Verifier

Debug and test HDL code on Altera® FPGAs

Capabilities and Features

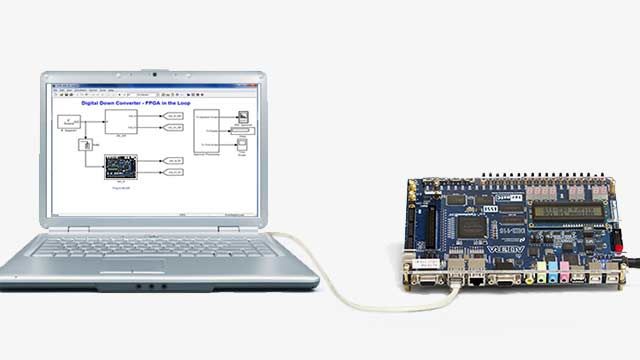

HDL Verifier automates the verification of HDL code on Altera® FPGA boards by enabling three capabilities: FPGA-in-the-loop (FIL) testing, FPGA data capture, and AXI Manager.FIL testing helps ensure that the MATLAB algorithm or Simulink model behaves as expected in the real world, increasing confidence in your silicon implementation. The MATLAB algorithm or Simulink model is used to drive FPGA input stimuli and to analyze the output of the FPGA. With FIL testing, you can verify your design at FPGA speeds, enabling you to run more extensive sets of test cases and perform regression tests on your design.

HDL Verifier supports FIL simulation for select Altera® FPGA boards. The board definition files for these boards are included in the Support Package. You can add other FPGA boards for use with FIL with FPGA board customization.

FPGA Data Capture lets you observe signals from your design in MATLAB or Simulink while the design is running on the Altera FPGA or SoC FPGA. Using AXI Manager, you can read from or write to on-board memory locations from MATLAB or Simulink.

The following device families are supported:

- Arria® 10 SoC, Cyclone® 10 GX, Cyclone 10 LP, and MAX® 10

- Stratix® V, Arria V, Arria V SoC, Cyclone® V, and Cyclone V SoC

- Stratix IV and Cyclone IV

- Cyclone III

- Arria II

Platform and Release Support

See the hardware support package system requirements table for current and prior version, release, and platform availability.

View enhancements and bug fixes in release notes.