IP Core Generation Workflow with Ethernet-Based AXI Manager

This example uses the HDL Verifier™ Ethernet AXI manager IP to access the HDL Coder™ product generated registers. AXI manager provides access to FPGA registers from MATLAB® directly.

Requirements

Intel® Quartus® Prime, with a supported version listed in FPGA Verification Requirements

Arrow® DECA MAX® 10 FPGA evaluation kit

HDL Coder Support Package for Intel FPGA and SoC Devices

HDL Verifier Support Package for Intel FPGA Boards

USB-JTAG cable

Cross-over Ethernet cable

Arrow DECA MAX 10 FPGA Evaluation Kit

This figure shows the Arrow DECA MAX 10 FPGA evaluation kit.

Example Reference Design

The reference design, AXI Manager - Ethernet, uses MathWorks® IP and a MATLAB command line interface for issuing read and write operations. To use this design, you must have the HDL Verifier product. The plugin_rd.m for this reference design is shown below.

function hRD = plugin_rd() % Reference design definition

% Construct reference design object hRD = hdlcoder.ReferenceDesign('SynthesisTool', 'Altera QUARTUS II');

hRD.ReferenceDesignName = 'AXI Manager - Ethernet (requires HDL Verifier)'; hRD.BoardName = 'Arrow DECA MAX 10 FPGA evaluation kit';

% Tool information hRD.SupportedToolVersion = {'17.1','18.1','19.1','20.1'};

%% Add custom design files % add custom Qsys design hRD.addCustomQsysDesign('CustomQsysPrjFile', 'system_soc.qsys'); hRD.CustomConstraints = {'system_soc.sdc','create_project_eth_deca.tcl'}; hRD.CustomFiles = {'phy_to_gmii'}; % Adding other files for custom IP core

% Add ip from support package msg = message('hdlcommon:plugin:IPRepositoryHDLVerifierAlteraNotFound',... '<a href="matlab:matlab.addons.supportpackage.internal.explorer.showSupportPackages({''HDLVALTERA''}, {''tripwire''});">download</a>').getString; hRD.addIPRepository('IPListFunction','hdlverifier.fpga.quartus.iplist','NotExistMessage', msg);

%% Add interfaces % add clock interface hRD.addClockInterface( ... 'ClockConnection', 'altpll_0.c0', ... 'ResetConnection', 'clk_0.clk_reset', ... 'DefaultFrequencyMHz', 50);

% add Register interfaces hRD.addRegisterInterface( ... 'InterfaceConnection', 'udp_axi_manager_0.axi4_udp', ... 'BaseAddress', '0x0000_0000', ... 'InterfaceType', 'AXI4'); % [ 'AXI4-Lite'| 'AXI4' ]

% Specify Embedded Coder(R) Support Package to use for Software Interface hRD.EmbeddedCoderSupportPackage = hdlcoder.EmbeddedCoderSupportPackage.None; % [ None | Zynq | AlteraSoC ]

The corresponding plugin_rd.m file for the AXI manager reference design is located at plugin_rd.m.

Execute IP Core Workflow

The reference design generates an HDL IP core that blinks LEDs on the DECA board. Locate the files that are used in the following demonstration at this path.

matlab/toolbox/hdlcoder/supportpackages/altera/+hdlipcore/+board/ArrowDECA

Follow these steps to execute the IP core workflow for AXI Manager - Ethernet reference design, which uses Ethernet AXI manager IP. Using this reference design, you can generate an HDL IP core that blinks LEDs on the DECA board. To generate an HDL IP core, follow these steps.

1. Set up the Intel Quartus tool path. Use your own Intel Quartus installation path when executing the command.

hdlsetuptoolpath('ToolName','Altera QUARTUS II','ToolPath', ... 'C:\intelFPGA\20.1\quartus\bin64\quartus.exe');

2. Open the Simulink model that implements LED blinking by executing this command in MATLAB.

open_system('hdlcoder_led_blinking')

3. Launch HDL Workflow Advisor from the hdlcoder_led_blinking/led_counter subsystem. To do this, right-click the led_counter subsystem, point to Select Apps, and click the HDL Coder button. Then, in the HDL Coder app section, select HDL Workflow Advisor.

4. In step 1.1, select Target workflow as IP Core Generation and Target platform as Arrow DECA MAX 10 FPGA evaluation kit. Click Run This Task.

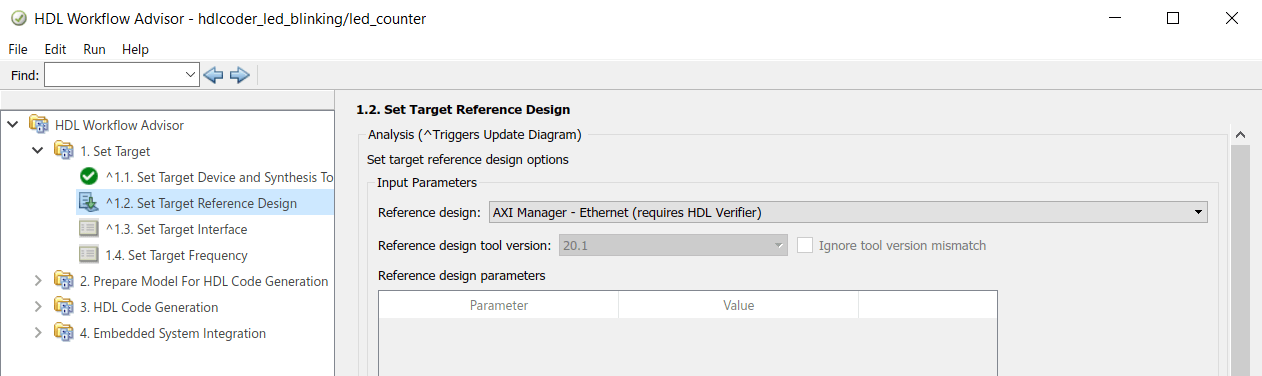

5. In step 1.2, select Reference design as AXI Manager - Ethernet (requires HDL Verifier).

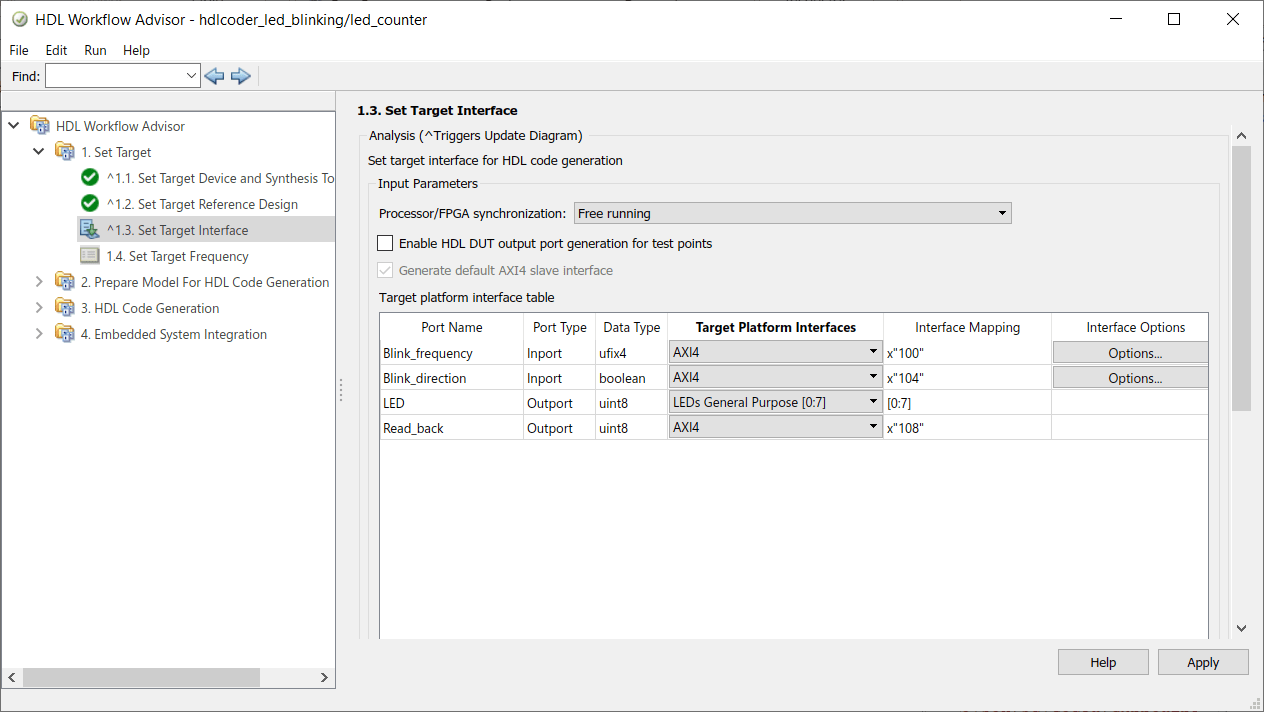

6. In step 1.3, assign Blink_frequency, Blink_direction, and Read_back ports to the AXI4 interface. Assign the LED port to LEDs General Purpose [0:7].

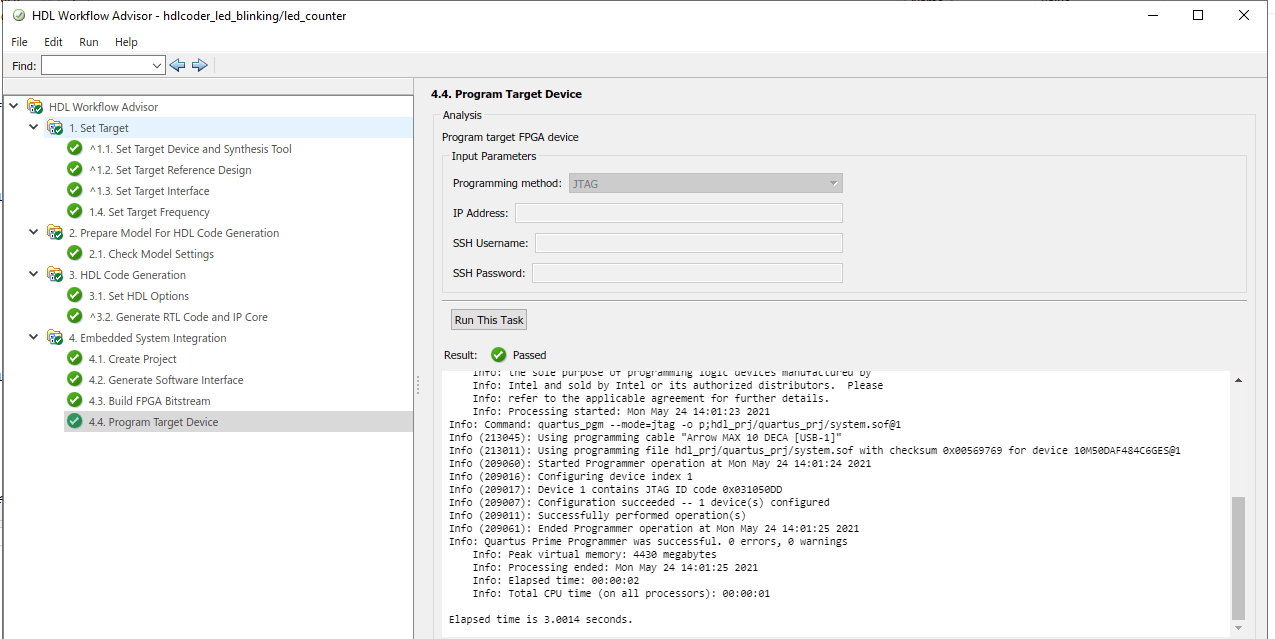

7. Run the remaining steps in the workflow to generate a bitstream and program the target device.

The Ethernet AXI manager IP in this design has a default target IP address of 192.168.1.2 and default UDP port value of 50101. Configure the network interface card (NIC) of the host machine accordingly.

Determine Addresses from IP Core Report

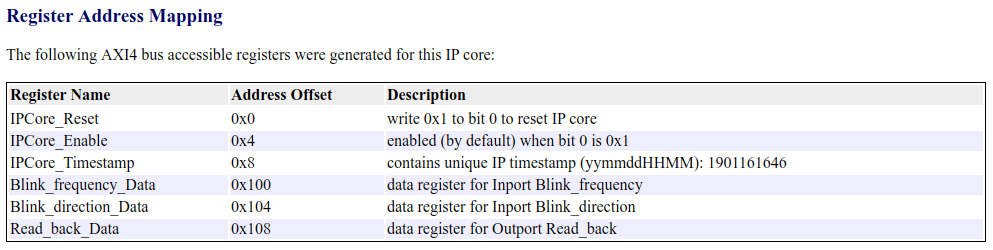

The base address for an HDL Coder IP core is defined in the reference design plugin_rd.m. For this design, the base address is 0x0000_0000. The IP core report register address mapping table shows the offsets.

HDL Verifier AXI Manager - Ethernet Command Line Interface

If you have the HDL Verifier Support Package for Intel FPGA Boards and select the AXI Manager - Ethernet reference design, then you can use the MATLAB command line interface to access the IP core that is generated by the HDL Coder product.

To write and read from the DDR memory, follow these steps.

1. Create an AXI manager object.

h = aximanager('Intel','interface','PLEthernet','DeviceAddress','192.168.1.2')

2. Issue a write command. For example, disable the DUT.

h.writememory('4',0)

3. Re-enable the DUT.

h.writememory('4',1)

4. Read the current counter value.

h.readmemory('108',1)

See Also

aximanager | writememory | readmemory