Supported EDA Tools and Hardware

Cosimulation Requirements

Cosimulation is supported for the 64-bit version of the following simulators.

To get started, see Connect MATLAB and HDL Simulator or Start HDL Simulator for Cosimulation in Simulink.

Cadence Xcelium Requirements

MATLAB® and Simulink® support Cadence® verification tools on Linux® using HDL Verifier™. Use this recommended version, which has been fully tested against the current release:

Xcelium™ 2024.09

The HDL Verifier shared libraries (liblfihdls*.so,

liblfihdlc*.so) are built using the

gcc included in the Cadence

Xcelium simulator platform distribution. If you are building your own

application, choose the version of the library that matches the version of

gcc that you are using. See the HDL simulator

documentation for more details about how to build and link your own

applications.

Siemens Questa and ModelSim Requirements

HDL Verifier has been tested against the following stand-alone version of Questa™:

Questa Base/Core/Prime 2024.3_1

HDL Verifier should work with the same FPGA vendor-bundled versions of Questa.

Vivado Simulator Requirements

MATLAB and Simulink support AMD® Vivado® verification tool using HDL Verifier. Use this recommended version, which has been fully tested against the current release:

AMD Vivado 2024.1

Synopsys VCS Simulator Requirements

MATLAB and Simulink support Synopsys® VCS® verification tool on Linux using HDL Verifier. Use this recommended version, which has been fully tested against the current release:

Synopsys VCS 2024.09-1

FPGA Verification Requirements

AMD Usage Requirements

MATLAB and Simulink support AMD design tools using HDL Verifier. Use HDL Verifier features with these recommended versions:

AMD Vivado 2024.1

AMD ISE 14.7

AMD ISE is not supported for FPGA data capture or AXI manager.

AMD ISE is required for FPGA boards in the Spartan®-6, Virtex®-4, Virtex-5, and Virtex-6 families.

For tool setup instructions, see Set Up FPGA Design Software Tools.

Intel Quartus Usage Requirements

MATLAB and Simulink support Intel® design tools using HDL Verifier. Use the FIL tools with these recommended versions:

Intel Quartus® Prime Standard 23.1

Intel Quartus Prime Pro 24.2 (supported for Intel Arria® 10, Cyclone® 10 GX, and Intel Agilex® 7 only)

Intel Quartus II 13.1 (supported for Intel Cyclone III boards only)

For tool setup instructions, see Set Up FPGA Design Software Tools.

Microchip Usage Requirements

MATLAB and Simulink support Microchip design tools using HDL Verifier. Use the FIL tools with these recommended versions:

Microchip Libero® SoC v2024.1

These features require a gold or platinum license from Microchip. For tool setup instructions, see Set Up FPGA Design Software Tools.

FPGA Board Connections

Additional boards can be custom added with the FPGA Board Manager. See Supported FPGA Device Families for Board Customization.

JTAG Connection. You can run FPGA-in-the-loop, FPGA data capture, or AXI manager over a JTAG cable to your board. However, each feature requires exclusive use of the JTAG cable, so you cannot run more than one feature at the same time. To allow other tools access to the JTAG cable, such as programming the FPGA, and AMD ChipScope, you must discontinue the JTAG connection in MATLAB. To release the JTAG cable:

FPGA-in-the-loop — Close the Simulink model, or call the

releasemethod of the System object™.FPGA data capture — Close the FPGA Data Capture tool, release the System object, or close the Simulink model.

AXI manager — Call the

releasemethod of the object.

However, the nonblocking capture mode enables you to simultaneously use FPGA data capture and AXI manager, which share a common JTAG interface. For more information, see Simultaneous Use of FPGA Data Capture and AXI Manager.

The JTAG clock frequency depends on the type of cable and the maximum clock frequency supported by the FPGA or SoC board.

| Vendor | Required Hardware | Required Software | JTAG Clock Frequency |

|---|---|---|---|

| Intel | USB Blaster I or USB Blaster II download cable |

| 12 or 24 MHz |

| AMD | Digilent® download cable

|

| 33 MHz |

FTDI USB-JTAG cable

| Install these D2XX drivers:

For the installation guide, see D2XX Drivers from the FTDI Chip website. | 15 MHz | |

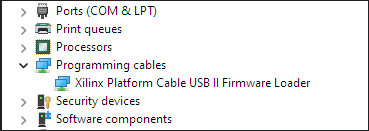

| Platform Cable USB II | Run the driver installer before you use the cable by following these steps:

For more information about driver installation, see Platform Cable USB II Data Sheet (DS593) from the AMD website. | 12 MHz | |

| Microchip | JTAG connection not supported | ||

Note

When simulating your FPGA design through JTAG cable with Simulink or MATLAB, you cannot use any debugging software that requires access to JTAG, such as Vivado Logic Analyzer.

Ethernet Connection. You can run FPGA-in-the-loop, FPGA data capture, or AXI manager over an Ethernet connection. To use FPGA data capture and AXI manager over an Ethernet connection in a single HDL project, connect the FPGA data capture and AXI manager IPs to the same Ethernet MAC Hub IP using different port addresses.

On Zynq® SoC devices you can access the Ethernet interface only through the processing system (PS). To implement Ethernet communication between the host and the hardware board, operation system (OS) and related software applications must run on the PS. Use the hardware setup app to guide you in setting up the SD card and boot the board with a compatible OS.

| Required Hardware | Supported Interfacesa | Required Software |

|---|---|---|

|

| There are no software requirements for an Ethernet connection, but ensure that the firewall on the host computer does not prevent UDP communication. |

a The HDL Verifier Support Package for Microchip FPGA Boards supports only SGMII interfaces. | ||

Note

FPGA data capture and AXI manager support GMII, MII, and SGMII interfaces only. For SGMII interface, you must first properly configure and verify correct usage of the Ethernet 1G/2.5G PCS/PMA or SGMII IP provided by AMD. Then connect the IP to the provided Ethernet MAC Hub. See Ethernet MAC Hub IP.

RMII is supported with Vivado versions older than 2019.2.

Ethernet connection to Virtex-7 VC707 is not supported for Vivado versions older than 2013.4.

AXI manager in HDL Workflow Advisor supports programmable logic (PL) Ethernet only. PS Ethernet is not supported.

FPGA data capture in HDL Workflow Advisor supports the GMII and MII interfaces. The SGMII interface is not supported.

PCI Express Connection. FPGA-in-the-loop over a PCI Express® connection is supported only for 64-bit Windows operating systems.

PCI Express connection for FPGA-in-the-loop and AXI manager is supported for Vivado 2017.4 or newer versions for AMD boards, and Quartus II 15.0 or newer versions for Intel boards.

USB Ethernet Connection. You can run FPGA-in-the-loop, FPGA data capture, or AXI manager over a USB Ethernet connection.

Use a USB 3.0 or USB 2.0 cable based on the type of USB cable your hardware board supports. If you use a USB 2.0 cable for a board that supports USB 3.0, the cable provides lesser data throughput.

| Required Hardware | Required Software |

|---|---|

| USB 3.0 or USB 2.0 cable |

|

Supported FPGA Devices for FPGA Verification

HDL Verifier supports FIL simulation, FPGA data capture, and AXI manager on the devices shown in the following table. The board definition files for these boards are in the Download FPGA Board Support Package. You can add other FPGA boards for use with FIL, FPGA data capture, and AXI manager with FPGA board customization (FPGA Board Customization).

| Device Family | Board | Ethernet | JTAG | PCI Express | USB Ethernet | Comments | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| FIL | Free-Running FIL | FPGA Data Capture | AXI Manager | FIL | FPGA Data Capture | AXI Manager | FIL | FPGA Data Capture | AXI Manager | FIL | Free-Running FIL | FPGA Data Capture | AXI Manager | |||

AMD Artix®-7 | Digilent Nexys™ 4 Artix-7 | ✓ | ✓ | ✓ | ✓ | |||||||||||

| Artix-7 35T Arty FPGA Evaluation Kit | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ||||||||||

AMD Kintex®-7 | Kintex-7 FPGA KC705 Evaluation Kit | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | |||||||

AMD Kintex UltraScale™ | Kintex UltraScale FPGA KCU105 Evaluation Kit | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ||||||||

AMD Kintex UltraScale+™ | Kintex UltraScale+ FPGA KCU116 Evaluation Kit | ✓ | ✓ | ✓ | ✓ | For more information, see PCI Express AXI Manager. | ||||||||||

AMD Spartan-6 | Spartan-6 SP605 Development Board | ✓ | ||||||||||||||

| Spartan-6 SP601 Development Board | ✓ | |||||||||||||||

| XUP Atlys Spartan-6 | ✓ | |||||||||||||||

AMD Spartan-7 | Digilent Arty S7-25 | ✓ | ✓ | ✓ | ||||||||||||

AMD Versal® | Versal AI Core Series VCK190 Evaluation Kit | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | This board supports PS Ethernet. | ||||||||

AMD Virtex UltraScale | Virtex UltraScale FPGA VCU108 Evaluation Kit | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ||||||||

AMD Virtex UltraScale+ | Virtex UltraScale+ FPGA VCU118 Evaluation Kit | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ||||||||

AMD Virtex-7 | Virtex-7 FPGA VC707 Evaluation Kit | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | |||||||

| Virtex-7 FPGA VC709 Connectivity Kit | ✓ | ✓ | ✓ | ✓ | ✓ | |||||||||||

AMD Virtex-6 | Virtex-6 FPGA ML605 Evaluation Kit | ✓ | ||||||||||||||

AMD Virtex-5 | Virtex ML505 Development Board | ✓ | ||||||||||||||

| Virtex ML506 Development Board | ✓ | |||||||||||||||

| Virtex ML507 Development Board | ✓ | |||||||||||||||

| Virtex XUPV5–LX110T Development Board | ✓ | |||||||||||||||

AMD Virtex-4 | Virtex ML401 Development Board | ✓ |

Note Support for Virtex-4 device family will be removed in a future release. | |||||||||||||

| Virtex ML402 Development Board | ✓ | |||||||||||||||

| Virtex ML403 Development Board | ✓ | |||||||||||||||

AMD Zynq | Zynq-7000 SoC ZC702 Evaluation Kit | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | This board supports PS Ethernet. | |||

| Zynq-7000 SoC ZC706 Evaluation Kit | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | This board supports PS Ethernet. | ||||

| ZedBoard™ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | Use the USB port marked "PROG" for programming. This board supports PS Ethernet. | ||||

ZYBO™ Zynq-7000 Development Board | ✓ | ✓ | ✓ | |||||||||||||

| PicoZed™ SDR Development Kit | ✓ | ✓ | ✓ | |||||||||||||

| MiniZed™ | ✓ | ✓ | ||||||||||||||

AMD Zynq UltraScale+ | Zynq UltraScale+ MPSoC ZCU102 Evaluation Kit | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | This board supports PS Ethernet. | |||

Zynq UltraScale+ MPSoC ZCU104 Evaluation Kit | ✓ | ✓ | ✓ | |||||||||||||

Zynq UltraScale+ MPSoC ZCU106 Evaluation Kit | ✓ | ✓ | ✓ | |||||||||||||

Zynq UltraScale+ RFSoC ZCU111 Evaluation Kit | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | This board supports PS Ethernet. | ||||

Zynq UltraScale+ RFSoC ZCU208 Evaluation Kit | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | This board supports PS Ethernet. | ||||

Zynq UltraScale+ RFSoC ZCU216 Evaluation Kit | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | This board supports PS Ethernet. | ||||

| Intel Agilex 7 | Intel Agilex 7 FPGA I-Series Transceiver-SoC Development Kit | ✓ | ✓ | Device part number

This board supports PS Ethernet. | ||||||||||||

Intel Arria II | Arria II GX FPGA Development Kit | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | |||||||||

Intel Arria V | Arria V SoC Development Board - Rev. C | ✓ | ✓ | ✓ | ✓ | |||||||||||

| Arria V Starter Kit | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ||||||||||

Intel Arria 10 | Arria 10 SoC Development Kit | ✓ | ✓ | ✓ | ✓ | ✓ | For Ethernet connection, use Quartus Prime 16.1 or newer. | |||||||||

| Arria 10 GX FPGA Development Kit | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | For Ethernet connection, use Quartus Prime 16.1 or newer. For FIL over PCI Express, only Quartus Prime Standard edition is supported. For PCI Express, Quartus Prime 18.0 is not recommended. | ||||||||

Intel Cyclone IV | Cyclone IV GX FPGA Development Kit | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | |||||||||

| DE2-115 Development and Education Board | ✓ | ✓ | ✓ | ✓ | ✓ | The Altera® DE2-115 FPGA development board has two Ethernet ports. FIL uses only Ethernet 0 port. Make sure that you connect your host computer with the Ethernet 0 port on the board via an Ethernet cable. | ||||||||||

| BeMicro SDK | ✓ | ✓ | ✓ | ✓ | ✓ | |||||||||||

Intel Cyclone III | Cyclone III FPGA Starter Kit | ✓ | ✓ | ✓ | ✓ | Altera Cyclone III boards are supported with Quartus II 13.1 Note Support for Cyclone III device family will be removed in a future release. | ||||||||||

| Cyclone III FPGA Development Kit | ✓ | ✓ | ✓ | ✓ | ✓ | |||||||||||

| Altera Nios II Embedded Evaluation Kit, Cyclone III Edition | ✓ | ✓ | ✓ | ✓ | ✓ | |||||||||||

Intel Cyclone V | Cyclone V GX FPGA Development Kit | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | |||||||||

| Cyclone V SoC Development Kit | ✓ | ✓ | ✓ | ✓ | Rev. C or D | |||||||||||

| Cyclone V GT FPGA Development Kit | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | |||||||||

| Terasic Atlas-SoC Kit / DE0-Nano SoC Kit | ✓ | ✓ | ✓ | ✓ | ||||||||||||

| Arrow® SoCKit Development Kit | ✓ | ✓ | ✓ | ✓ | ||||||||||||

Intel Cyclone 10 LP | Altera Cyclone 10 LP Evaluation Kit | ✓ | ✓ | ✓ | ✓ | |||||||||||

Intel Cyclone 10 GX | Altera Cyclone 10 GX FPGA Development Kit | ✓ | ✓ | ✓ | ✓ | ✓ | Must be used with Quartus Prime Pro. | |||||||||

Intel MAX® 10 | Arrow DECA MAX 10 FPGA Evaluation Kit | ✓ | ✓ | ✓ | ✓ | ✓ | ||||||||||

Intel Stratix® IV | Stratix IV GX FPGA Development Kit | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | |||||||||

Intel Stratix V | DSP Development Kit, Stratix V Edition | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ||||||||

Microchip Polarfire® | Microchip Polarfire Evaluation Kit | ✓ | See Installing Microchip Polarfire Evaluation Kit. | |||||||||||||

Microchip RTG4® | RTG4-DEV-KIT | ✓ | ||||||||||||||

Microchip SmartFusion® 2 | Microchip SmartFusion 2 SoC FPGA Advanced Development Kit | ✓ | See Installing Microchip SmartFusion 2 SoC FPGA Advanced Development Kit. | |||||||||||||

Limitations

For FPGA development boards that have more than one FPGA device, only one such device can be used with FIL.

FIL over PCI Express connection is supported only for 64-bit Windows operating systems.

FPGA Board Support Packages. The FPGA board support packages contain the definition files for all supported boards. You can download one or more vendor-specific packages. To use FIL, download at least one of these packages, or customize your own board definition file. See Create Custom FPGA Board Definition.

To see the list of HDL Verifier support packages, visit HDL Verifier Supported Hardware. To download an FPGA board support package:

On the MATLAB Home tab, in the Environment section, click Add-Ons > Get Hardware Support Packages.

Supported FPGA Device Families for Board Customization

HDL Verifier supports the following FPGA device families for board customization; that is, when you create your own board definition file. See FPGA Board Customization.

Note

The HDL Verifier Support Package for Microchip FPGA Boards does not support board customization.

For board customization, only the JTAG and Ethernet interfaces are supported. The PCI Express and USB Ethernet interfaces are not supported. The availability of interfaces varies by board and depends on the specific custom board you select.

You can select and set up an interface for board customization by using the New FPGA Board Wizard tool. For more information about supported interfaces for board customization, see FPGA-in-the-Loop Interface.

| Device Family | Restrictions | |

|---|---|---|

| AMD | Artix 7 | |

| Kintex 7 | ||

Kintex UltraScale | ||

Kintex UltraScale+ | ||

| Spartan 6 | JTAG is not supported | |

| Spartan 7 | ||

| Virtex 4 | JTAG is not supported Note Support for Virtex-4 device family will be removed in a future release. | |

| Virtex 5 | JTAG is not supported | |

| Virtex 6 | JTAG is not supported | |

| Virtex 7 | ||

Virtex UltraScale | ||

Virtex UltraScale+ | ||

| Zynq 7000 | Ethernet is not supported | |

Zynq UltraScale+ | Ethernet is not supported | |

| Versal AI Core | Ethernet is not supported | |

| Intel | Arria II GX | |

| Arria V | ||

| Arria 10 | ||

| Cyclone III |

Note Support for Cyclone III device family will be removed in a future release. | |

| Cyclone IV GX | ||

| Cyclone IV E | ||

| Cyclone V | ||

| Cyclone 10 LP | ||

| Cyclone 10 GX | ||

| MAX 10 | ||

| Stratix IV | ||

| Stratix V | ||

| Agilex 7 | ||

UVM and DPI Component Generation Requirements

UVM and DPI component generation workflows supports the same versions of these HDL simulators as for cosimulation:

Siemens® Questa

Siemens ModelSim™

AMD Vivado simulator (not supported for

uvmbuild)Synopsys VCS (Linux only)

Cadence Xcelium (Linux only)

For cross platform workflow, see Generate Cross-Platform DPI Components or Generate Cross-Platform UVM Components.

UVM generation requires a UVM Reference Implementation, available for download from the UVM standard website. This feature is tested with the default shipped version for each supported simulator.

UVM Framework (UVMF) requires Siemens UVMF tools. Use this recommended version, which has been fully tested against the current release:

Siemens UVM Framework release 2023.4_2

Note

When you run a DPI component in ModelSim 10.5b on Debian® 8.3, you may encounter a library incompatibility error:

** Warning: ** Warning: (vsim-7032) The 64-bit glibc RPM does not appear to be installed on this machine. Calls to gcc may fail. ** Fatal: ** Error: (vsim-3827) Could not compile 'STUB_SYMS_OF_fooour.so':

Set the Build configuration to

Faster Runs.Or, set the Build configuration to

Specifyand specify the compiler flag-O3.

TLM Generation Requirements

With the current release, TLMG includes support for:

Compilers:

Visual Studio®: VS2008, VS2010, VS2012, VS2013, VS2015, and VS2017

Windows 7.1 SDK

gcc 6.3

SystemC™:

SystemC 2.3.1 (TLM included)

You can download SystemC and TLM libraries at https://www.accellera.org/. Consult the Accellera Systems Initiative website for information about how to build these libraries after downloading.

System C Modeling Library (SCML):

SCML 2.4.3

You can download SCML from https://www.synopsys.com.

Troubleshooting

Path exceeds Windows limit. When executing the HDL Verifier product examples on a Windows machine there can be errors caused by a Windows path limit of 260 characters. Sometimes the condition can be caught and you may receive an error such as the following:

Build failed because the build file name(s) exceed the Windows limit of

260 characters. Build from a working directory with a shorter path, to allow

build files to be created with shorter filenames.

Often, however, the long path is created during the execution of third party tools such as Vivado or Quartus and the resulting error from those tools will seem to be unrelated. Some examples for such errors are:

ERROR: [Common 17-680] Path length exceeds 260-Byte maximum allowed by Windows: c:\Users\user\OneDrive - MathWorks\Documents\MATLAB\Examples\R2022a\xilinxfpgaboards\ ZynqEthernet\ethernetaximanagerzynq.srcs\sources_1\bd\design_1\ip\design_1_mig_7series_0_0\ _tmp\/design_1_mig_7series_0_0/example_design/rtl/traffic_gen/mig_7series_v4_2_axi4_tg.v Please consider using the OS subst command to shorten the path length by mapping part of the path to a virtual drive letter. See Answer Record AR52787 for more information. Resolution: In Windows 7 or later, the mklink command can also be used to create a symbolic link and shorten the path.

WARNING: [Vivado 12-8222] Failed run(s) : 'clk_wiz_0_synth_1', 'simcycle_fifo_synth_1' wait_on_run: Time (s): cpu = 00:00:00 ; elapsed = 00:02:16 . Memory (MB): peak = 1636.988 ; gain = 0.000 # if {[get_property PROGRESS [get_runs synth_1]] != "100%"} { # error "ERROR: Synthesis failed"Error (12006): Node instance "ident" instantiates undefined entity "alt_sld_fab_altera_connection_identification_hub_171_gdd6b5i" Ensure that required library paths are specified correctly, define the specified entity, or change the instantiation. If this entity represents Intel FPGA or third-party IP, generate the synthesis files for the IP.

A long path may be suspected when the root folder for running the example is already fairly long, such as over 100 characters.

In both the detected and undetected long path scenarios, to avoid the errors, use one of these methods:

Map the example directory to a shorter letter drive alias. For example, the following will eliminate 122 characters from the path, allowing much more headroom for the 260 character limit.

cmd> subst W: “C:\Users\janedoe\OneDrive - Personal\Documents\MATLAB\Examples\R2021b\hdlverifier\GettingStartedWithSimulinkHDLCosimExample”After opening an example, copy the example directory to a directory with a short name (such as

/tmp).

Unrecognized Function. When you have more than one version of a third party tool, but only one

version is licensed (or when only one version is supported by HDL Verifier), MATLAB might error out with "Unrecognized function"

when calling that tool.

To make sure MATLAB opens the licensed version of your simulator you must:

Set the correct license variable with the path to the licence file.

Make sure that the

Pathvariable points to your licensed executable version.