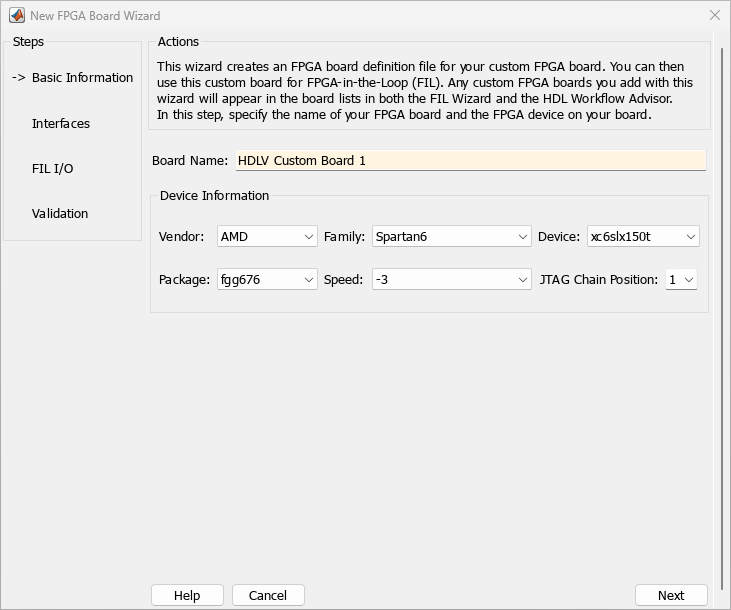

New FPGA Board Wizard

Create, configure, and add custom board for FPGA-in-the-loop workflows

Description

Create, configure, and add custom FPGA boards for FPGA-in-the-loop workflows.

Step through the workflow to enter the required information to add a board to the FPGA board list. This list applies to FPGA-in-the-loop (FIL) workflows. Review FPGA Board Requirements before adding an FPGA board to make sure that it is compatible with the workflow for which you want to use it.

Adding Boards Once for Multiple Users

To add new boards globally, follow these instructions. To access a board added globally, all users must be using the same MATLAB® installation.

Create the following folder:

matlabroot/toolbox/shared/eda/board/boardfilesCopy the board description XML file to the

boardfilesfolder.After copying the XML file, restart MATLAB. The new board appears in the FPGA board list for the FIL workflow.

All boards under this folder show-up in the FPGA board list automatically for users with the same MATLAB installation. You do not need to use FPGA Board Manager to add these boards again.

Open the New FPGA Board Wizard

FPGA Board Manager: click Create Custom Board.

Examples

Parameters

Version History

Introduced in R2012b