FPGA Data Capture

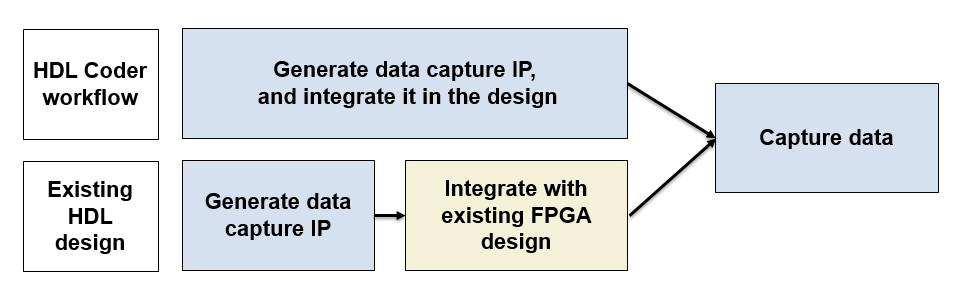

Use FPGA data capture to observe signals from your design while the design is running on the FPGA. This feature captures a window of signal data from the FPGA and returns the data to MATLAB® or Simulink®. To capture the signals, HDL Verifier™ generates an IP core that you must integrate into your HDL project and deploy to the FPGA along with the rest of your design. HDL Verifier also generates a tool, System object™, and Simulink model that communicate with the FPGA and return the data to MATLAB or Simulink.

To capture FPGA data:

Generate customized components and an IP core. Specify port names and sizes for the generated IP. These ports connect to the signals you want to capture, and the signals you want to use as triggers to control when the capture occurs.

Integrate the generated IP into your FPGA design and deploy the design to your FPGA board.

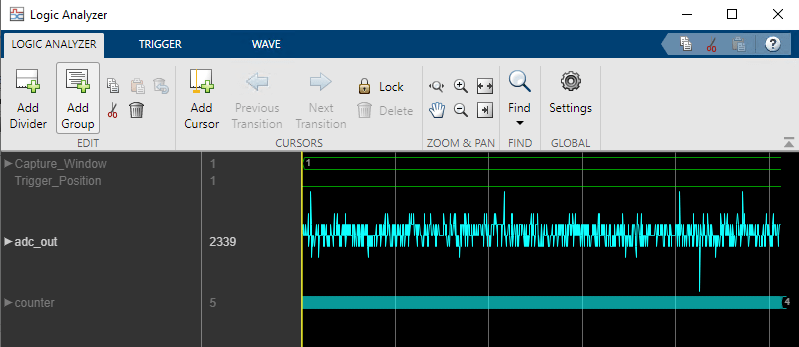

Use the generated tool, System object, or Simulink model to capture data for analysis, verification, or display. You can configure a trigger condition to control when the capture occurs and a capture condition to control which data to capture.

Tools

| FPGA Data Capture Component Generator | Configure and generate FPGA data capture components |

| FPGA Data Capture | Capture data from live FPGA into MATLAB workspace interactively |

Functions

hdlverifier.FPGADataReader | Capture data from live FPGA into MATLAB workspace |

generateFPGADataCaptureIP | Open FPGA Data Capture Component Generator |

Blocks

| FPGA Data Reader | Capture data from live FPGA into Simulink model |

Topics

- Data Capture Workflow

Capture signal data from a design running on an FPGA.

- Triggers

Use trigger conditions to capture data around specific events on the FPGA.

- Capture Conditions

Use capture condition to control which data to capture from the FPGA.

- Design Considerations for Data Capture

Signal, timing, and interface limitations for FPGA data capture.