FPGA Data Capture Component Generator

Configure and generate FPGA data capture components

Description

Add-On Required: This feature requires one of these add-ons.

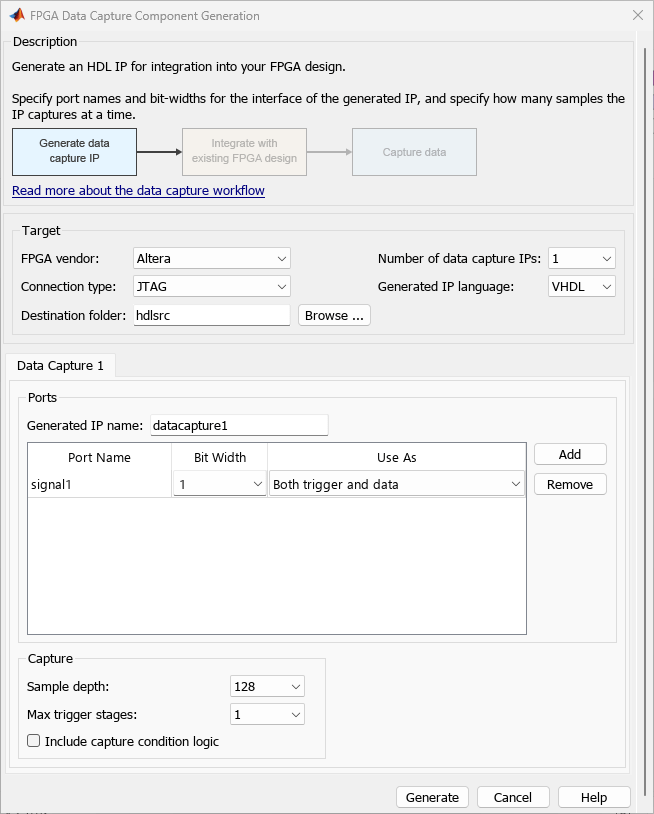

The FPGA Data Capture Component Generator tool configures and generates components for capturing data from a design running on an FPGA. The generated components capture a window of signal data from the FPGA and return the data to MATLAB® or Simulink®.

To use this tool, you must have an existing HDL design and FPGA project. To capture the signals, HDL Verifier™ generates the IP core that you must integrate into your HDL project, and deploy to the FPGA along with the rest of your design.

The Generate button in this tool generates these components:

HDL IP core, for integration into your FPGA design. Connect the signals you want to capture and use as triggers, and connect a clock and clock enable.

Generation report, with list of generated files and instructions for next steps.

Tool to set capture parameters and capture data to the MATLAB workspace. See FPGA Data Capture.

Customized version of the

hdlverifier.FPGADataReaderSystem object™ that provides an alternative, programmatic, way to configure and capture data.Simulink model that contains a customized FPGA Data Reader block. This model streams the captured signals into the Logic Analyzer waveform viewer. You can also use the Scope block to display the signals.

MAT file in the

generatedIPName_generation_settings.matgeneratedIPNamegenerateFPGADataCaptureIPfunction.AMD® only — Tcl file,

insertFPGADataCaptureIP.tcl, for a non-Versal® device. Use this Tcl script to insert the generated HDL IP core along with either the JTAG Debug Hub IP (for a JTAG connection), the Ethernet MAC Hub IP (for a PL Ethernet connection), or only the HDL IP core (for a PS Ethernet or USB Ethernet connection) into the Vivado® block design and establish the required connections.AMD only — Tcl file,

insertVersalFPGADataCaptureIP.tcl, for a Versal device. Use this Tcl script to insert the generated HDL IP core, the JTAG Debug Hub IP, and the CIPS IP into the Vivado block design and establish the required connections.

For a workflow overview, see Data Capture Workflow.

For an AMD device over a JTAG connection, you can observe signals operating at different clock rates by using multiple data capture IPs. For more information about how to generate and integrate multiple data capture IPs into your FPGA design, see Capture Asynchronous Data.

Open the FPGA Data Capture Component Generator

Simulink Toolstrip: Access the HDL Verifier tab by opening the HDL Verifier app from the Apps tab. On the HDL Verifier tab, on the HDL Verifier Mode pane, select FPGA Data Capture (FDC). Then, under Generate:

To open the tool, click Generate FDC Components.

To open the tool with the preloaded parameters of a design you have already generated and saved in a MAT file, click Generate FDC Components from Previous Settings.

MATLAB Command Prompt:

To open the tool, enter this command.

generateFPGADataCaptureIP

To open the tool with the preloaded parameters of the most recent design, enter this command.

generateFPGADataCaptureIP('restore',true);To open the tool with the preloaded parameters of a design you have already generated and saved in a MAT file, enter this command.

WheregenerateFPGADataCaptureIP('datacapture1_generation_settings.mat');datacapture1

Examples

Parameters

Version History

Introduced in R2017a