resetState

Class: dlhdl.Workflow

Namespace: dlhdl

Syntax

resetState(workflowObject)

Description

resetState( resets the state

parameters of the deployed neural network. Use this method to reset the state of a recurrent

neural network, such as an LSTM network.workflowObject)

Input Arguments

Deep learning network deployment options, specified as a

dlhdl.Workflow object.

Examples

This example shows how to create, compile, and deploy a long short-term memory (LSTM) network trained on waveform data by using the Deep Learning HDL Toolbox™ Support Package for Xilinx FPGA and SoC. Use the deployed network to predict future values by using open-loop and closed-loop forecasting. Use MATLAB® to retrieve the prediction results from the target device.

Waveform Data Network

The network attached to this example was trained using the Time Series Forecasting Using Deep Learning. This example uses the WaveformData.mat data set, which contains 2000 synthetically generated waveforms of varying lengths with three channels. This example uses a trained LSTM network to forecast future values of the waveforms given the values from the previous time steps using both closed loop and open loop forecasting.

Prerequisites

Xilinx® Zynq® Ultrascale+™ ZCU102 SoC development kit

Load the Pretrained Network

To load the LSTM network enter:

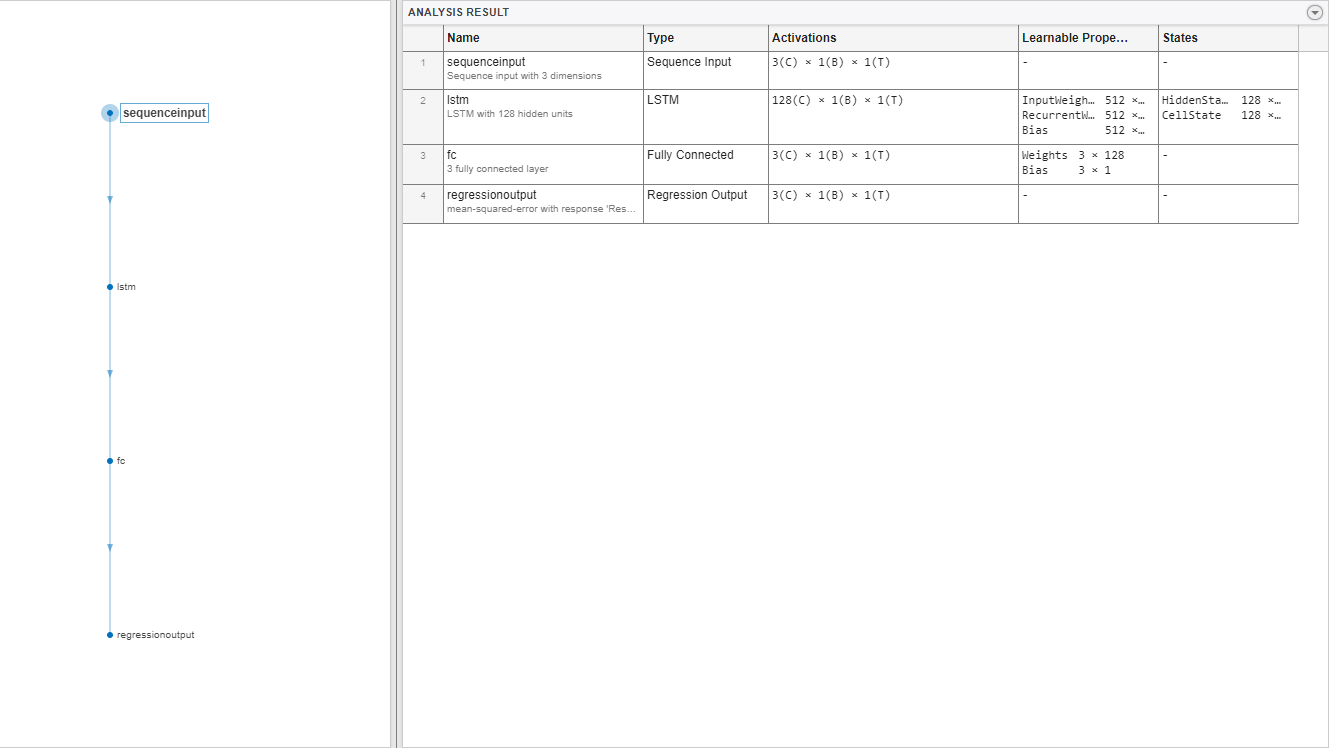

load WaveformForcastingNetUse the analyzeNetwork function to obtain information about the network layers. The function returns a graphical representation of the network that contains detailed parameter information for every layer in the network.

analyzeNetwork(net)

Define FPGA Board Interface

Define the target FPGA board programming interface by using the dlhdl.Target object. Specify that the interface is for a Xilinx board with an Ethernet interface.

To create the target object, enter:

hTarget = dlhdl.Target('Xilinx','Interface','Ethernet');

To use the JTAG interface, install Xilinx™ Vivado™ Design Suite 2024.1. To set the Xilinx Vivado toolpath, enter:

hdlsetuptoolpath('ToolName', 'Xilinx Vivado', 'ToolPath', 'C:\Xilinx\Vivado\2024.1\bin\vivado.bat'); hTarget = dlhdl.Target('Xilinx','Interface','JTAG');

Prepare Network for Deployment

Prepare the network for deployment by creating a dlhdl.Workflow object. Specify the network and the bitstream name. Ensure that the bitstream name matches the data type and the FPGA board. In this example the target FPGA board is the Xilinx ZCU102 SOC board. The bitstream uses the single data type.

hW = dlhdl.Workflow('network', net, 'Bitstream', 'zcu102_lstm_single','Target',hTarget);

Tu run the example on the Xilinx ZC706 board, enter:

hW = dlhdl.Workflow('Network', net, 'Bitstream', 'zc706_lstm_single','Target',hTarget);

Compile the LSTM Network

Run the compile method of the dlhdl.Workflow object to compile the network and generate the instructions, weights, and biases for deployment. The total number of frames exceeds the default value of 30. Set the InputFrameNumberLimit name-value argument to 1000 to run predictions in chunks of 1000 frames to prevent timeouts.

dn = compile(hW,'InputFrameNumberLimit',1000)### Compiling network for Deep Learning FPGA prototyping ...

### Targeting FPGA bitstream zcu102_lstm_single.

### An output layer called 'Output1_fc' of type 'nnet.cnn.layer.RegressionOutputLayer' has been added to the provided network. This layer performs no operation during prediction and thus does not affect the output of the network.

### The network includes the following layers:

1 'sequenceinput' Sequence Input Sequence input with 3 channels (SW Layer)

2 'lstm' LSTM LSTM with 128 hidden units (HW Layer)

3 'fc' Fully Connected Fully connected layer with output size 3 (HW Layer)

### Notice: The layer 'sequenceinput' with type 'nnet.cnn.layer.ImageInputLayer' is implemented in software.

### Compiling layer group: lstm.wi ...

### Compiling layer group: lstm.wi ... complete.

### Compiling layer group: lstm.wo ...

### Compiling layer group: lstm.wo ... complete.

### Compiling layer group: lstm.wg ...

### Compiling layer group: lstm.wg ... complete.

### Compiling layer group: lstm.wf ...

### Compiling layer group: lstm.wf ... complete.

### Compiling layer group: fc ...

### Compiling layer group: fc ... complete.

### Allocating external memory buffers:

offset_name offset_address allocated_space

_______________________ ______________ __________________

"InputDataOffset" "0x00000000" "16.0 kB"

"OutputResultOffset" "0x00004000" "16.0 kB"

"SchedulerDataOffset" "0x00008000" "868.0 kB"

"SystemBufferOffset" "0x000e1000" "20.0 kB"

"InstructionDataOffset" "0x000e6000" "4.0 kB"

"FCWeightDataOffset" "0x000e7000" "272.0 kB"

"EndOffset" "0x0012b000" "Total: 1196.0 kB"

### Network compilation complete.

dn = struct with fields:

weights: [1×1 struct]

instructions: [1×1 struct]

registers: [1×1 struct]

syncInstructions: [1×1 struct]

constantData: {}

ddrInfo: [1×1 struct]

resourceTable: [6×2 table]

Program Bitstream onto FPGA and Download Network Weights

To deploy the network on the Xilinx ZCU102 SoC hardware, run the deploy function of the dlhdl.Workflow object. This function uses the output of the compile function to program the FPGA board by using the programming file. It also downloads the network weights and biases. The deploy function starts programming the FPGA device and displays progress messages, and the required time to deploy the network.

deploy(hW)

### FPGA bitstream programming has been skipped as the same bitstream is already loaded on the target FPGA. ### Deep learning network programming has been skipped as the same network is already loaded on the target FPGA.

Test Network

Prepare the test data for prediction. Normalize the test data using the statistics calculated from the training data. To forecast the values of future time steps of a sequence, specify the targets as the test sequences with values shifted by one time step. In other words, at each time step of the input sequence, the LSTM network learns to predict the value of the next time step. Specify the predictors as the test sequences without the final time step.

load WaveformData.mat data = cellfun(@(x)x',data,UniformOutput=false); numChannels = size(data{1},1); numObservations = numel(data); idxTrain = 1:floor(0.9*numObservations); idxTest = floor(0.9*numObservations)+1:numObservations; dataTrain = data(idxTrain); dataTest = data(idxTest); for n = 1:numel(dataTrain) X = dataTrain{n}; XTrain{n} = X(:,1:end-1); TTrain{n} = X(:,2:end); end muX = mean(cat(2,XTrain{:}),2); sigmaX = std(cat(2,XTrain{:}),0,2); muT = mean(cat(2,TTrain{:}),2); sigmaT = std(cat(2,TTrain{:}),0,2); for n = 1:size(dataTest,1) X = dataTest{n}; XTest{n} = ((X(:,1:end-1) - muX) ./ sigmaX)'; TTest{n} = ((X(:,2:end) - muT) ./ sigmaT)'; end

Make predictions using the test data.

YTest = hW.predict(XTest{1},Profile ='on');### Resetting network state.

### Finished writing input activations.

### Running a sequence of length 115.

Deep Learning Processor Profiler Performance Results

LastFrameLatency(cycles) LastFrameLatency(seconds) FramesNum Total Latency Frames/s

------------- ------------- --------- --------- ---------

Network 37304 0.00015 115 4317203 6659.4

memSeparator_2 276 0.00000

memSeparator_0 167 0.00000

lstm.wi 8320 0.00003

lstm.wo 8275 0.00003

lstm.wg 8330 0.00003

lstm.wf 8285 0.00003

lstm.sigmoid_1 288 0.00000

lstm.sigmoid_3 287 0.00000

lstm.tanh_1 305 0.00000

lstm.sigmoid_2 289 0.00000

lstm.multiplication_1 390 0.00000

lstm.multiplication_2 341 0.00000

lstm.c_add 331 0.00000

lstm.tanh_2 298 0.00000

lstm.multiplication_3 328 0.00000

fc 559 0.00000

memSeparator_1 235 0.00000

* The clock frequency of the DL processor is: 250MHz

To evaluate the accuracy, calculate the root mean squared error (RMSE) between the predictions and the target for each test sequence.

for i = 1:size(YTest,2) rmse(i) = sqrt(mean((YTest(1,i) - TTest{1}(1,i)).^2,"all")); end

Visualize the errors in a histogram. Lower values indicate greater accuracy.

figure histogram(rmse) xlabel("RMSE") ylabel("Frequency")

Calculate the mean RMSE over all test observations.

mean(rmse)

ans = single

0.8385

Forecast Future Time Steps

To forecast the values of multiple future time steps, when given an input time series or sequence, use the predict function. This function predicts time steps one at a time and updates the network state at each prediction. For each prediction, use the previous prediction as the input to the function.

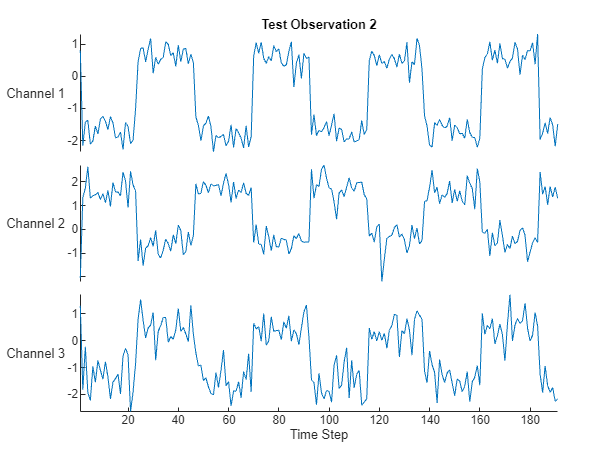

Visualize one of the test sequences in a plot.

idx = 2;

X = XTest{idx};

T = TTest{idx};

figure

stackedplot(X,DisplayLabels="Channel " + (1:numChannels))

xlabel("Time Step")

title("Test Observation " + idx)

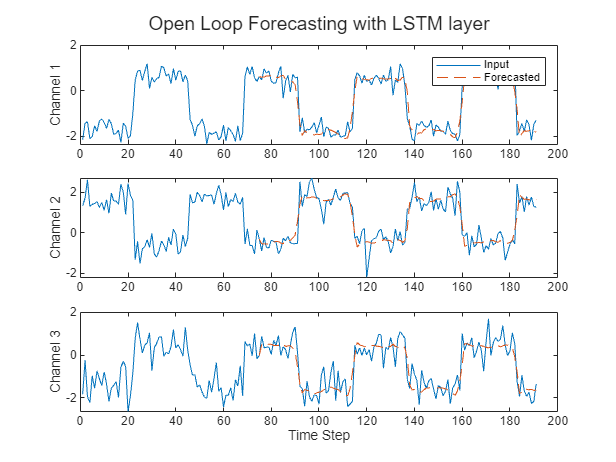

Open-Loop Forecasting

Open-loop forecasting predicts the next time step in a sequence using only the input data. When making predictions for subsequent time steps, you collect the true values form your data source and use those as input. For example, suppose that you want to predict the value for time step of a sequence by using data collected in time steps 1 through . To make predictions for time step , wait until you record the true value for time step and use that value as input to make the next prediction. Use open-loop forecasting when you have true values to provide to the network before making the next prediction.

Initialize the network state by resetting the state using the resetState function, then make an initial prediction using the first few time steps of the input data. Update the network state by using the first 75 time steps of the input data.

resetState(hW)

offset = 75;

[~,~] = hW.predict(X(1:offset,:),KeepState=true,Profile='on'); ### Resetting network state.

### Finished writing input activations.

### Running a sequence of length 75.

Deep Learning Processor Profiler Performance Results

LastFrameLatency(cycles) LastFrameLatency(seconds) FramesNum Total Latency Frames/s

------------- ------------- --------- --------- ---------

Network 37253 0.00015 75 2815915 6658.6

memSeparator_2 238 0.00000

memSeparator_0 166 0.00000

lstm.wi 8330 0.00003

lstm.wo 8283 0.00003

lstm.wg 8281 0.00003

lstm.wf 8284 0.00003

lstm.sigmoid_1 288 0.00000

lstm.sigmoid_3 366 0.00000

lstm.tanh_1 306 0.00000

lstm.sigmoid_2 290 0.00000

lstm.multiplication_1 324 0.00000

lstm.multiplication_2 342 0.00000

lstm.c_add 331 0.00000

lstm.tanh_2 372 0.00000

lstm.multiplication_3 327 0.00000

fc 491 0.00000

memSeparator_1 234 0.00000

* The clock frequency of the DL processor is: 250MHz

To forecast further predictions, loop over time steps and update the network state by using the predict function and setting the KeepState name-value argument to true. Forecast values for the remaining time steps of the test observation by looping over the time steps of the input data and using them as input to the network. The first prediction is the value that corresponds to the time step offset + 1.

numTimeSteps = size(X,1);

numPredictionTimeSteps = numTimeSteps - offset;

Y = hW.predict(X(offset+1:offset+numPredictionTimeSteps,:),KeepState=true,Profile='on');### Finished writing input activations.

### Running a sequence of length 116.

Deep Learning Processor Profiler Performance Results

LastFrameLatency(cycles) LastFrameLatency(seconds) FramesNum Total Latency Frames/s

------------- ------------- --------- --------- ---------

Network 37148 0.00015 116 4354341 6660.0

memSeparator_2 237 0.00000

memSeparator_0 167 0.00000

lstm.wi 8306 0.00003

lstm.wo 8277 0.00003

lstm.wg 8284 0.00003

lstm.wf 8290 0.00003

lstm.sigmoid_1 293 0.00000

lstm.sigmoid_3 287 0.00000

lstm.tanh_1 305 0.00000

lstm.sigmoid_2 289 0.00000

lstm.multiplication_1 324 0.00000

lstm.multiplication_2 407 0.00000

lstm.c_add 331 0.00000

lstm.tanh_2 298 0.00000

lstm.multiplication_3 327 0.00000

fc 491 0.00000

memSeparator_1 235 0.00000

* The clock frequency of the DL processor is: 250MHz

Compare the predictions with the target values.

figure t = tiledlayout(numChannels,1); title(t,"Open Loop Forecasting with LSTM layer") for i = 1:numChannels nexttile plot(T(:,i)) hold on plot(offset:numTimeSteps,[T(offset, i) Y(:, i)'],'--') ylabel("Channel " + i) end xlabel("Time Step") nexttile(1) legend(["Input" "Forecasted"])

Closed-Loop Forecasting

Closed-loop forecasting predicts subsequent time steps in a sequence by using the previous predictions as input. In this case, the model does not require the true values to make the prediction. For example, suppose that you want to predict the value for time steps through of the sequence by using data collected in time steps 1 through . To make predictions for time step , use the predicted value for time step as input. Use closed-loop forecasting to forecast multiple subsequent time steps or when you do not have true values to provide to the network before making the next prediction.

Initialize the network state by resetting the state using the resetState function, then make an initial prediction, Z, using the first few time steps of the input data. Update the network state by using the first 75 time steps of the input data.

resetState(hW)

[Z, ~] = predict(hW,X,KeepState=true,Profile='on');### Resetting network state.

### Finished writing input activations.

### Running a sequence of length 191.

Deep Learning Processor Profiler Performance Results

LastFrameLatency(cycles) LastFrameLatency(seconds) FramesNum Total Latency Frames/s

------------- ------------- --------- --------- ---------

Network 37145 0.00015 191 7169387 6660.3

memSeparator_2 237 0.00000

memSeparator_0 167 0.00000

lstm.wi 8314 0.00003

lstm.wo 8282 0.00003

lstm.wg 8281 0.00003

lstm.wf 8282 0.00003

lstm.sigmoid_1 290 0.00000

lstm.sigmoid_3 288 0.00000

lstm.tanh_1 305 0.00000

lstm.sigmoid_2 289 0.00000

lstm.multiplication_1 324 0.00000

lstm.multiplication_2 404 0.00000

lstm.c_add 330 0.00000

lstm.tanh_2 298 0.00000

lstm.multiplication_3 328 0.00000

fc 491 0.00000

memSeparator_1 235 0.00000

* The clock frequency of the DL processor is: 250MHz

To forecast further predictions, loop over time steps and update the network state by using the predict function and setting the KeepState name-value argument to true. Forecast the next 200 time steps by iteratively passing the previously predicted value to the network. Because the network does not require the input data to make any further predictions, you can specify any number of time steps to forecast.

numPredictionTimeSteps = 200; % Z = Z'; Xt = Z(end,:); Y = zeros(numPredictionTimeSteps, numChannels); fprintf("Run %d predictions:\n",numPredictionTimeSteps);

Run 200 predictions:

for t = 1:numPredictionTimeSteps fprintf("."); [Y(t,:),~] = predict(hW,Xt,KeepState=true); Xt = Y(t,:); end

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

.

### Finished writing input activations. ### Running a sequence of length 1.

Visualize the forecasted values in a plot.

offset = size(X,1); numTimeSteps = offset + numPredictionTimeSteps; figure t = tiledlayout(numChannels,1); title(t,"Closed Loop Forecasting with LSTM layer") for i = 1:numChannels nexttile plot(T(1:offset, i)) hold on plot(offset:numTimeSteps,[T(offset, i) Y(:, i)'],'--') ylabel("Channel " + i) end xlabel("Time Step") nexttile(1) legend(["Input" "Forecasted"])

Closed-loop forecasting allows you to forecast an arbitrary number of time steps, but can be less accurate when compared to open-loop forecasting because the network does not have access to the true values during the forecasting process.

Version History

Introduced in R2022b

See Also

activations | compile | deploy | predict | predictAndUpdateState

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

选择网站

选择网站以获取翻译的可用内容,以及查看当地活动和优惠。根据您的位置,我们建议您选择:。

您也可以从以下列表中选择网站:

如何获得最佳网站性能

选择中国网站(中文或英文)以获得最佳网站性能。其他 MathWorks 国家/地区网站并未针对您所在位置的访问进行优化。

美洲

- América Latina (Español)

- Canada (English)

- United States (English)

欧洲

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)