Sigma-Delta A/D 转换

此示例说明如何通过实现 Sigma-Delta 算法对模数转换进行建模。

过采样的 Sigma-Delta A/D 转换器是一种噪声成形量化器。噪声成形的主要目的是重构量化噪声的频谱,使得大部分噪声从相关频带(如语音应用的音频带)中滤除。主要目标是用位换采样。即,增大采样率,但减小每个采样的位数。由此增加的量化噪声通过噪声成形量化器进行补偿。此量化器将添加的量化噪声推出相关频带,从而保持所需的信号质量水平。位数的减少简化了 A/D 和 D/A 转换器的结构。

此示例包括两个模型。在这些模型中,模拟输入首先由抗混叠预滤波器(其结构由于过采样而得到简化)进行预滤波。对输入信号进行 64 倍的过采样。Integrator、1-Bit Quantizer 和 Zero-Order Hold 模块构成一个两级模数转换器 (ADC)。然后,从模拟输入中减去 Zero-Order Hold 模块的输出。反馈或逼近环会导致对 ADC 生成的量化噪声进行高通滤波,从而将其能量推向较高频率 (64*fs/2) 并远离相关信号带。

抽取阶段会降低采样率,使其回到 8 kHz。在此过程中,抽取阶段去除由反馈环引入的高频量化噪声,并去除简单模拟预滤波器未去除的 fs/2 (4 KHz) 以外的任何不需要的频率分量。

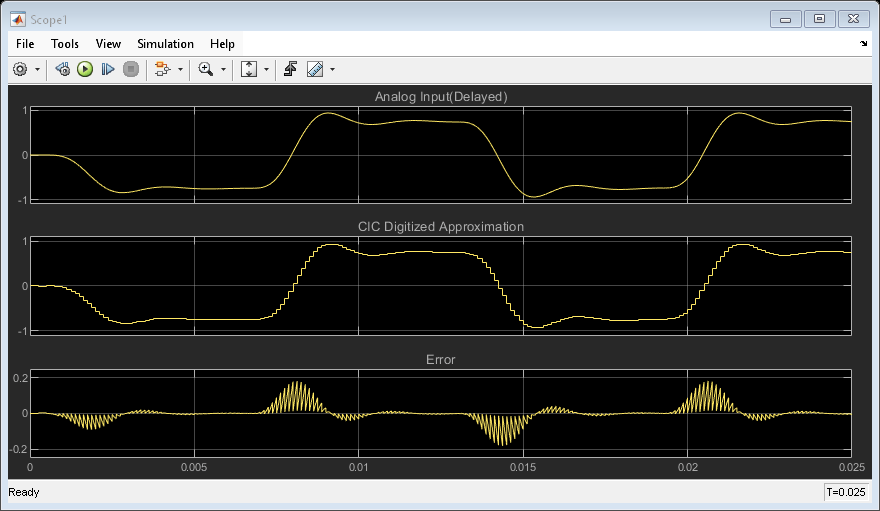

Scope 模块显示模拟输入信号、信号的数字化逼近以及两个信号之间的误差。打开模型并运行它们。您将看到数字化信号是模拟输入信号的紧密逼近。

浮点模型

使用 open_system 命令打开模型 dspsdadc.slx。

定点模型

使用 open_system 命令打开模型 dspsdadc_fixpt.slx。

抽取器设计

此示例中的两个模型说明两种可能的抽取器设计解决方案。

浮点版本模型使用由三个多相 FIR 抽取器组成的级联。与单个抽取器相比,此方法通过使用低阶滤波器减少计算和内存需求。每个抽取器阶段将采样率降低为原来的四分之一。滤波器引入的延迟用于设置 Transport Delay 模块中适当的时滞参数。由于滤波器的群延迟,三个 FIR Decimation 模块各引入 16 个采样的延迟。实际值为 15.5 个采样,向上舍入到最近的整数个采样。由于抽取操作,三个滤波器引入的总延迟如下:16(第一个滤波器)+ 4*16(第二个滤波器)+ 16*16(第三个滤波器)得到最终总延迟 336。时滞参数的分母是模型的基本速率 (512 kHz)。

定点版本使用一个五节 CIC 抽取器将采样率同样降低为原来的 1/64。虽然不如 FIR 抽取器灵活,但 CIC 抽取器的优点是不需要任何乘法运算。它仅使用加法、减法和延迟就能实现。因此,在计算资源有限的硬件实现中,它是很好的选择。CIC 抽取引入 158 个采样的延迟,这是滤波器的群延迟 (157.5) 向上舍入到最近的整数的结果。此值用于 Multistage CIC Processing Delay 模块的时滞参数中。

参考

[1] Orfanidis, S. J. Introduction To Signal Processing, Prentice Hall, 1996.

另请参阅

Signal Generator (Simulink) | Analog Filter Design | FIR Decimation | CIC Decimation | Integrator (Simulink) | Sign (Simulink) | Zero-Order Hold (Simulink) | Transport Delay (Simulink) | Scope (Simulink)