CIC Decimation

Decimate signal using cascaded integrator-comb filter

Libraries:

DSP System Toolbox /

Filtering /

Multirate Filters

DSP System Toolbox HDL Support /

Filtering

Description

The CIC Decimation block performs a sample rate decrease (decimation) on an input signal by an integer factor. Cascaded Integrator-Comb (CIC) filters are a class of linear phase FIR filters comprised of a comb part and an integrator part.

The block supports real and complex fixed-point inputs. In its normal mode of operation, the CIC Decimation block allows the adder’s numeric values to overflow and wrap around [1] [3]. The Fixed-Point infrastructure then causes overflow warnings to appear on the command line. This overflow is of no consequence.

The CIC Decimation block requires a Fixed-Point Designer™ license.

Examples

GSM Digital Down Converter in Simulink

Simulate steady-state behavior of a fixed-point digital down converter for GSM (Global System for Mobile) baseband conversions. The example model uses blocks from Simulink® and the DSP System Toolbox™ to emulate the operation of the TI GC4016 Quad Digital Down Converter (DDC).

Ports

Input

Data input, specified as a vector or matrix. The number of input rows must be a multiple of the decimation factor.

If the input is fixed point, it must be a signed integer or a signed fixed point value with a power-of-two slope and zero bias.

Data Types: int8 | int16 | int32 | int64 | fixed point

Complex Number Support: Yes

Output

CIC decimated output, returned as a vector or a matrix. The data type of the output is determined by the settings in the block dialog. The complexity of the output matches that of the input. The number of output rows is (1/R)✕Num, where R is the decimation factor and Num is the number of input rows.

Data Types: int8 | int16 | int32 | int64 | fixed point

Complex Number Support: Yes

Parameters

Source of the filter information, specified as one of the following:

Dialog parameters— Enter information about the filter, such as Decimation factor (R), Differential delay (M) and Number of sections (N), in the block dialog.Filter object— Specify the filter using adsp.CICDecimatorSystem object™.

Different items appear on the CIC Decimation block dialog depending

on whether you select Dialog parameters or

Filter object in the Coefficient

source parameter.

Decimation factor of the filter, specified as an integer greater than 1.

Dependencies

This parameter appears when you set Coefficient source to

Dialog parameters.

Specify the differential delay of the comb part of the filter, M, as a positive integer. For more details, see CIC Decimation Filter.

Dependencies

This parameter appears when you set Coefficient source to

Dialog parameters.

Specify the number of filter sections. The number you specify determines the number of sections in either the comb part of the filter or the integrator part of the filter. This value does not represent the total number of sections in the comb and integrator parts combined.

Dependencies

This parameter appears when you set Coefficient source to

Dialog parameters.

Choose how you specify the fixed-point word length and fraction length of the filter sections and/or output:

Full precision— The word and fraction lengths of the filter sections and outputs are automatically selected for you. All word lengths (WL) are set to:where,

I — Input word length

M — Differential delay

N — Number of sections

R — Decimation factor

All fraction lengths are set to the input fraction length.

Minimum section word lengths— Specify the word length of the filter output in the Output word length parameter. The block automatically selects the word lengths of the filter sections and all fraction lengths such that each of the section word lengths is as small as possible. The precision of each filter section is less than inFull precisionmode, but the range of each section is preserved.Specify word lengths— Specify the word lengths of the filter sections and output in the Section word lengths and Output word length parameters. The block automatically selects fraction lengths for the filter sections and output such that the range of each section is preserved when the least significant bits are discarded.Binary point scaling— Specify the word and fraction lengths of the filter sections and output in the Section word lengths, Section fraction lengths, Output word length, and Output fraction length parameters.

Dependencies

This parameter appears when you set Coefficient source to

Dialog parameters.

Word lengths of filter sections, specified as a scalar or a vector of length equal to 2N, where N is the number of filter sections. The section word length must be in the range [2, 128].

Dependencies

This parameter appears when you set Coefficient source to

Dialog parameters and Data type specification

mode to either Specify word lengths or

Binary point scaling.

Fraction lengths of filter sections, specified as an integer.

Dependencies

This parameter appears when you set Coefficient source to

Dialog parameters and Data type specification

mode to Binary point scaling.

Word length of the filter output, specified as an integer in the range [2, 128].

Dependencies

This parameter appears when you set Coefficient source to

Dialog parameters and Data type specification

mode to any option other than Full

precision.

Fraction length of the filter output, specified as an integer.

Dependencies

This parameter appears when you set Coefficient source to

Dialog parameters and Data type specification

mode to Binary point scaling.

Specify the rate processing rule for the block:

Enforce single-rate processing— The block performs frame-based processing and produces an output that has the same sample rate as the input. To decimate the signal while maintaining the input sample rate, the block decreases the output frame size. In this mode, the input column size must be a multiple of Decimation Factor (R).Allow multirate processing— In this mode, the block produces an output with a sample rate that isRtimes slower than the input sample rate.

Specify the name of the multirate filter object that you want the block to

implement. You must specify the filter as a dsp.CICDecimator

System object.

You can define the System object in the block dialog or in a MATLAB® workspace variable.

For information on creating System objects, see Define Basic System Objects.

Dependencies

This parameter appears when you set Coefficient source to

Filter object.

This button opens the Filter Visualization Tool (FVTool) from the Signal Processing Toolbox™ product and displays the filter response of the filter defined in the block. For more information on FVTool, see the Signal Processing Toolbox documentation.

Note

If you specify a filter in the Filter object parameter, you must apply the filter by clicking the Apply button before using the View Filter Response button.

Block Characteristics

Data Types |

|

Direct Feedthrough |

|

Multidimensional Signals |

|

Variable-Size Signals |

|

Zero-Crossing Detection |

|

More About

CIC filters are an optimized class of linear phase FIR filters composed of a comb part and an integrator part.

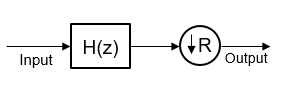

The CIC decimation filter is conceptually given by a single rate CIC filter, H(z) which is a lowpass anti-imaging filter, followed by a downsampler. The CIC decimation filter decreases the sample rate of an input signal by an integer factor using a cascaded integrator-comb (CIC) filter.

In a more efficient implementation, the single rate CIC filter H(z) is factorized this way:

where,

HI is the transfer function of the integrator part of the filter containing N stages of integrators.

HC is the transfer function of the N sections of the cascaded comb filters, each with a width of RM.

N is the number of sections. The number of sections in a CIC filter is defined as the number of sections in either the comb part or the integrator part of the filter. This value does not represent the total number of sections throughout the entire filter.

R is the decimation factor.

M is the differential delay.

In the overall multirate realization, the algorithm applies the noble identity for decimation and moves the rate change factor, R, to follow after the N sections of the cascaded integrators. The transfer function of the resulting filter is given by the following equation:

For a block diagram that shows the multirate implementation, see Algorithms.

Algorithms

The CIC decimation filter in More About is realized as a cascade of N sections of the integrators followed by a rate change factor of R, followed by N sections of comb filters.

This diagram shows two sections of cascaded integrators and two sections of cascaded comb filters. The unit delay in the integrator portion of the CIC filter can be located in either the feedforward or the feedback path. These two configurations yield identical filter frequency response. However, the numerical outputs from these two configurations are different due to the latency. This block puts the unit delay in the feedforward path of the integrator because it is a preferred configuration for HDL implementation.

References

[1] Hogenauer, E.B. “An Economical Class of Digital Filters for Decimation and Interpolation.” IEEE Transactions on Acoustics, Speech and Signal Processing. Vol. 29, Number 2, 1981, pp. 155–162.

[2] Meyer-Baese, U. Digital Signal Processing with Field Programmable Gate Arrays. New York: Springer Verlag, 2001.

[3] Harris, Fredric J., Multirate Signal Processing for Communication Systems. Upper Saddle River, NJ: Prentice Hall PTR, 2004.

Extended Capabilities

Generated code relies on the memcpy or

memset function (string.h) under certain

conditions.

HDL Coder™ provides additional configuration options that affect HDL implementation and synthesized logic.

Note

For an HDL-optimized filter architecture with hardware-friendly control signals, use the CIC Decimator (DSP HDL Toolbox) block. The DSP HDL Toolbox™ block simulates the latency of the HDL algorithm in Simulink®.

The block has HDLDataPath as a default architecture. This

architecture provides additional configuration options that affect HDL implementation and

synthesized logic.

| HDL Block Properties | Description |

|---|---|

| InputPipeline | Number of input pipeline stages to insert in the generated code.

Distributed pipelining and constrained output pipelining can move these

registers. The default is |

| OutputPipeline | Number of output pipeline stages to insert in the generated code.

Distributed pipelining and constrained output pipelining can move these

registers. The default is |

| ConstrainedOutputPipeline | Number of registers to place at the outputs by moving existing delays

within your design. Distributed pipelining does not redistribute these

registers. The default is |

| AddPipelineRegisters | Insert a pipeline register between stages of computation in a filter. See also AddPipelineRegisters (HDL Coder). |

The block supports these data types for HDL code generation:

| Input Port | Dimension | Fixed-Point | Floating-Point | Built-in Integers | Bus | Boolean | Enumerated | Complex Signal |

|---|---|---|---|---|---|---|---|---|

| Port_1 | Scalar | Yes | Half Single Double | Yes | No | Yes | Yes | Yes |

These block parameter configurations are incompatible with HDL code generation.

| Block Parameter | Limitations |

|---|---|

| Rate options | Parameter value Enforce single-rate processing

is not supported. |

The block participates in these HDL optimizations to optimize the speed, and area.

Area Optimization

| Optimization | Description |

|---|---|

| Resource Sharing (HDL Coder) | Resource sharing is an area optimization in which HDL Coder identifies multiple functionally equivalent resources and replaces them with a single resource. |

| Streaming (HDL Coder) | Streaming is an area optimization in which HDL Coder transforms a vector data path to a scalar data path (or to several smaller-sized vector data paths). |

Speed Optimization

| Optimization | Description |

|---|---|

| Specify Distributed Pipelining Settings (HDL Coder) | Distributed pipelining, or register retiming, is a speed optimization that moves existing delays in a design to reduce the critical path while preserving functional behavior. |

| Clock-Rate Pipelining (HDL Coder) | Clock-rate pipelining is an optimization framework in HDL Coder that allows other speed and area optimizations to introduce latency at the clock rate. |

| Specify Adaptive Pipelining Settings (HDL Coder) | Adaptive pipelining optimization creates patterns or combination of blocks with registers that can improve the achievable clock frequency and reduce the area usage on the FPGA boards by inserting pipeline registers to the blocks in your design. |

| Critical Path Estimation (HDL Coder) | To quickly identify the most likely critical path in your design, use Critical Path Estimation. Critical path estimation speeds up the iterative process of finding the critical path. To know blocks that are characterized in critical path estimation, see Characterized Blocks (HDL Coder). |

Vector and frame inputs are not supported for HDL code generation.

When you use AddPipelineRegisters, registers are placed based on the filter structure. The pipeline register placement determines the latency.

| Pipeline Register Placement | Latency (clock cycles) |

|---|---|

| A pipeline register is added between the comb stages of the differentiators. | NS-1, where NS is number of sections

(at the output side). |

Version History

Introduced before R2006a

See Also

Functions

Objects

dsp.CICDecimator|dsp.CICInterpolator|dsp.FIRDecimator|dsp.FIRInterpolator|dsp.CICCompensationDecimator|dsp.CICCompensationInterpolator|dsp.FIRHalfbandDecimator|dsp.FIRHalfbandInterpolator

Blocks

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

选择网站

选择网站以获取翻译的可用内容,以及查看当地活动和优惠。根据您的位置,我们建议您选择:。

您也可以从以下列表中选择网站:

如何获得最佳网站性能

选择中国网站(中文或英文)以获得最佳网站性能。其他 MathWorks 国家/地区网站并未针对您所在位置的访问进行优化。

美洲

- América Latina (Español)

- Canada (English)

- United States (English)

欧洲

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)