Getting Started with Embedded Coder Support Package for Qualcomm Hexagon Processors

This example shows how to generate, verify, and profile the optimized code using Embedded Coder® Support Package for Qualcomm® Hexagon® Processors.

In this example, you can run the generated code using Qualcomm Hexagon QHL CRL and Qualcomm Hexagon HVX CRL for an interpolated finite impulse response (IFIR) filter on the Qualcomm Hexagon DSP (Qualcomm Hexagon Simulator).

Introduction

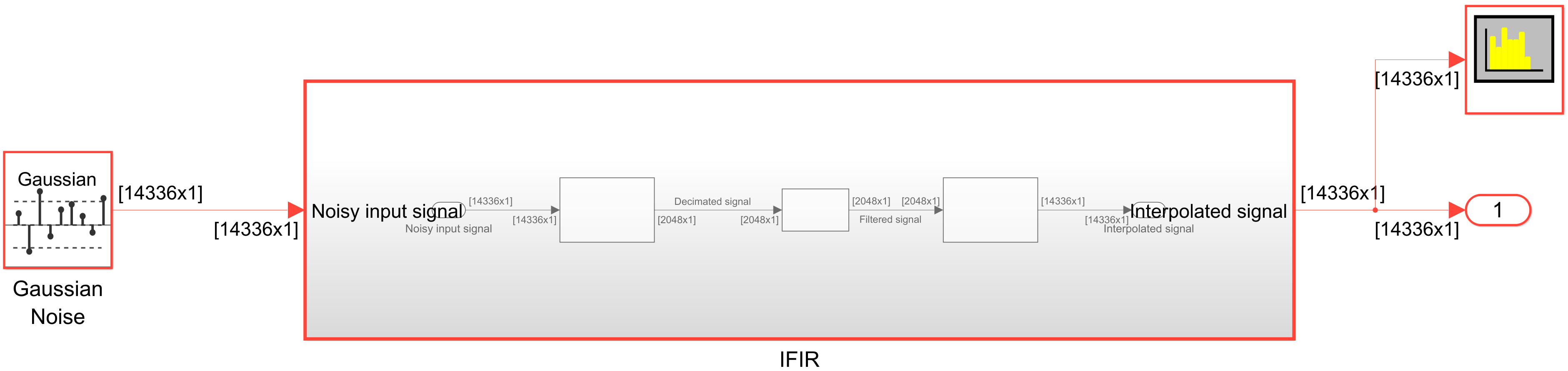

The interpolated finite impulse response (IFIR) filter offers an efficient way to create high-order FIR filters by utilizing multirate signal processing techniques to reduce computational complexity. The model includes a Gaussian noise source block, a FIR Decimation (DSP System Toolbox) block, a Discrete FIR Filter block, and an FIR Interpolation (DSP System Toolbox) block.

The FIR Decimation block downsamples the input signal, effectively reducing the sample rate. The lower order Discrete FIR Filter block then filters the input signal at this reduced sample rate, which minimizes computational complexity. Following the filtering stage, the FIR Interpolation block restores the signal to its original sample rate. This process significantly reduces the number of multiplications required during convolution, thereby substantially decreasing the overall computational burden.

Required Hardware

Qualcomm Hexagon Simulator

Simulate Interpolated FIR Filter

The filter coefficients for the FIR Decimation, Discrete FIR Filter, and FIR Interpolation blocks are derived using the ifir (DSP System Toolbox) function. This function designs a periodic filter h(z), which provides the coefficients for the Discrete FIR Filter block. Additionally, it designs an image-suppressor filter g(z), providing the coefficients for both the FIR Decimation and FIR Interpolation blocks as shown in this model.

The cascade of these filters represents the optimal min-max FIR approximation of the desired response.

Design Filters for Low Pass Filter Response

Set the passband ripple (or deviation) to 0.005 dB, stopband attenuation (or deviation) to 80 dB, interpolation factor to 7, passband edge frequency to 0.1 π rad/sample, and stopband edge frequency to 0.101 π rad/sample.

Apass = 0.005; % dB Astop = 80; % dB Fstop = .101; M = 7; F = [.1 Fstop];

Execute these commands to convert the passband ripple and stopband attenuation from dB to the linear scale, and to design the h(z) and g(z) filters, thereby deriving the filter coefficients.

A= [convertmagunits(Apass,'db','linear','pass') convertmagunits(Astop,'db','linear','stop')]; [h,g] = ifir(M,'low',F,A);

Ensure that the commands to compute h(z) and g(z) are set in the PreLoadFcn of the model. To open and configure PreLoadFcn, follow the below steps:

In the Simulink Toolstrip, on the Modeling tab, click Design gallery and then click Property Inspector.

With no selection at the top level of the model, on the Properties tab click Callbacks section and then select

PreLoadFcn.

To open the model, execute this command:

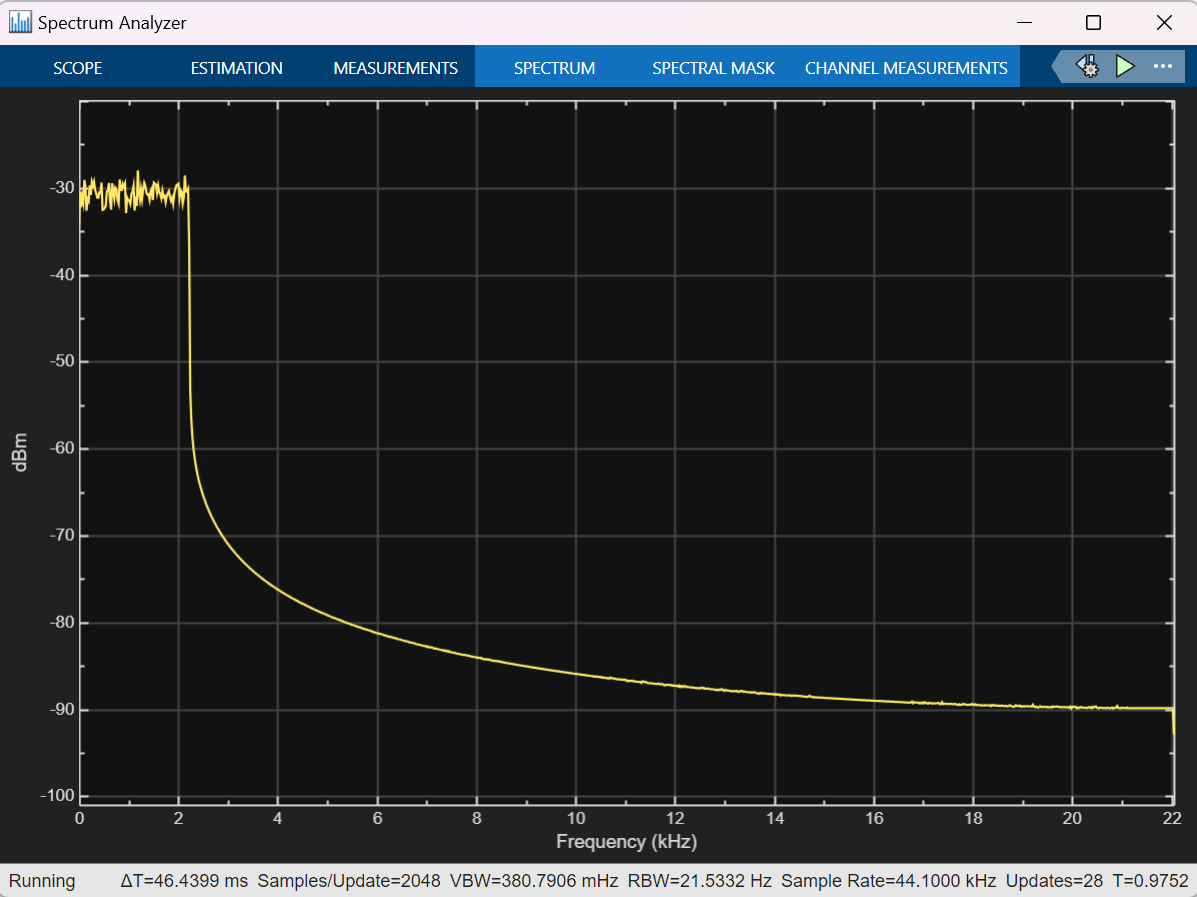

open_system('hexagon_ifir_filter');Observe the magnitude of the IFIR filter in the Spectrum Analyzer. For execution in host simulation, click on Run in the Simulation tab or run the following command. The default simulation time is set to 1 sec.

sim('hexagon_ifir_filter',SimulationMode="normal");

Configure Model

You can configure the model using either the Interactive Approach (Configuration Parameters in Simulink) or the Programmatic Approach (MATLAB programming interface).

Interactive Approach

Configure the model for code generation on Qualcomm Hexagon Simulator.

Press Ctrl+E to open Configuration Parameters the dialog box or on the model toolstrip click the Modeling tab and then click Model Settings.

Go to Hardware Implementation > Hardware board and select Qualcomm Hexagon Simulator.

In the Code Generation section, set these parameters:

System target file to ert.tlc

Build Configuration to Faster Runs

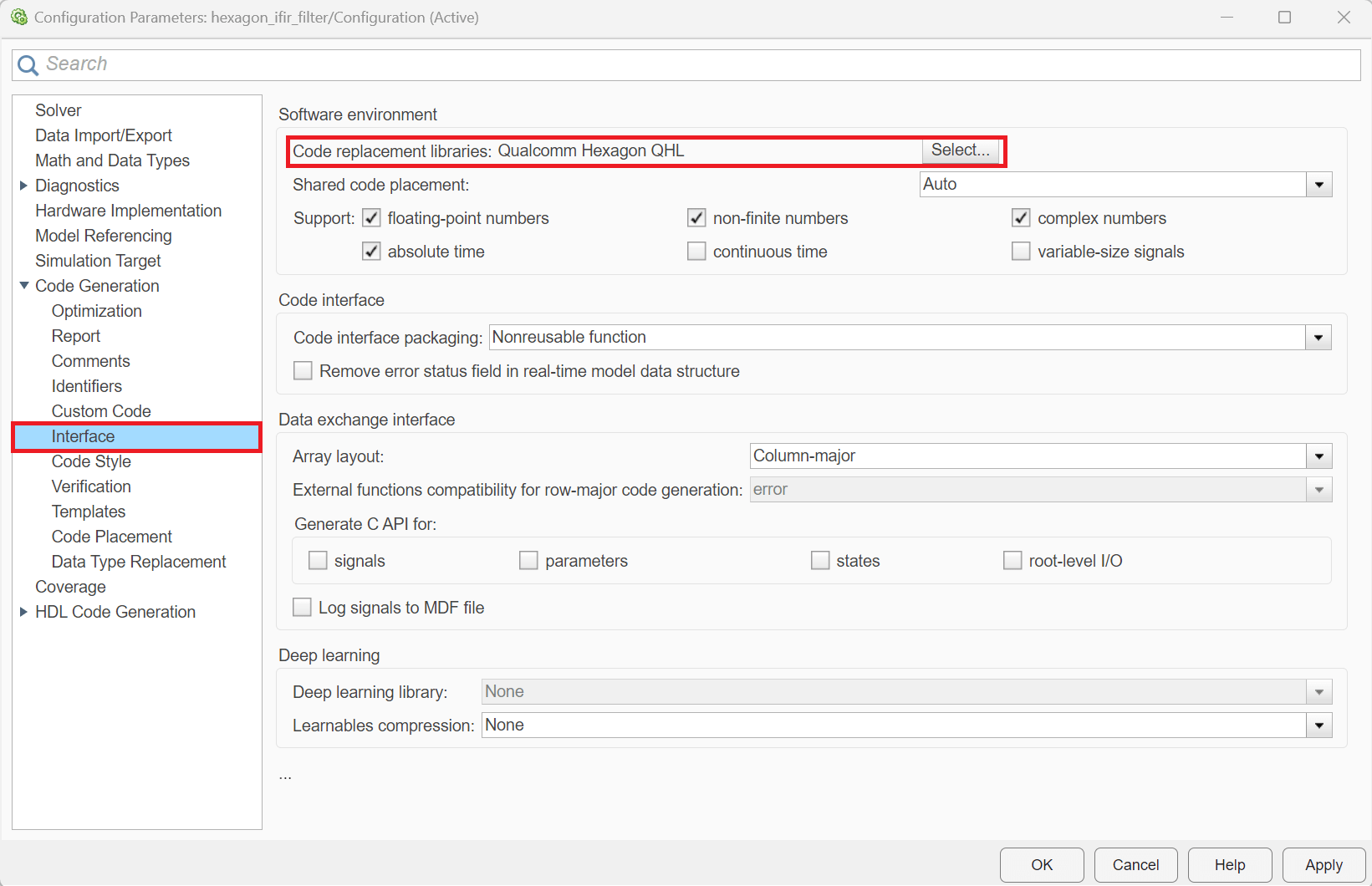

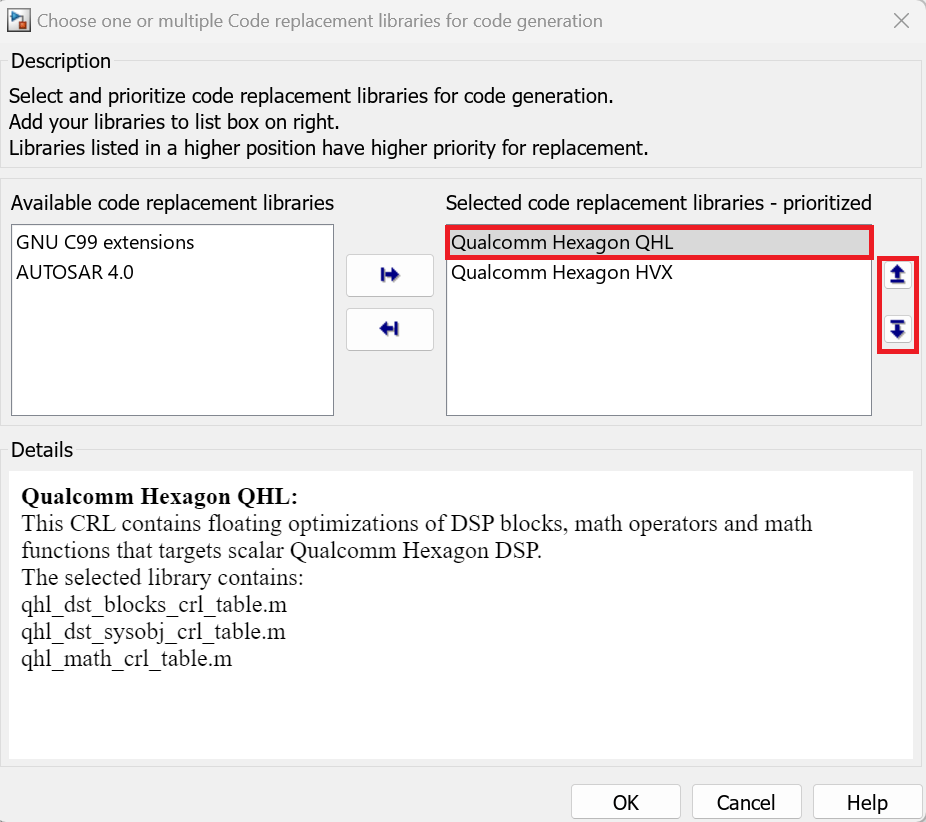

Under Code Generation > Interface > Code replacement libraries select Qualcomm Hexagon QHL or Qualcomm Hexagon HVX. Prioritize the selected Qualcomm Hexagon CRL (HVX/QHL) to ensure higher priority.

To select the Qualcomm Hexagon HVX library, make sure you select the Enable HVX option located in the Hardware Implementation section, under Hardware Board Settings > Target Hardware Resources. Additionally, the Processor Version must be V68 or higher, as HVX support is limited to these versions. For more information, see Qualcomm Hexagon Simulator Configurations.

Code Generation > Report > enable Create code generation report

Code Generation > Report > enable Open report automatically

Code Generation > Report > enable Summarize which blocks triggered code replacements

Programmatic Approach

To configure the Simulink model

hexagon_ifir_filter.slxfor deployment on Qualcomm Hexagon Simulator, execute these commands:

set_param('hexagon_ifir_filter','HardwareBoard','Qualcomm Hexagon Simulator'); set_param('hexagon_ifir_filter','SystemTargetFile','ert.tlc'); set_param('hexagon_ifir_filter','BuildConfiguration','Faster Runs');

These commands set the system target file to ert.tlc for optimizing the code for embedded real-time systems and configure the build configuration to prioritize execution speed by selecting Faster Runs.

Set the code replacement library to use either Qualcomm Hexagon QHL for scalar optimizations or Qualcomm Hexagon HVX for vectorized optimizations, in order to produce code that is optimized for Qualcomm Hexagon Simulator.

targetInfo = get_param('hexagon_ifir_filter',"CoderTargetData"); targetInfo.Device.EnableHVX = 1; targetInfo.Device.ProcessorVersion = 'V73'; set_param('hexagon_ifir_filter',"CoderTargetData",targetInfo); set_param('hexagon_ifir_filter','CodeReplacementLibrary','Qualcomm Hexagon HVX');

or

set_param('hexagon_ifir_filter','CodeReplacementLibrary','Qualcomm Hexagon QHL');

Finally, enable the generation of detailed code replacement reports. These reports provide valuable insights into the code structure and optimizations, facilitating a deeper understanding of the deployment process.

set_param('hexagon_ifir_filter','GenerateReport','on'); set_param('hexagon_ifir_filter','GenerateCodeReplacementReport','on');

Generate Code

You can now use the model to run the IFIR filter on the target.

Press Ctrl+B or go to Embedded Coder App and click Build.

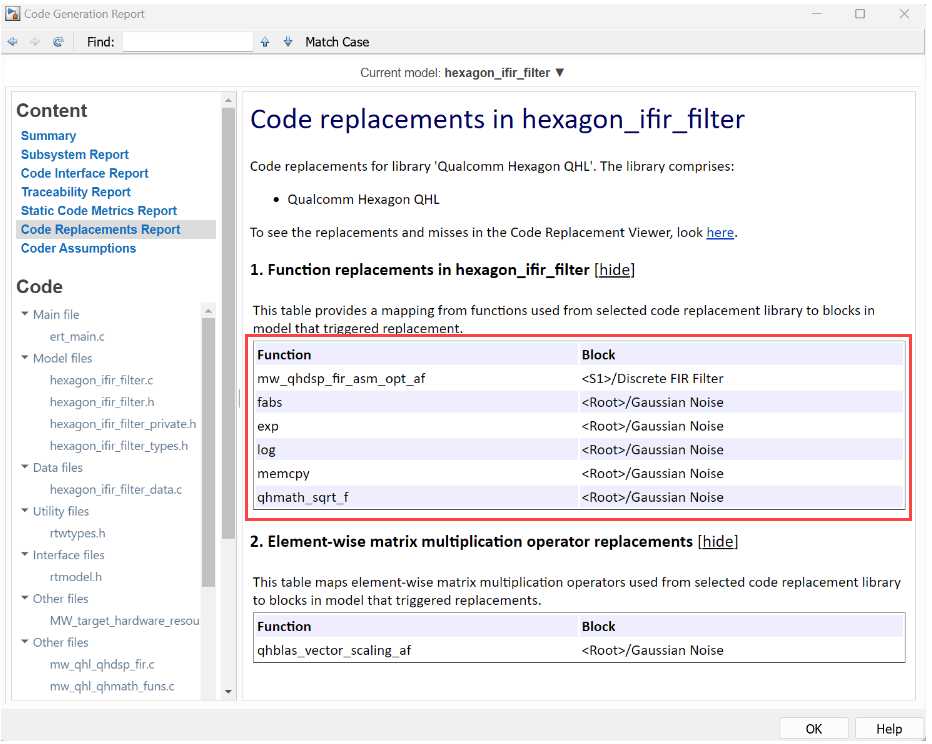

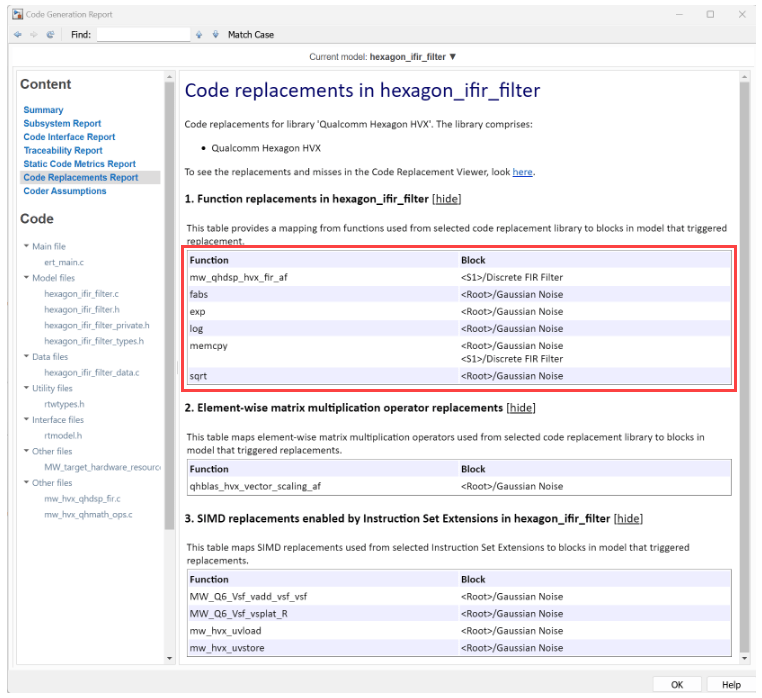

Once the code is generated you can view the generated code by clicking View Code for Qualcomm Hexagon QHL CRL.

You can also verify the code replacements using the Open Report > Code Replacement Report option.

This image shows the code and the corresponding replacements report for Qualcomm Hexagon HVX CRL.

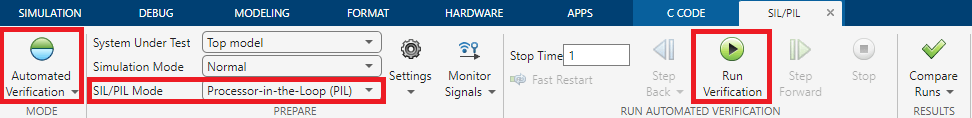

Verify on Target Using SIL/PIL Manager

To perform numerical accuracy verification of the generated code against the simulation output, use the SIL/PIL Manager App.

Go to SIL/PIL Manager.

Set Mode to Automated Verification.

Set the SIL/PIL Mode to Processor-in-loop (PIL).

Click Run Verification.

Or execute this command to run the model programmatically in PIL mode.

set_param('hexagon_ifir_filter','SimulationMode','processor-in-the-loop (pil)'); outputWithCRL = sim('hexagon_ifir_filter.slx');

### Searching for referenced models in model 'hexagon_ifir_filter'. ### Total of 1 models to build. ### Starting build procedure for: hexagon_ifir_filter ### Printing set environment variables: ### Successful completion of build procedure for: hexagon_ifir_filter Build Summary Top model targets: Model Build Reason Status Build Duration ================================================================================================== hexagon_ifir_filter Generated code was out of date. Code generated and compiled. 0h 0m 45.043s 1 of 1 models built (0 models already up to date) Build duration: 0h 0m 47.254s ### Connectivity configuration for component "hexagon_ifir_filter": Hexagon Simulator ### ### Preparing to start PIL simulation ... Building with 'Microsoft Visual C++ 2022 (C)'. MEX completed successfully. ### Updating code generation report with PIL files ... ### Starting application: 'hexagon_ifir_filter_ert_rtw\pil\hexagon_ifir_filter' ### Stopping application. Output logs Error logs

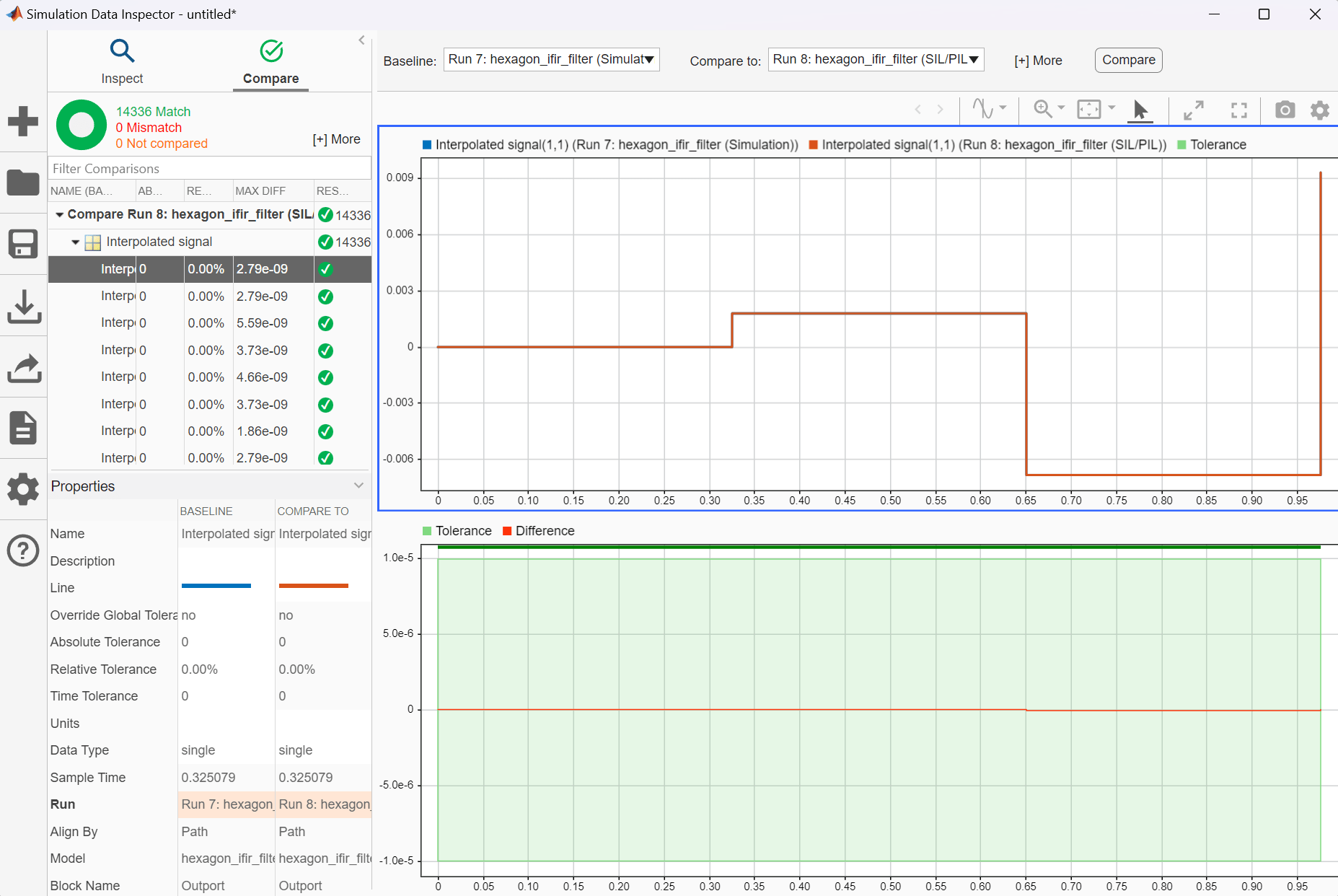

You can verify the numerical accuracy using the Simulation Data Inspector.

First convert the signals into frames in the Inspect tab of the inspector.

Then, verify the accuracy in the Compare tab.

Ensure to set the tolerance (Absolute or Relative) under the [+] More section in the Simulink Data Inspector window.

From the plot, observe that the simulation output overlaps with the PIL output (subplot-1), and the absolute sample tolerance is less than 1e-5 (subplot-2).

Or execute this function to run and configure the SDI programmatically.

simulinkSDI;

Compare Performance

Compare the performance of a particular block with plain C code (without CRL) and QHL/HVX code (with CRL).

Enabling code profiling

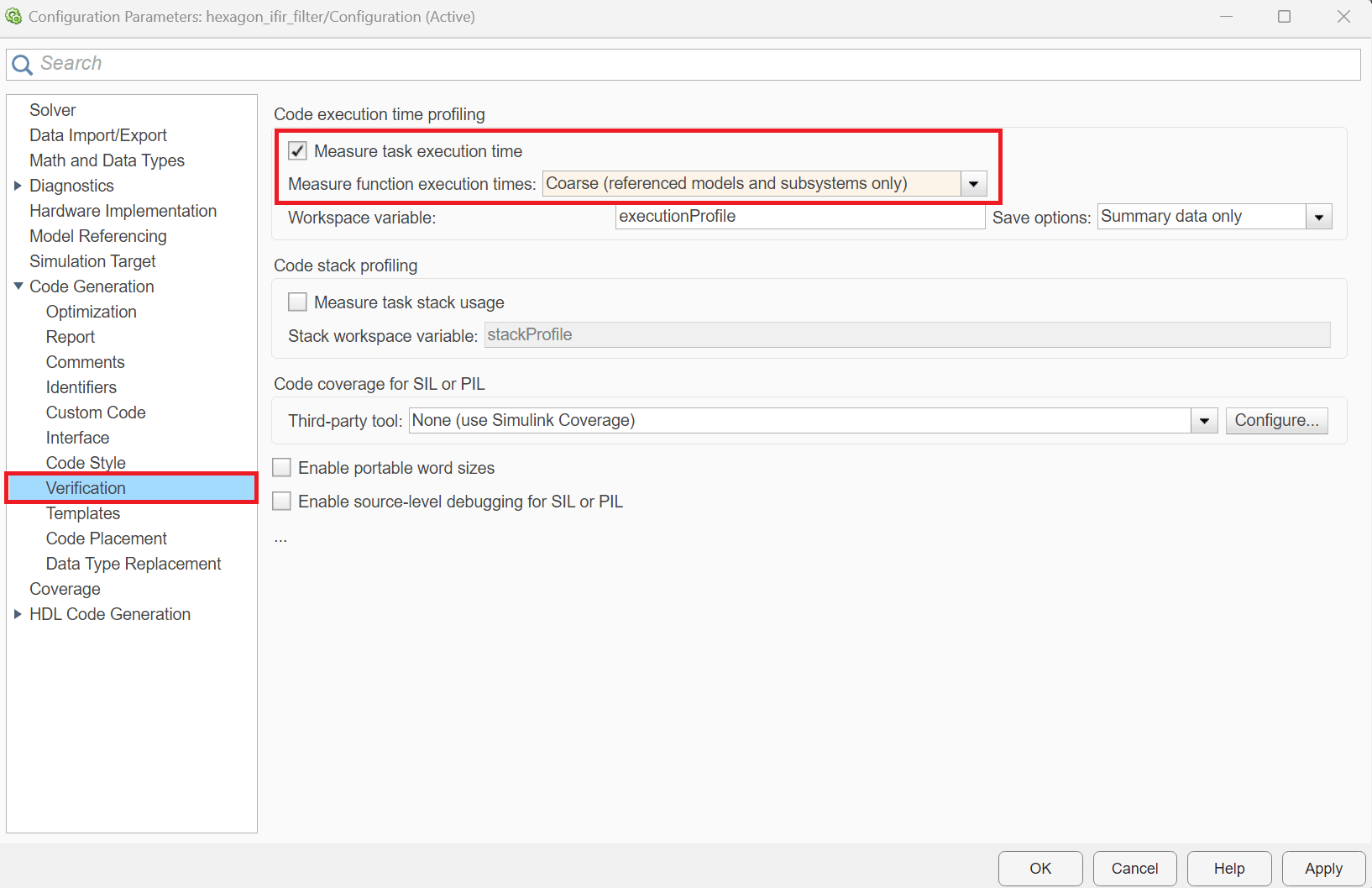

Go to Model Settings, check the Code Generation > Verification > Measure task execution time.

Set Code Generation > Verification > Measure function execution times to Coarse.

Redo the Run Verification step from SIL/PIL.

Analyze Profile Information

To analyze the profiling information, you can either use Code Execution Profiling Report or Code Profile Analyzer.

Code Execution Profiling Report

From SIL/PIL > RESULTS select Generate Report.

Under Profiled Sections of Code, you can find the execution time obtained for each of the model functions.

In this section, verify the block profiling. Click the MATLAB icon next to the IFIR to get the total execution time in ticks.

The image shows the code execution profiling report for Qualcomm Hexagon QHL CRL replacements.

ticksWithQHLCRL = outputWithCRL.get('executionProfile').Sections(4).TotalExecutionTimeInTicksticksWithQHLCRL = uint64

29266215

You can observe that the total execution time in ticks consumed by the step function with Qualcomm Hexagon QHL CRL is 29266215 cycles. Repeat the same steps without selecting a CRL in the Model Settings (Code Generation > Interface > Code replacement libraries).

set_param('hexagon_ifir_filter','CodeReplacementLibrary','None'); outputWithoutCRL = sim('hexagon_ifir_filter.slx');

### Searching for referenced models in model 'hexagon_ifir_filter'. ### Total of 1 models to build. ### Starting build procedure for: hexagon_ifir_filter ### Printing set environment variables: ### Successful completion of build procedure for: hexagon_ifir_filter Build Summary Top model targets: Model Build Reason Status Build Duration ================================================================================================== hexagon_ifir_filter Generated code was out of date. Code generated and compiled. 0h 0m 34.393s 1 of 1 models built (0 models already up to date) Build duration: 0h 0m 35.549s ### Connectivity configuration for component "hexagon_ifir_filter": Hexagon Simulator ### ### Preparing to start PIL simulation ... Building with 'Microsoft Visual C++ 2022 (C)'. MEX completed successfully. ### Updating code generation report with PIL files ... ### Starting application: 'hexagon_ifir_filter_ert_rtw\pil\hexagon_ifir_filter' ### Stopping application. Output logs Error logs

ticksWithoutCRL = outputWithoutCRL.get('executionProfile').Sections(4).TotalExecutionTimeInTicksticksWithoutCRL = uint64

45477747

The total cycles consumed by the step function without selecting a CRL is around 45477747 cycles.

Similarly, the total execution time in ticks consumed by the step function with Qualcomm Hexagon HVX CRL is 15261975 cycles**.** This figure shows the performance comparison between the Qualcomm Hexagon QHL CRL, Qualcomm Hexagon HVX CRL, and Plain-C.

Code Profile Analyzer

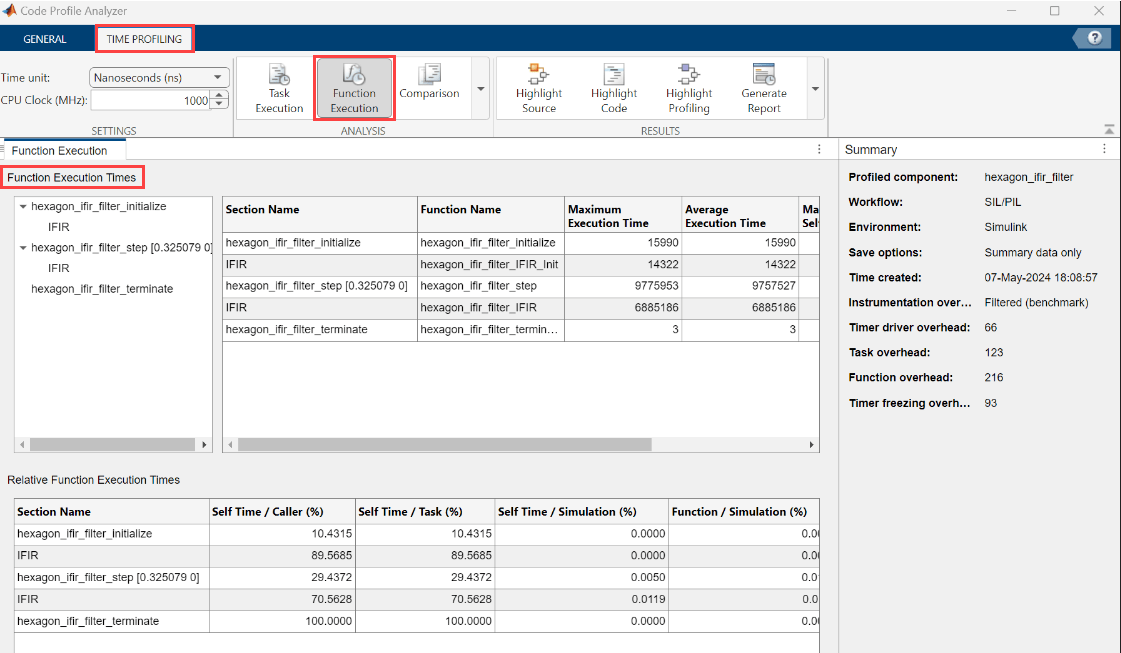

Under the Analysis section, click Function Execution.

In the Function Execution Times pane, verify the Maximum and Average Execution time for the Discrete FIR Filter block and Math Operations. You can consider the average execution time for the whole simulation.

Optionally, you can also verify the relative times among the self-time/caller or self-time/task.

This image shows the code profile analyzer report for Qualcomm Hexagon QHL CRL replacements.