AXI4-Stream IIO Write

Write AXI4-Stream Data using IIO

Add-On Required: This feature requires the Embedded Coder Support Package for AMD SoC Devices add-on.

Libraries:

Embedded Coder Support Package for AMD SoC Devices

Description

Add-On Required: This feature requires the Embedded Coder Support Package for AMD SoC Devices add-on.

This block writes data to the direct-memory-access (DMA) buffer of the specified AXI4-Stream IP core device by using the Industrial I/O (IIO) library drivers. The AXI4-Stream IIO Write block enables low-latency, high-throughput data transmission from your model on the processor to the IP core on the FPGA.

Examples

Ports

Input

Output

Parameters

Tips

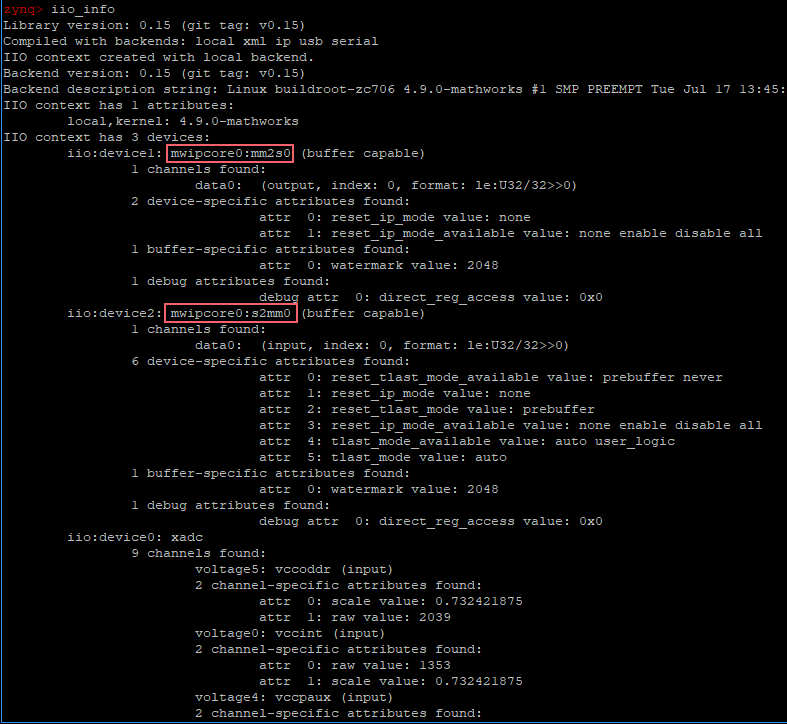

To get a list of available IIO device names and channels, open a terminal into the AMD® SoC device hardware board, and execute this command.

iio_info

Version History

Introduced in R2018b