参考设计集成和部署

将生成的 IP 核集成到默认系统参考设计中

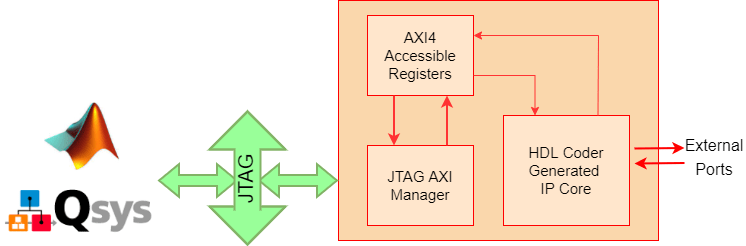

您可以将生成的 IP 核集成到默认系统参考设计中,或集成到为板注册的自定义参考设计中。HDL Coder™ 可以生成 IP 核,将其集成到 Qsys 工程中,并对硬件进行编程。使用 Embedded Coder®,您可以生成和编译嵌入式软件,并在 ARM® 处理器上运行它。

主题

- Default System Reference Design for Intel FPGA Boards

Learn about the default system reference design and using the reference design for Intel® FPGA boards.

- Default System Reference Design for Intel SoC Devices

Learn about the default system reference design and using the reference design for Intel SoC Devices.

- Default System with External DDR4 Memory Access Reference Design

Learn about the default system with external DDR3 memory access reference design and its requirements.

- Program Target FPGA Boards or SoC Devices

How to program the target Intel or Xilinx Hardware.