Intel FPGA 和 SoC 器件

HDL Coder™ 可以生成 IP 核,将其集成到 Qsys 工程中,并对 Intel 硬件进行编程。使用 Embedded Coder®,您可以生成和编译嵌入式软件,并在 ARM® 处理器上运行它。请参阅Hardware-Software Co-Design Workflow for SoC Platforms。

要将设计部署到 Intel FPGA 和 SoC 器件,您必须安装 HDL Coder Support Package for Intel FPGA and SoC Devices。有关安装信息,请参阅HDL Coder 支持的硬件。

HDL Coder Support Package for Intel FPGA and SoC Devices 支持生成可集成到使用 Intel Qsys 的 FPGA 设计中的 IP 核。与 Embedded Coder Support Package for Intel SoC Devices 结合使用时,此解决方案可以使用 C 和 HDL 代码生成对 Intel SoC 进行编程。软硬件协同设计工作流涵盖仿真、原型构建、验证和实现。

| 器件系列 | 板 | 可用参考设计 |

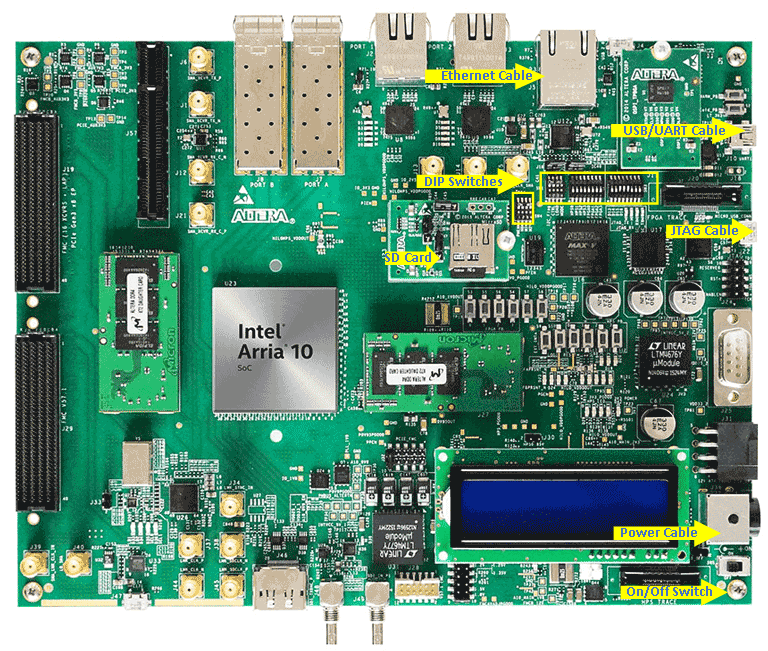

Arria® 10 SoC | Intel Arria 10 SoC 开发工具包 | |

Cyclone® V | Cyclone V SoC 开发工具包 - 修订版 C | |

Cyclone V SoC 开发工具包 - 修订版 D | ||

Arrow SoCKit 开发板 | ||

Arria 10 | Arria 10 GX FPGA 开发工具包 | 支持外部 DDR4 内存访问的 PCIe AXI Manager(需要 HDL Verifier) 支持外部 DDR4 内存访问的 JTAG AXI Manager(需要 HDL Verifier) |

Intel MAX® 10 | Arrow® DECA MAX 10 FPGA 评估工具包 | AXI Manager - 以太网(需要 HDL Verifier) (HDL Verifier) |

注意

要扩展对新硬件的支持,请参阅在自定义硬件上部署 IP 核。

类别

- 设置和配置

下载并安装支持包以与第三方 EDA 工具和受支持的硬件结合使用

- 软硬件协同设计快速入门

在目标硬件平台上部署生成的 HDL 代码

- 生成 IP 核和比特流

生成包含 HDL 代码的 HDL IP 核和比特流,用于部署在独立的 Intel FPGA 板和 SoC 器件上