AMD FPGA 和 SoC 器件

HDL Coder™ 可以生成 IP 核,将其集成到 Vivado® 工程中,并对 AMD 硬件进行编程。要将设计部署到 AMD 硬件,您必须安装 HDL Coder Support Package for AMD FPGA and SoC Devices。有关安装信息,请参阅HDL Coder 支持的硬件。

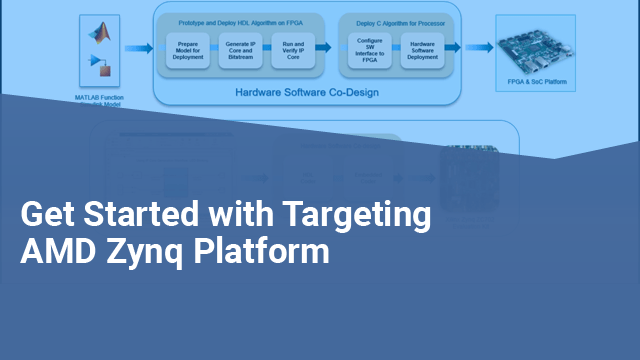

HDL Coder Support Package for AMD FPGA and SoC Devices 支持生成可集成到使用 Xilinx® Vivado 的 FPGA 设计中的 IP 核。与 Embedded Coder® 结合使用时,此解决方案可以使用 C 和 HDL 代码生成对 AMD Zynq® SoC 进行编程。软硬件协同设计工作流涵盖仿真、原型构建、验证和实现。使用 Embedded Coder,您可以生成和编译嵌入式软件,并在 ARM® 处理器上运行它。请参阅Hardware-Software Co-Design Workflow for SoC Platforms。

| 器件系列 | 板 | 可用参考设计 |

Versal® | Xilinx Versal AI Core Series VCK190 评估工具包 | |

Zynq UltraScale+™ RFSoC | Xilinx Zynq UltraScale+ RFSoC ZCU111 评估工具包 | |

Xilinx Zynq UltraScale+ RFSoC ZCU216 评估工具包 | ||

Zynq UltraScale+ MPSoC | Xilinx Zynq UltraScale+ MPSoC ZCU102 评估工具包 | |

Zynq | Xilinx Zynq ZC706 评估工具包 | |

Xilinx Zynq ZC702 评估工具包 | ||

ZedBoard™ | ||

Kintex®-7 | Xilinx Kintex-7 KC705 开发板 | |

Virtex®-7 | Xilinx Virtex-7 VC707 开发板 | |

Artix®-7 | Xilinx Artix-7 35T Arty 开发板 |

注意

要扩展对新硬件的支持,请参阅在自定义硬件上部署 IP 核。

有关工具和板支持的详细信息,请参阅Supported EDA Tools and Hardware。

类别

- 设置和配置

下载并安装支持包以与第三方 EDA 工具和受支持的硬件结合使用

- 软硬件协同设计快速入门

在目标硬件平台上部署生成的 HDL 代码

- 生成 IP 核和比特流

生成包含 HDL 代码的 HDL IP 核和比特流,用于部署在独立的 AMD FPGA 板和 SoC 器件上

- 目标 AMD RFSoC 硬件

在 AMD RFSoC 目标硬件上运行 MATLAB® 或 Simulink® 算法