Default Video System Reference Design

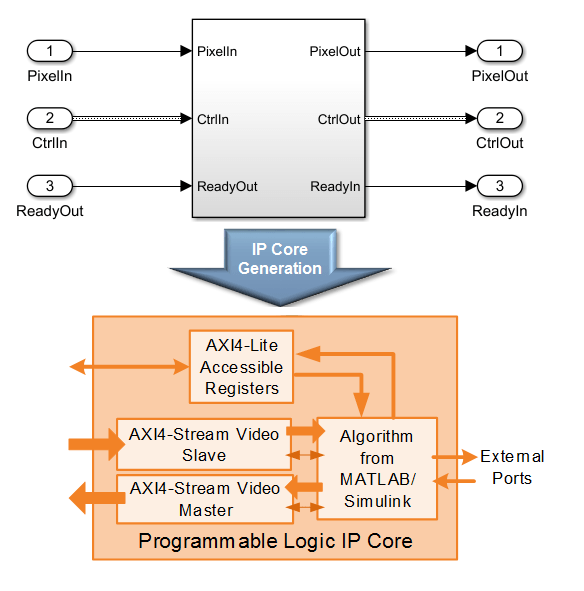

With the HDL Coder™ software, you can generate an HDL IP core with AXI4-Stream Video

interfaces. You can integrate the HDL IP core into the Default video

system reference design platform. The reference design supports

high-speed image processing and video streaming applications.

The reference design contains the IP blocks to handle HDMI input and output video interfaces. HDL Coder generates the HDL DUT IP core with an AXI4-Stream Video interface, and inserts it into the reference design. The AXI4-Stream Video interface processes the video stream from the HDMI Input IP, and sends the output video stream to the HDMI Output IP. The input stream to the HDL IP core is in RGB format. The reference design contains IP blocks that convert the video stream data between the YCbCr and RGB formats.

For parameter tuning, the IP core can have an AXI4-Lite interface that connects to the ARM processor.

Requirements

FMC-HDMI-CAM or FMC-IMAGEON FMC HDMI I/O card

Specifications

Input video source and output video display resolution: 1080p

Video stream Pixel Data signal format: RGB

Video stream Pixel Data signal encoding: Encodes RGB format into 32-bit representation 32’hFFRRGGBB

DUT interface: Only one AXI4-Stream Video Slave and one AXI4-Stream Video Master interface

Targeting the Reference Design

To target your video algorithm in Simulink® to the Default video system reference design:

Model your video algorithm with the streaming pixel protocol. To generate an IP core with AXI4-Stream Video interfaces, in your DUT interface, implement the Pixel Data and Pixel Control Bus signals. You can optionally model the backpressure signal, Ready, and map it to the AXI4-Stream Video interface.

For more information, see Model Design for AXI4-Stream Video Interface Generation.

Specify

IP Core Generationas target workflow. Open the HDL Workflow Advisor. In the Set Target Device and Synthesis Tool task, specifyIP Core Generationas the Target workflow. For Target platform, choose from one of the boards listed in Board Support.Specify

Default video systemas target reference design. In the Set Target Reference Design task, for Reference design, specifyDefault video system (requires HDMI FMC Module).You can also specify whether the code generator inserts the AXI manager IP for the JTAG or programmable logic (PL) Ethernet connection and the data capture IP for the JTAG, PL Ethernet, processing system (PS) Ethernet, or universal serial bus (USB) Ethernet connection into the reference design.

For more information about the available connections for AXI manager and FPGA data capture, see Set Target Reference Design.

For an example of automatic insertion of the AXI manager IP for the JTAG connection into a reference design, see Debug and Control Generated HDL IP Core by Using JTAG AXI Manager.

Go through the workflow to generate the HDL IP core, and integrate the IP core

into the Default video system reference design.

For an example that shows how to generate an HDL IP core with AXI4-Stream Video interface, see Generate IP Core with AXI4-Stream Video Interface.

Board Support

You can use the Default video system reference design

architecture with these target platforms:

Xilinx® Zynq® ZC702 evaluation kit

Xilinx Zynq ZC706 evaluation kit

ZedBoard™