Simscape 硬件在环工作流

从 Simscape 模型生成 HDL 代码并部署到目标硬件上

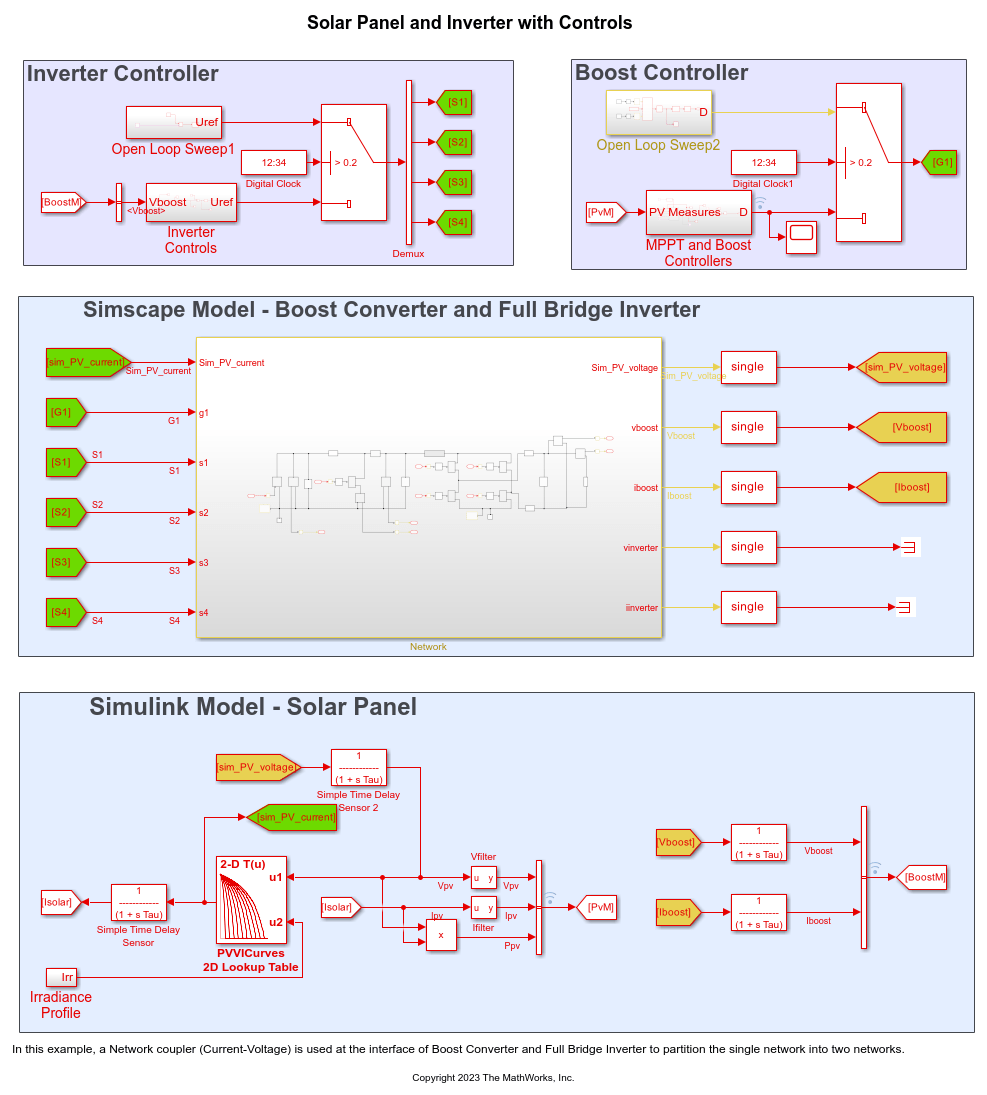

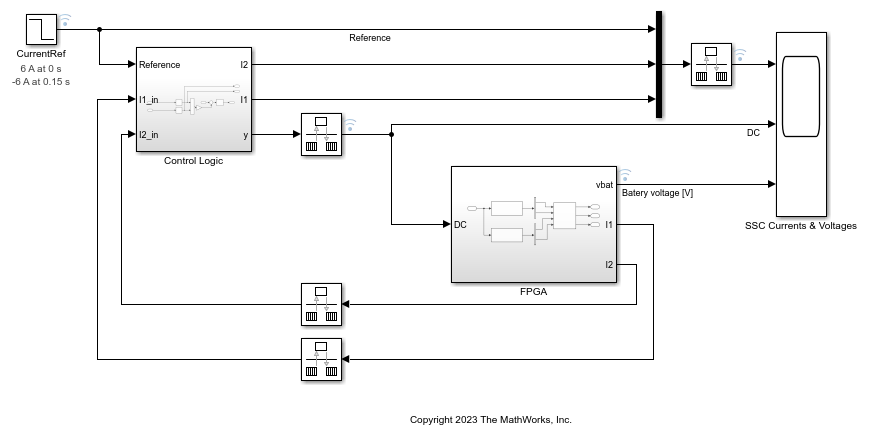

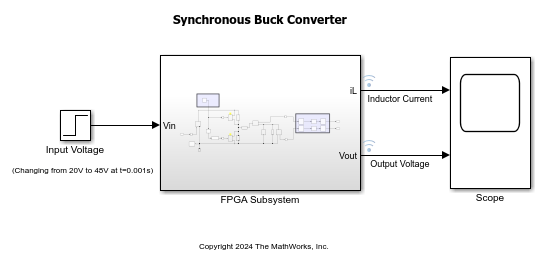

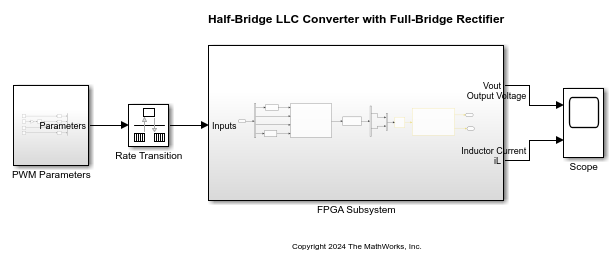

Simscape™ 硬件在环 (HIL) 工作流使您能够为 Simscape 被控对象模型生成 HDL 代码,并将生成的代码部署到通用现场可编程门阵列 (FPGA)、片上系统 (SoC) 或 Speedgoat® FPGA I/O 模块上。通过将被控对象模型部署到 FPGA 板,您可以加速模型的仿真,并使用 HIL 仿真实时对模型进行仿真。

Simscape HDL 工作流顾问将 Simscape 被控对象模型转换为 HDL 兼容的实现模型,您可以从中生成 HDL 代码。您可以使用 sschdladvisor 函数打开顾问并在其中运行任务来生成 HDL 实现模型。在生成 HDL 实现模型时,您可以为其指定数据类型精度(浮点,如 single 或 double,或定点)。您还可以指定在实现模型中插入验证逻辑,并验证 HDL 实现是否在数值上与原始 Simscape 算法匹配。

在生成 HDL 实现模型后,您可以使用 HDL Coder™ 为此模型生成代码,并使用 HDL 工作流顾问将生成的代码部署到目标平台上。