Simplify Constant Operations and Reduce Design Complexity in HDL Coder

HDL Coder™ performs certain optimization techniques that improve the quality of the generated HDL code. When you use floating-point data types in Native Floating Point mode and generate code from your model, at compile-time, HDL Coder searches for a subset of blocks that fit a certain pattern. When the code generator recognizes the pattern, it automatically performs certain optimization techniques to replace the blocks in the subset with other, simpler blocks.

The optimization techniques:

Remove redundant run-time computations

Simplify your design

Improve quality and efficiency of generated HDL code

Reduce latency and area footprint

Improve timing of your design on target hardware

Simplification of Constant Operations

HDL Coder removes redundant operations in your design by evaluating constant subexpressions in advance. This optimization technique identifies Simulink® blocks in your model that have constant values at all input ports, and then replaces the blocks with Constant blocks. The code generator propagates the input constants inside the blocks to compute the resulting Constant value. For example, c = 3 * 5 becomes c = 15.

This optimization works with any Simulink block that supports HDL code generation. For example:

Open the model

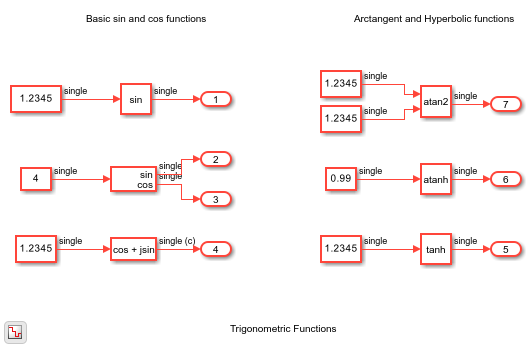

hdlcoder_constant_simplification. Double-click theTrigonometric FunctionsSubsystem.

open_system('hdlcoder_constant_simplification') open_system('hdlcoder_constant_simplification/Trigonometric Functions') set_param('hdlcoder_constant_simplification', 'SimulationCommand', 'update');

To generate HDL code for the

hdlcoder_constant_simplificationmodel, enter this command.

makehdl('hdlcoder_constant_simplification')

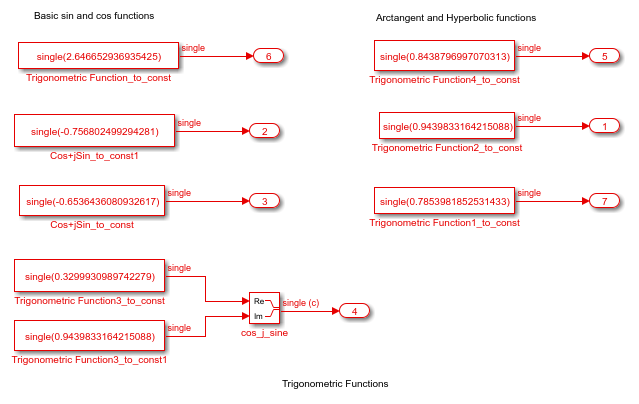

Open the generated model, and double-click the

Trigonometric Functionssubsystem.

HDL Coder recognized the modeling pattern and replaced the constant single-precision trigonometric operations with constants. This optimization results in significant area reduction and improvements to timing when you deploy the code onto the target platform.

Replacement of Slower Operations with Faster Equivalents

This optimization automatically replaces slower operations with faster equivalents. For example, r1 = r2 / 2 becomes r1 = r2 >> 1.

Examples of this optimization technique include replacement of a Product block or a Divide block by a Gain block. If one of the inputs to a Product block or a Divide block is a constant and a power of two, the code generator replaces that block by a Gain block. The code generator propagates the Constant value inside the Product block or the Divide block to compute the Gain parameter. This optimization works with single data types in the Native Floating Point mode.

For example:

Open the model

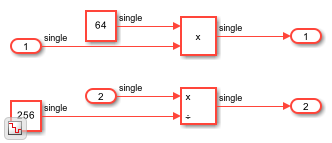

hdlcoder_slow_operation_replacement. Double-click the DUT Subsystem.

open_system('hdlcoder_slow_operation_replacement') open_system('hdlcoder_slow_operation_replacement/DUT') set_param('hdlcoder_slow_operation_replacement', 'SimulationCommand', 'update');

To generate HDL code for the DUT Subsystem, enter this command:

makehdl('hdlcoder_slow_operation_replacement/DUT')

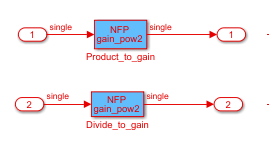

Open the generated model, and double-click the

DUTsubsystem.

HDL Coder recognized the modeling pattern and replaced the Product block and the Divide block by a Gain block. This optimization significantly reduces the latency of your design, and improves area and timing on the target FPGA.

Combination of Multiple Operations

This optimization replaces several operations with one equivalent operation. Examples of this optimization technique include replacement of a Sin block and a Cos block by a Sincos block. If you provide the same input signal to a Sin block and a Cos block in your model, and when the HDL Block Properties of the Sin and Cos blocks match, the code generator replaces the blocks with a Sincos block. This optimization works with single data types in the Native Floating Point mode.

For example:

Open the model

hdlcoder_combine_operations. Double-click the DUT Subsystem.

open_system('hdlcoder_combine_operations') open_system('hdlcoder_combine_operations/DUT') set_param('hdlcoder_combine_operations', 'SimulationCommand', 'update');

To generate HDL code for the DUT Subsystem, enter this command:

makehdl('hdlcoder_combine_operations/DUT')

Open the generated model, and double-click the DUT Subsystem. The generated model appears as below.

HDL Coder recognized the modeling pattern and replaced the Sin block and the Cos block by a Sincos block. This optimization technique significantly improves the performance of your design on the target platform.

Considerations

The optimizations work with floating-point data types. Fixed-point designs are not affected by this optimization. When you use single data types, enable the

Native Floating Pointmode. In the Configuration Parameters dialog box, in the HDL Code Generation > Floating Point pane, select Use Floating Point. To learn about native floating-point support in HDL Coder, see Generate Target-Independent HDL Code with Native Floating-Point.The optimizations preserve all comments from the blocks in the generated code. To learn about specifying comments to blocks, see Generate HDL Code with Annotations or Comments.

The optimizations do not optimize blocks that use tunable parameters or generic inputs because the tunable parameters are not treated as constant values. To make these blocks participate in the optimization, in the Mask Editor for the blocks, clear the Tunable check box. To learn about tunable parameters, see Generate DUT Ports for Tunable Parameters.

The optimizations treat enumeration values and constants from the Workspace browser as constant values. The code generator therefore propagates these values inside various components and simplifies the constant operations.