Integrate Custom HDL Code by Using DocBlock

You can use one or more DocBlock blocks to integrate custom HDL code into your design.

When to Use DocBlock for Integrating Custom Code

If you want to keep the HDL code in your model, instead of as a separate file, use a DocBlock to integrate custom HDL code. The text in the DocBlock is your custom VHDL®, Verilog® or SystemVerilog code.

You include each DocBlock that contains custom HDL code by placing it in a black box subsystem, and then including the black box subsystem in your design under test (DUT). One HDL file is generated for each black box subsystem.

Alternatives for Custom Code Integration

If you want to keep your custom HDL code separate from your model, such as when the custom code is intellectual property (IP) or a library from a third party vendor, use a black box subsystem or black box model reference.

Use DocBlock to Integrate Custom Code

In your DUT, at any level of hierarchy, add a Subsystem block.

For the Subsystem block, in the HDL Block Properties dialog box:

Set Architecture to

BlackBox.Customize the black box subsystem interface so that it matches your custom HDL code interface. See Customize Black Box or HDL Cosimulation Interface.

In the subsystem, add a DocBlock block.

For the DocBlock, in the HDL Block Properties dialog box:

Set Architecture to

HDLText.Set TargetLanguage to your target language, such as

Verilog,SystemVerilogorVHDL.

In the DocBlock, enter the HDL code for your custom Verilog or SystemVerilog

module, or VHDLentity.The language must match the DocBlock TargetLanguage setting.

Restrictions

The black box subsystem that contains the DocBlock cannot be the top-level DUT.

You can have a maximum of two DocBlock blocks in the black box subsystem. If you have two DocBlock blocks, one has TargetLanguage set to

VHDLand the other must have TargetLanguage set to eitherVerilogorSystemVerilog.When generating code, HDL Coder™ integrates the code from the DocBlock that matches the target language for code generation.

When a black box subsystem that contains the DocBlock is placed in another black box subsystem, HDL Coder does not integrate the HDL code from this DocBlock during code generation.

When a black box subsystem contains a DocBlock with custom

packagedeclarations, HDL Coder does not include those package data types in the generated interface code.

Include Custom HDL Code Using Doc Block

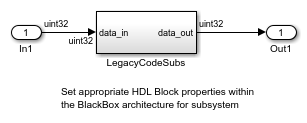

The hdlcoderIncludeCustomHdlUsingDocBlockExample model shows how to integrate custom VHDL and Verilog code into your design with the DocBlock block.

To open hdlcoderIncludeCustomHdlUsingDocBlockExample model, run these commands:

load_system('hdlcoderIncludeCustomHdlUsingDocBlockExample.slx'); open_system('hdlcoderIncludeCustomHdlUsingDocBlockExample/DUT');

The LegacyCodeSubs subsystem has two DocBlock blocks which contains legacy VHDL and Verilog code. You can generate the HDL code of the DUT subsystem by using makehdl command.