FIL Simulation

Simulate HDL code on FPGA hardware from Simulink

Libraries:

Generated

Description

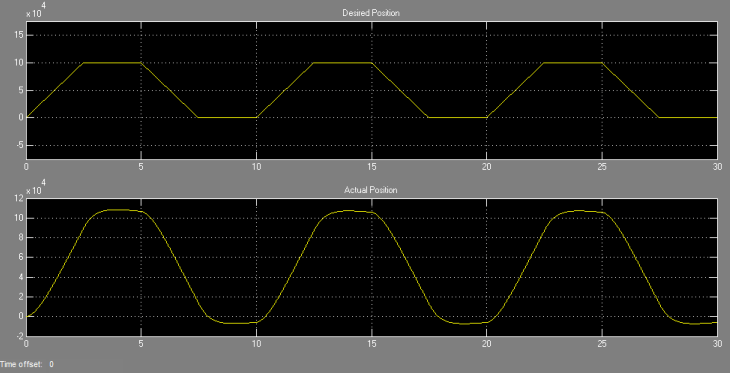

The generated FPGA-in-the-loop (FIL) simulation block is the communication interface between the FPGA and your Simulink® model. It integrates the hardware into the simulation loop and allows it to participate in simulation as any other block.

You can generate a FIL Simulation block from existing HDL code using the FPGA-in-the-Loop Wizard, or, generate HDL code and an accompanying FIL Simulation block using HDL Workflow Advisor. Generating HDL code requires an HDL Coder™ license.

For the generation and simulation workflow, see Block Generation with the FIL Wizard. If you encounter any issues during FIL simulation, refer to Troubleshooting FIL for help in diagnosing the problem.

You can use the FIL Simulation block in models running in Normal, Accelerator, or Rapid Accelerator simulation modes. The FIL Simulation parameters are not tunable in any of the simulation modes. For more information about these modes, see How Acceleration Modes Work (Simulink).

Examples

Ports

The ports of the block correspond to the interface of your HDL design running on your FPGA. You can configure the data types of the signals that the FIL Simulation block returns to Simulink.

Input

Output

Parameters

Version History

Introduced in R2012b