Generate SystemVerilog Class for DPI Component

A SystemVerilog class is a user-defined data type that includes data (properties) and functions/tasks (methods) that operate on the data. SystemVerilog classes are often used in verification environments such as UVM.

HDL Verifier™ uses SystemVerilog DPI to generate C code from MATLAB® or Simulink® and wraps the code within a SystemVerilog interface. Using a SystemVerilog class template, the C entry points are exposed as methods of a SystemVerilog class. This allows you to instantiate and use the generated class just like any native SystemVerilog class within your verification environment.

This example shows how to generate a SystemVerilog class for a DPI component from a Simulink® subsystem and verify the generated class using an HDL simulator.

This example uses the proportional-integral-derivative (PID) controller from the example Get Started with SystemVerilog DPI Component Generation.

Set Up Model

To open the design, run the following command:

open_system("svdpi_pid.slx");To set up the model to generate SystemVerilog class, open the HDL Verifier app from the Apps tab:

Select DPI Component Generation in the Mode section.

Select SystemVerilog Settings in the Prepare section.

Set Component template type to SystemVerilog Class and click OK.

Alternatively, run the following commands to set up the model:

set_param("svdpi_pid","SystemTargetFile","systemverilog_dpi_grt.tlc"); set_param("svdpi_pid","DPIComponentTemplateType","SystemVerilog Class");

Generate SystemVerilog Class

To generate the SystemVerilog class, select the Controller subsystem in the model, and in the Simulink toolstrip click Generate DPI Component in the Generate section.

Alternatively, run the following command to generate DPI:

slbuild("svdpi_pid/Controller");### Searching for referenced models in model 'Controller'. ### Total of 1 models to build. ### Starting build procedure for model: Controller ### Generated code for 'Controller' is up to date because no structural, parameter or code replacement library changes were found. ### Starting SystemVerilog DPI Component Generation ### Successful completion of build procedure for model: Controller Build Summary Top model targets: Model Build Reason Status Build Duration =================================================================================== Controller Compilation artifacts were out of date. Code compiled. 0h 0m 11.588s 1 of 1 models built (0 models already up to date) Build duration: 0h 0m 18.051s

Open the generated package file,

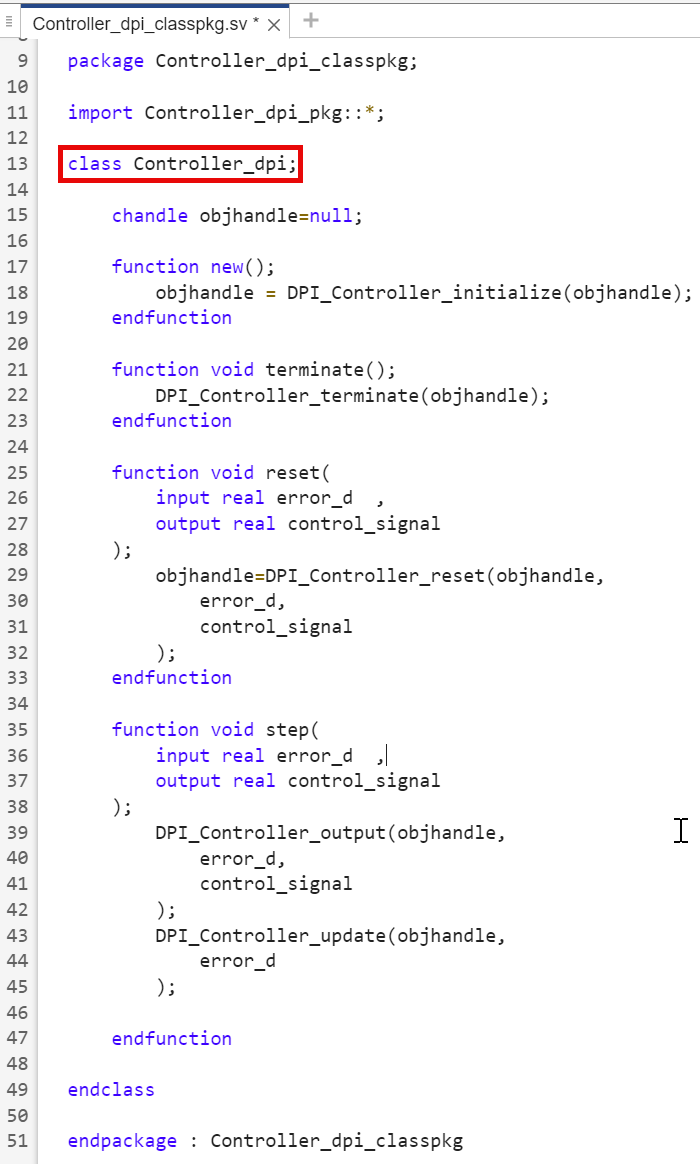

edit("Controller_build/Controller_dpi_classpkg.sv");The file includes a definition for the Controller_dpi class. This class contains the constructor new(), as well as the methods terminate(), reset(), and step().

Verify SystemVerilog Class

To use the class in your code, import the package DUT_dpi_classpkg and instantiate a DUT_dpi object. Then, call the class methods as needed.

Open the testbench file provided with this example.

edit("Controller_dpi_class_tb.sv");The testbench instantiates a Controller_dpi object. Then, every 10 ns, it calls the method step(), and compares the DPI output with the Simulink output. Finally, it calls the method terminate() when the simulation completes.

To simulate the testbench, make sure that Questa™ simulator is on the system path, and then run the following command:

[~, result] = system('vsim -c -do run_class_tb.do')result =

'Reading pref.tcl

# 2024.3_1

# do run_class_tb.do

# QuestaSim-64 vlog 2024.3_1 Compiler 2024.10 Oct 17 2024

# Start time: 10:06:21 on Nov 14,2025

# vlog -sv ./Controller_build/Controller_dpi_pkg.sv ./Controller_build/Controller_dpi_classpkg.sv ./Controller_dpi_class_tb.sv

# -- Compiling package Controller_dpi_pkg

# -- Compiling package Controller_dpi_classpkg

# -- Importing package Controller_dpi_pkg

# -- Compiling package Controller_dpi_class_tb_sv_unit

# -- Importing package Controller_dpi_classpkg

# -- Compiling module Controller_dpi_class_tb

#

# Top level modules:

# Controller_dpi_class_tb

# End time: 10:06:21 on Nov 14,2025, Elapsed time: 0:00:00

# Errors: 0, Warnings: 0

# vsim -sv_lib ./Controller_build/Controller work.Controller_dpi_class_tb

# Start time: 10:06:21 on Nov 14,2025

# ** Note: (vsim-3812) Design is being optimized...

# // Questa Sim-64

# // Version 2024.3_1 linux_x86_64 Oct 17 2024

# //

# // Unpublished work. Copyright 2024 Siemens

# //

# // This material contains trade secrets or otherwise confidential information

# // owned by Siemens Industry Software Inc. or its affiliates (collectively,

# // "SISW"), or its licensors. Access to and use of this information is strictly

# // limited as set forth in the Customer's applicable agreements with SISW.

# //

# // This material may not be copied, distributed, or otherwise disclosed outside

# // of the Customer's facilities without the express written permission of SISW,

# // and may not be used in any way not expressly authorized by SISW.

# //

# Loading sv_std.std

# Loading work.Controller_dpi_pkg(fast)

# Loading work.Controller_dpi_classpkg(fast)

# Loading work.Controller_dpi_class_tb_sv_unit(fast)

# Loading work.Controller_dpi_class_tb(fast)

# Loading ././Controller_build/Controller.so

# Vector compare count = 60001

# **************TEST COMPLETED (PASSED)**************

# ** Note: $finish : ./Controller_dpi_class_tb.sv(55)

# Time: 600030 ns Iteration: 1 Instance: /Controller_dpi_class_tb

# End time: 10:06:24 on Nov 14,2025, Elapsed time: 0:00:03

# Errors: 0, Warnings: 0

'

See Also

slbuild (Simulink)