Generate Native SystemVerilog Assertions from Simulink

This example shows you how to generate native SystemVerilog assertions from assertions in a Simulink® model. This capability is useful whenever you need the same assertion behavior in Simulink and in your HDL testing environment.

Requirements and Prerequisites

Products required for this example:

Siemens® ModelSim™/Questa™ or another supported SystemVerilog simulator

One of the supported C compilers: Microsoft® Visual C++, or GNU GCC

For supported software versions, see Supported EDA Tools and Hardware.

Overview

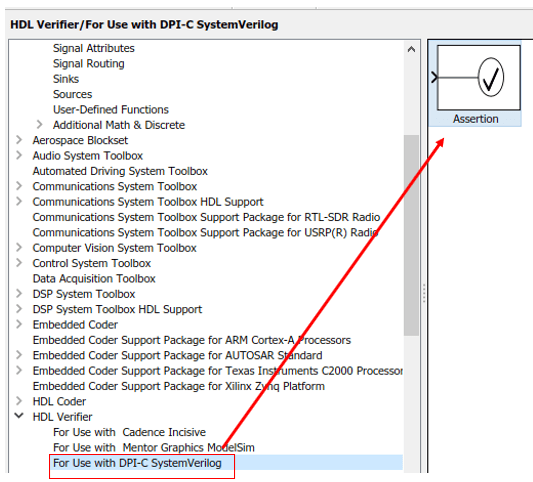

To generate a DPI-C component that contains SystemVerilog assertions, the Simulink model must use the Assertion for DPI-C block. Find this block in the HDL Verifier-> For Use with DPI-C SystemVerilog library as shown below:

This block can be used just like the generic Assertion block in the Model Verification library. The simulation behavior is identical to the Simulink Assertion block, however during DPI-C component generation the block generates a native SystemVerilog assertion for each Assertion for DPI-C block present in the model.

Set Up Example

The model in this example contains two Assertion for DPI-C block. One of them is used to provide information for a delay using the customization option, the second block is set to provide warnings when a second delay is over.

Run the following code to open the design.

open_system('svdpi_assertion');

Set Up Model for Code Generation

The model is preconfigured with one of the DPI-C system target files (systemverilog_dpi_grt.tlc). Before generating the DPI-C component make sure to configure the desired assertion behavior in SystemVerilog via the block mask.

By default the assertion block will generate a SystemVerilog error ($error("")) with an empty message when triggered. This can be changed either by providing an error message, changing the error to a warning ($warning("")) with a warning message, or providing your own custom SystemVerilog command to be executed.

The picture below shows the SystemVerilog behavior configuration for the assertion block after the first delay. The parameters outside of the DPI-C assertion options group only affect Simulink simulation behavior.

Notice that the Assertion custom command is a valid SystemVerilog statement.

The second assertion block is configured to output a warning with a specified message as shown below.

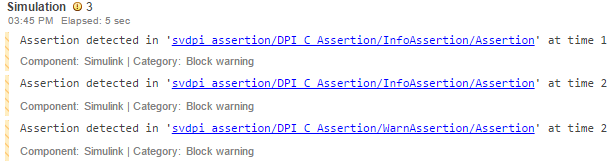

If we run the model we can see that two assertion warnings are triggered in Simulink:

Generate SystemVerilog DPI-C Component

Build the component to generate C code for the DPI_C_Assertion subsystem, and a SystemVerilog DPI-C wrapper and package file named "DPI_C_Assertion_build/DPI_C_Assertion_dpi.sv" and "DPI_C_Assertion_build/DPI_C_Assertion_dpi_pkg.sv".

To generate the DPI component, execute the following in the MATLAB command prompt:

slbuild('svdpi_assertion/DPI_C_Assertion');

Run Generated Testbench in HDL Simulator

For this example ModelsSim/QuestaSim simulator will be used. To get more detailed instructions on how to run the testbench please refer to "Getting Started with SystemVerilog DPI Component Generation".

After running the testbench notice the messages and the warnings that are being thrown by the DPI-C component.

Tracing a SystemVerilog Assertion Back to Simulink

If you want to trace the assertion that generated the warning back to Simulink you need to find the Simulink Identifier (SID) from the warning message as shown below:

Once you find the SID for the assertion block you can use Simulink programmatic API's to highlight the corresponding block. Execute:

Simulink.ID.hilite('svdpi_assertion:7');

This will highlight the relevant block.

Filtering an Assertion in the HDL Simulator

If you want to filter an assertion in the HDL Simulator, you need to supply the SID of the block you want to filter as a plusargs argument to the HDL Simulator.

For instance the SID of the "InfoAssertion" assertion block is "svdpi_assertion:6". So in order to filter the informative messages given by this block we need to supply the argument "+svdpi_assertion:6" to the HDL Simulator. When executing ModelSim/QuestaSim on Linux®, enter this command in the MATLAB prompt:

vsim -c -voptargs=+acc -sv_lib ../DPI_C_Assertion work.DPI_C_Assertion_dpi_tb +svdpi_assertion:6

Windows® users, enter this command:

vsim -c -voptargs=+acc -sv_lib ../DPI_C_Assertion_win64 work.DPI_C_Assertion_dpi_tb +svdpi_assertion:6