Post-Layout Verification of Serial Link Projects

Post-layout verification allows you to verify the performance of your actual routed system against the design guidelines or specification rules. You can edit the vias and stackups and control the padstack models. You can also verify your design using PCB models. You can create topologies from extracted PCB data for pre-layout analysis.

Note

You need a RF PCB Toolbox™ license for the post-layout workflow.

Apps

| Serial Link Designer | Analyze PCB designs for serial link applications (Since R2021b) |

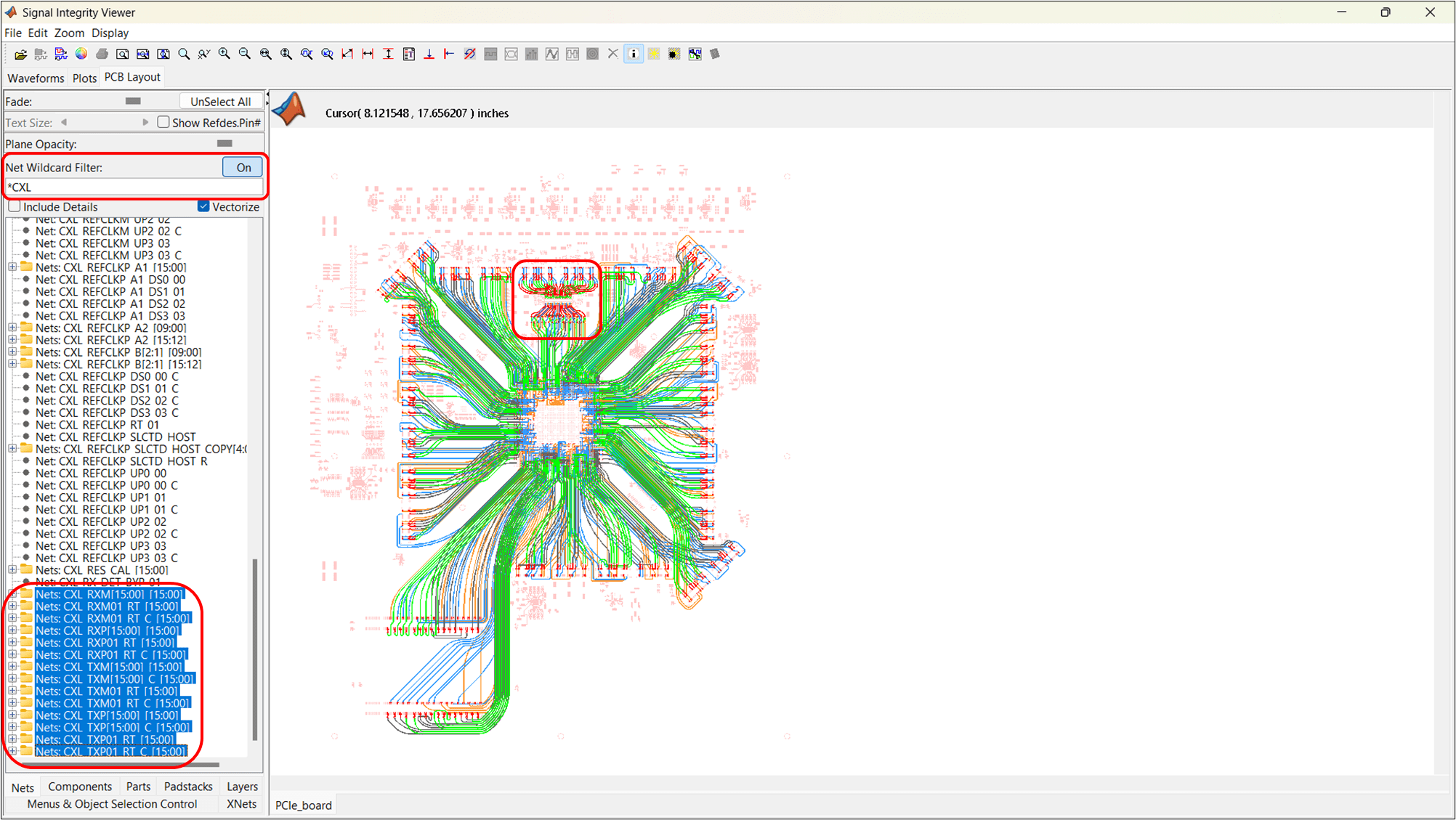

| Signal Integrity Viewer | View the signal integrity results of Serial Link Designer or Parallel Link Designer apps (Since R2021b) |

Topics

- Post-Layout Verification of Serial Link

Verify system-level SI and timing margins of PCB design databases.

- Post-Layout Verification Workflow

Set up stimulus patterns, SPICE options, and select the nets for simulation during post-layout verification.

- Stackup and Extraction Control in Serial Link Project

Edit stackups and control padstack models.

- Via and Stackup Management in Serial Link Project

Manage vias and stackups using Stackup Editor and PadStack Editor.

- Post-Layout to Pre-Layout Extraction

Create topologies from extracted PCB data.