Specify Corner Conditions in Parallel Link Design

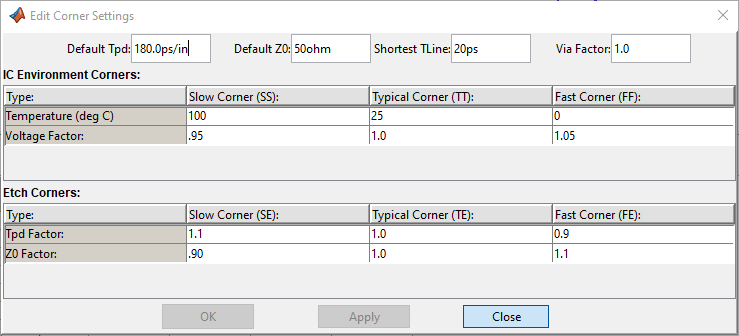

Corner conditions are used to define the process corners. In the process corners, the parameters are within the specified range for that parameter but outside the range of normal operations. You can specify corner conditions using the Edit Corners Settings dialog box from Setup > Corner Conditions.

The corner conditions settings include default characteristic impedance (Z0) in ohms, default propagation delay (Tpd) in ps/in, and the length of the shortest transmission line to simulate (TLine) in ps. You can also specify the factor by which to scale the impedance of all the vias using the Via Factor parameter.

IC Environment Corners

The IC Environment Corners area contains the temperature parameter for each corner. This app uses it as the .TEMP parameter in the SPICE simulations. The temperature parameter does not affect IBIS buffer models.

The voltage factors are used to scale all voltage sources in the netlist. The typical corner value is scaled by the scaling factor to create the values for the slow and fast corners. For voltage sources, the value entered in the schematic or specified for a voltage net in the post-layout is scaled by the scaling factor.

I/O buffer voltages can use the three values specified in the IBIS [Voltage

Range] parameter for the three corners or use the typical value from the

[Voltage Range] and scale it.

Etch Corners

You can use the Etch Corners area to specify scaling factors for the Z0 and Tpd parameters of transmission line models. Scaling factors account for manufacturing variation in the PCB. Both ideal and lossy transmission line models are scaled.

Lossy transmission line models are scaled by computing the values of Z0 and Tpd from the typical corner L and C values. The computed Z0 and Tpd are then scaled by the scaling factors to create the Z0 and Tpd values for the slow and fast corners. The slow and fast corner L and C are computed from the slow and fast Z0 and Tpd. For more information, see Model Lossy Transmission Lines in Parallel Link Designer.

Impact of Corner Settings

The elements that are affected by corner settings are:

I/O buffer voltages: If scaling is enabled for I/O buffer voltages, the typical value of the IBIS [Voltage Range] parameter is multiplied by the scaling factor for the IC corner selected.

I/O buffer data: The data that is used for each process corner is summarized in Process Corner Model Data Usage.

Voltage sources on schematics: The voltage parameter of the element is multiplied by the scaling factor for the IC corner selected.

Voltage nets in post-layout: The voltage set on the net on import of the board is multiplied by the scaling factor for the IC corner selected.

Ideal transmission lines (SPICE T elements): The Z0 and Tpd parameters are multiplied by the Z0 and Tpd factors for the selected corner.

Lossy transmission lines (SPICE W elements): The models without explicit slow and fast corner models in the library are scaled using the Z0 and Tpd factors in Corner Conditions. Models that have

_te(typical),_fe(fast) or_se(slow) appended to the model name are used for the appropriate etch corner if they exist.SPICE subcircuits: file and subcircuit names can contain {etch} and {corner}. If present, the current corner is substituted.

Process Corner Model Data Usage

| IC Process Corner | Model or Setting | Data Used |

|---|---|---|

| FF | IBIS buffer in HSPICE | typ=fast HSPICE option |

| IBIS buffer in IsSPICE4 | IBIS maximum IV and VT data | |

| HSPICE buffer | HSPICE FF wrapper | |

| Temperature | FF Temperature from Corner Conditions | |

| TT | IBIS buffer in HSPICE | typ=typ HSPICE option |

| IBIS buffer in IsSPICE4 | IBIS typical IV and VT data | |

| HSPICE buffer | HSPICE TT wrapper | |

| Temperature | TT Temperature from Corner Conditions | |

| SS | IBIS buffer in HSPICE | typ=slow HSPICE option |

| IBIS buffer in IsSPICE4 | IBIS minimum IV and VT data | |

| HSPICE buffer | HSPICE SS wrapper | |

| Temperature | SS Temperature from Corner Conditions |