Bitwise Operator

对输入执行指定的按位运算

库:

Simulink /

Logic and Bit Operations

HDL Coder /

Logic and Bit Operations

描述

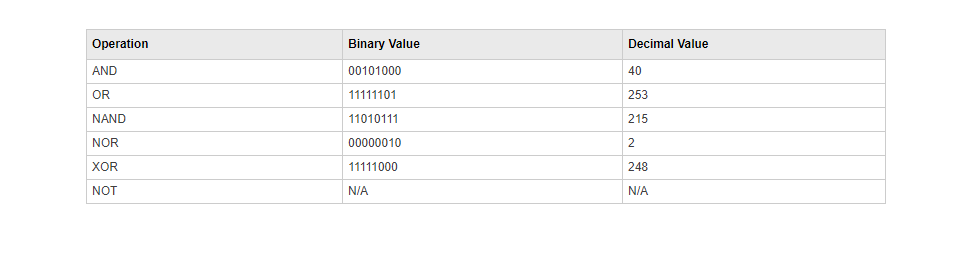

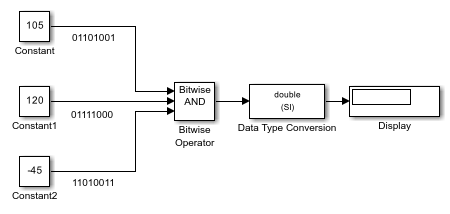

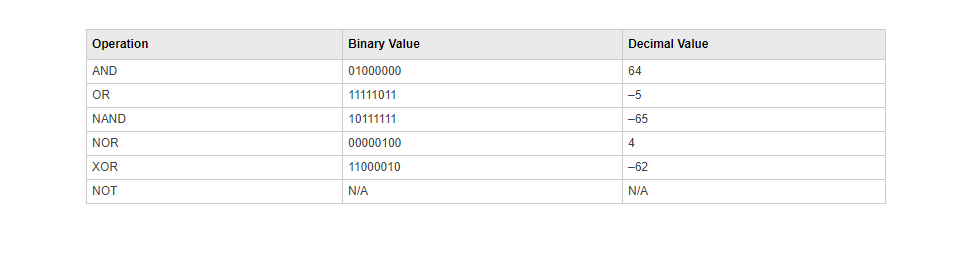

Bitwise Operator 模块执行您为一个或多个操作数指定的按位运算。与 Logical Operator 模块的逻辑运算不同的是,按位运算将操作数视为位向量,而不是单个值。

对模块运算的限制

Bitwise Operator 模块不支持移位运算。对于移位运算,请使用 Shift Arithmetic 模块。

当配置为多输入 XOR 门时,此模块将按照 IEEE® 逻辑元素标准的规定执行模 2 加法。

示例

端口

输入

输出

参数

扩展功能

版本历史记录

在 R2006a 之前推出

另请参阅

Logical Operator | Compare To Constant | Compare To Zero | Shift Arithmetic

主题

- WWV Digital Receiver - Synchronization and Detection (DSP System Toolbox)