设计错误检测中的派生范围

当您为模型中的信号或数据指定最小值和最大值时,这些值定义了设计范围。

在设计错误检测期间,软件会分析模型行为并计算仿真期间可能出现的值:

模块输出端口

Stateflow® 本地数据

这些值的范围称为派生范围。

如果启用“配置参数”对话框中 Design Verifier 窗格中的使用指定的输入最小值和最大值参数,则它会告诉分析在计算派生范围时将模型输入端口上的设计范围视为约束。默认情况下,使用指定的输入最小值和最大值参数是启用的。

如果禁用使用指定的输入最小值和最大值,软件在计算派生范围时不会限制信号。

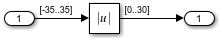

要了解此过程的工作原理,请考虑以下模型。

在此模型中,设计范围包括:

Inport 模块:[-35..35]

Abs 模块输出:[0..30]

要运行分析,请执行以下操作:

在 Design Verifier 选项卡的模式部分中,选择设计错误检测。

点击检测设计错误。

鉴于 Inport 模块的设计范围,Abs 模块输出的唯一可能值是从 0 到 35 的值。因此,Abs 模块的派生范围是 [0..35]。有关派生范围输出的更多信息,请参阅 查看结果。

但是,如果禁用使用指定的输入最小值和最大值参数,分析将根据模型输入端口的不受限制的值计算派生范围。在前面的模型中,Abs 模块的唯一有效输出是非负数。因此,Abs 模块的派生范围是 [0..Inf]。