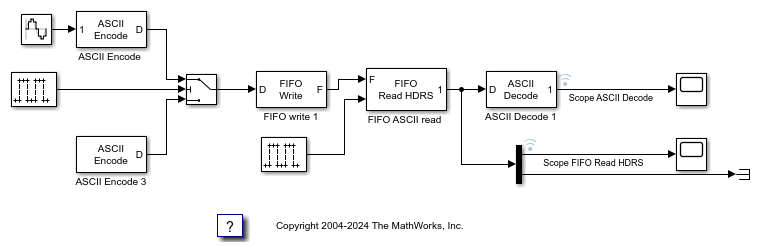

ASCII 编码/解码重新同步环回测试

该示例模型展示了 FIFO Read HDRS 模块在多次禁用后重新同步的能力,以及其处理错误的能力 - 例如当尝试读取时消息仅部分完成的情况。

Switch 模块在连续采样时间间隔中,在消息的首尾部分之间交替切换。这模拟了最坏的情况:模型在消息构建完成之前就进行了更新。因此,有时只能收到部分信息。第二个脉冲发生器交替启用和禁用 FIFO Read HDRS 模块。

范围 1 绘制了每个时间步接收到的解码正弦波数据。当脉冲发生器 1 模块输出 0 时,FIFO Read HDRS 模块的计数值为 0。当输出为 1 时,读取操作通过丢弃多余数据来同步进度,并返回 FIFO 中发现的最后一个完整值。范围 2 表示存在新数据时。

开放模型

model = 'slrt_ex_serialasciisplit';

open_system(model);

配置模型并进行仿真

set_param(model,'StopTime','30'); sim(model)

关闭模型

bdclose(model);