Frame Buffer with HDMI Template

The Frame Buffer with High-Definition Multimedia Interface (HDMI) template creates a Simulink® project with models to simulate and generate a video application with external memory frame buffer. This template forms the base for the Histogram Equalization Using Video Frame Buffer example. Use this template to simulate the full reference design of a video processing application on an FPGA with HDMI I/O and connection to an external memory frame buffer for advanced image processing designs.

Required Products

Vision HDL Toolbox™

Computer Vision Toolbox™

SoC Blockset™ Support Package for AMD FPGA and SoC Devices

Template Structure

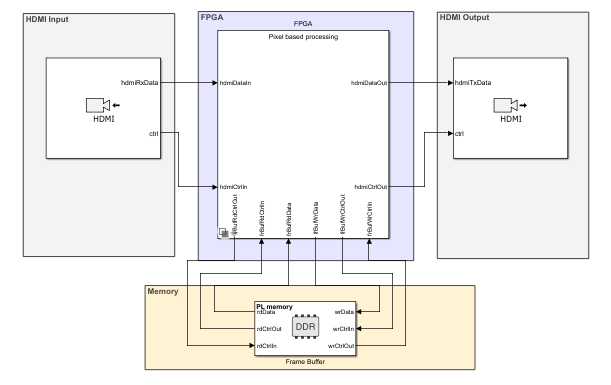

HDMI video streams video data from an HDMI Rx block into the FPGA. The

FPGA implements a color-space transformation and your image processing algorithm. The

processed images then undergo the inverse color-space transformation and stream to the

HDMI Tx block. The FPGA algorithm is connected to the external memory

frame buffer Memory Channel

block configured in

AXI4-Stream Video Frame Buffer mode.

The FPGA pixel model uses Video Stream Connector blocks to connect different subsystems and to connect to HDMI I/O blocks. This is required to be able to generate each subsystem as a separate IP in the implemented reference design from the model. Since the FPGA frame model is for simulation purposes only and is not used for implementation, the Video Stream Connector blocks are not modeled.

Modify Project

In MATLAB®, on the Project Shortcuts tab, click Open

FPGA pixel model. Double-click to open the FPGA Algorithm

Wrapper.

![]()

The FPGA Algorithm, highlighted in green, contains feedthrough ports

and signals.

![]()

Modify the content of the FPGA Algorithm subsystem to incorporate

your desired vision processing algorithm, with complete simulation and code generation

of the surrounding video memory system. The pixelToFrameBuf and

pixelFromFrameBuf ports provide access to the external memory

channel, Frame Buffer. For pure algorithm design and investigation,

in the Project Shortcuts tab, click Open FPGA frame

model, and repeat this step.

See Also

Use Template to Create SoC Model | Create New Project Using Templates