SM AC9C

Discrete- or continuous-time synchronous machine AC9C excitation system including an automatic voltage regulator and an exciter

Since R2023a

Libraries:

Simscape /

Electrical /

Control /

SM Control

Description

The SM AC9C block implements a synchronous machine (SM) AC9C excitation system model in conformance with IEEE Std 421.5-2016 [1].

Use this block to model the control and regulation of the field voltage of a synchronous machine that operates as a generator using an AC rotating exciter.

Switch between continuous and discrete implementations of the block by using the

Sample time (-1 for inherited) parameter. To configure the

integrator for continuous time, set the Sample time (-1 for

inherited) parameter to 0. To configure the integrator

for discrete time, set the Sample time (-1 for inherited) parameter

to a positive scalar. To inherit the sample time from an upstream block, set the

Sample time (-1 for inherited) parameter to

-1.

The SM AC9C block comprises five major components:

The Current Compensator component modifies the measured terminal voltage as a function of the terminal current.

The Voltage Measurement Transducer component simulates the dynamics of a terminal voltage transducer using a low-pass filter.

The Excitation Control Elements component compares the voltage transducer output with a terminal voltage reference to produce a voltage error value. The component then passes this value through a voltage regulator to produce the exciter field voltage.

The AC Rotating Exciter component models the AC rotating exciter, which produces a field voltage that is applied to the controlled synchronous machine. The block also feeds the exciter field current (VFE) back to the excitation system.

The Power Source component models the dependency of the power source for the controlled rectifier from the terminal voltage.

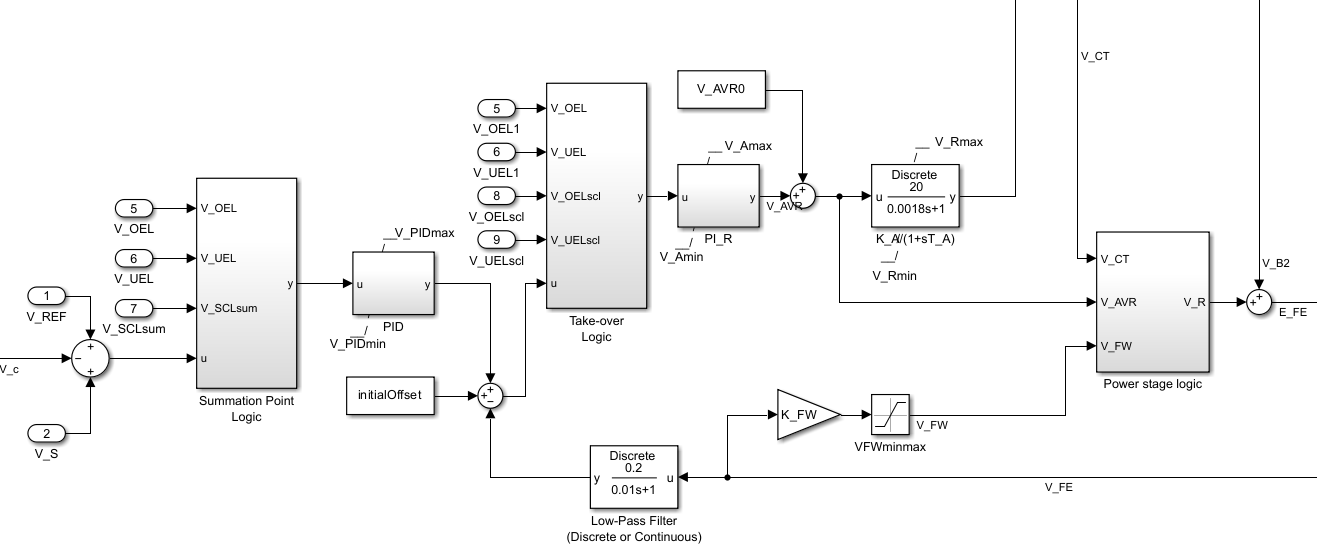

This diagram shows the structure of the AC9C excitation system model:

In the diagram:

VT and IT are the measured terminal voltage and current of the synchronous machine, respectively.

VC1 is the current-compensated terminal voltage.

VC is the filtered, current-compensated terminal voltage.

VREF is the reference terminal voltage.

VS is the power system stabilizer voltage.

SW1 is the power source switch that you specify for the controlled rectifier.

VB is the exciter field voltage.

EFE and VFE are the exciter field voltage and current, respectively.

EFD and IFD are the field voltage and current, respectively.

Current Compensator and Voltage Measurement Transducer

The block models the current compensator by using this equation:

where:

RC is the load compensation resistance.

XC is the load compensation reactance.

The block implements the voltage measurement transducer as a Low-Pass Filter block with the time constant TR. Refer to the documentation for the Low-Pass Filter block for information about the exact discrete and continuous implementations.

Excitation Control Elements

This diagram shows the structure of the excitation control elements:

In the diagram:

The Summation Point Logic subsystem models the summation point input location for the overexcitation limiter (OEL), underexcitation limiter (UEL), and stator current limiter (SCL). For more information about using limiters with this block, see Field Current Limiters.

The PID subsystem models a PID controller that functions as a control structure for the automatic voltage regulator. The minimum and maximum anti windup saturation limits for the block are VPIDmin and VPIDmax, respectively.

The Take-over Logic subsystem models the take-over point input location for the OEL, UEL, SCL and PSS voltages. For more information about using limiters with this block, see Field Current Limiters.

The PI_R subsystem models a PI controller that functions as a control structure for the field current regulator. The minimum and maximum anti windup saturation limits for the block are VAmin and VAmax, respectively.

The top Low-Pass Filter block models the major dynamics of the controlled rectified bridge. KA is the controlled rectifier bridge equivalent gain and TA is the major time constant of the controlled rectifier bridge. The minimum and maximum anti windup saturation limits for the block are VRmin and VRmax, respectively.

The bottom Low-Pass Filter block models the rate feedback path for the stabilization of the excitation system. KF and TF are the gain and time constants of this system, respectively. See the documentation for the Low-Pass Filter block for information about the discrete and continuous implementations.

The Power state logic subsystem supports the selection of the power stage type, which can be a thyristor or a chopper converter. If you set the Power stage type selector, S_CT parameter to

Thyristor bridge, it represents a thyristor converter. If you set the Power stage type selector, S_CT parameter toChopper converter, it represents a chopper converter. The subsystem sums the voltage regulator command signal VR to the exciter field voltage VB. For more information about the logical switch for the power source of the controlled rectifier and about the power state logic subsystem, see Power Source and Power State Logic.The initialOffset Constant block ensures the simulation can start from a steady state. The SM AC9C block calculates this value by using saturation and exciter parameters, including the initial field voltage and the exciter field current feedback gain.

Field Current Limiters

You can use different types of field current limiter to modify the output of the voltage regulator under unsafe operating conditions:

Use an overexcitation limiter to prevent overheating of the field winding due to excessive field current demand.

Use an underexcitation limiter to boost field excitation when it is too low, which risks desynchronization.

Use a stator current limiter to prevent overheating of the stator windings due to excessive current.

Attach the output of any of these limiters at one of these points:

Summation point — Use the limiter as part of the automatic voltage regulator (AVR) feedback loop.

Take-over point — Override the usual behavior of the AVR.

If you are using the stator current limiter at the summation point, use the input VSCLsum. If you are using the stator current limiter at the take-over point, use the overexcitation input VOELscl, and the underexcitation input VUELscl.

AC Rotating Exciter

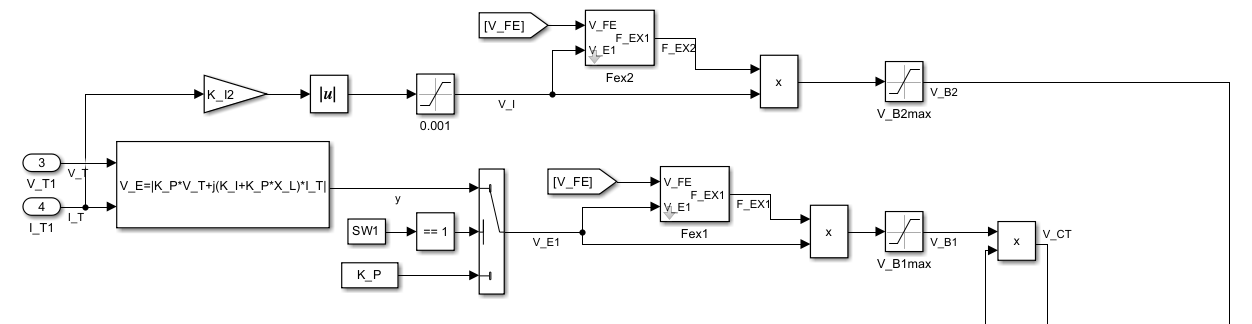

This diagram shows the structure of the AC rotating exciter:

In the diagram:

The exciter field current VFE is the sum of three signals:

The nonlinear function Vx models the saturation of the exciter output voltage.

The proportional term KE models the linear relationship between the exciter output voltage and the exciter field current.

The subsystem models the demagnetizing effect of the load current on the exciter output voltage using the demagnetization constant KD in the feedback loop.

The Integrator with variable limits subsystem integrates the difference between EFE and VFE to generate the exciter alternator output voltage VE. TE is the time constant for this process.

The nonlinear function FEX models the exciter output voltage drop from the rectifier regulation. This function depends on the constant KC, which itself is a function of commutating reactance.

The parameters VEmin and VFEmax model the lower and upper limits of the rotating exciter.

Power Source and Power State Logic

You can use different power source representations for the controlled rectifier by setting

the Power source selector SW1 parameter value. To derive the

power source for the controlled rectifier from the terminal voltage, set the

Power source selector SW1 parameter to

Position A: power source derived from terminal

voltage. To specify that the power source is independent of the

terminal voltage, set the Power source selector SW1 parameter

to Position B: power source independent from the terminal

conditions.

The Power state logic subsystem supports the selection of the power stage type, which can

be a thyristor or a chopper converter. If you set the Power stage type

selector, S_CT parameter to Thyristor

bridge, the Power state logic subsystem represents a thyristor

converter. If you set the Power stage type selector, S_CT

parameter to Chopper converter, the Power state logic

subsystem represents a chopper converter. The value of the voltage regulator command

signal VR depends on the Voltage

limit, V_lim1 (pu) and Voltage limit, V_lim2

(pu) parameters and on the

VCT,

VFW, and

VAVR signals according to this logic:

if S_CT ~= 0 % Thyristor bridge V_R = V_CT else % Chopper converter if V_AVR > V_lim1 V_R = C_T else if V_AVR > V_lim2 V_R = 0 else V_R = -V_FW end end end

Ports

Input

Output

Parameters

References

[1] “IEEE Recommended Practice for Excitation System Models for Power System Stability Studies.” IEEE Std 421.5-2016 (Revision of IEEE Std 421.5-2005), August 2016, 1–207. https://doi.org/10.1109/IEEESTD.2016.7553421.

Extended Capabilities

Version History

Introduced in R2023a